Method for measuring heat conduction parameter in thin layer material of active area of semiconductor device

A thin-layer material and semiconductor technology, which is applied in the field of semiconductor device testing, can solve the problems of low measurement accuracy, limitation, and inability to measure the heat conduction speed in the thin layer, and achieve the effect of improving the detection sensitivity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

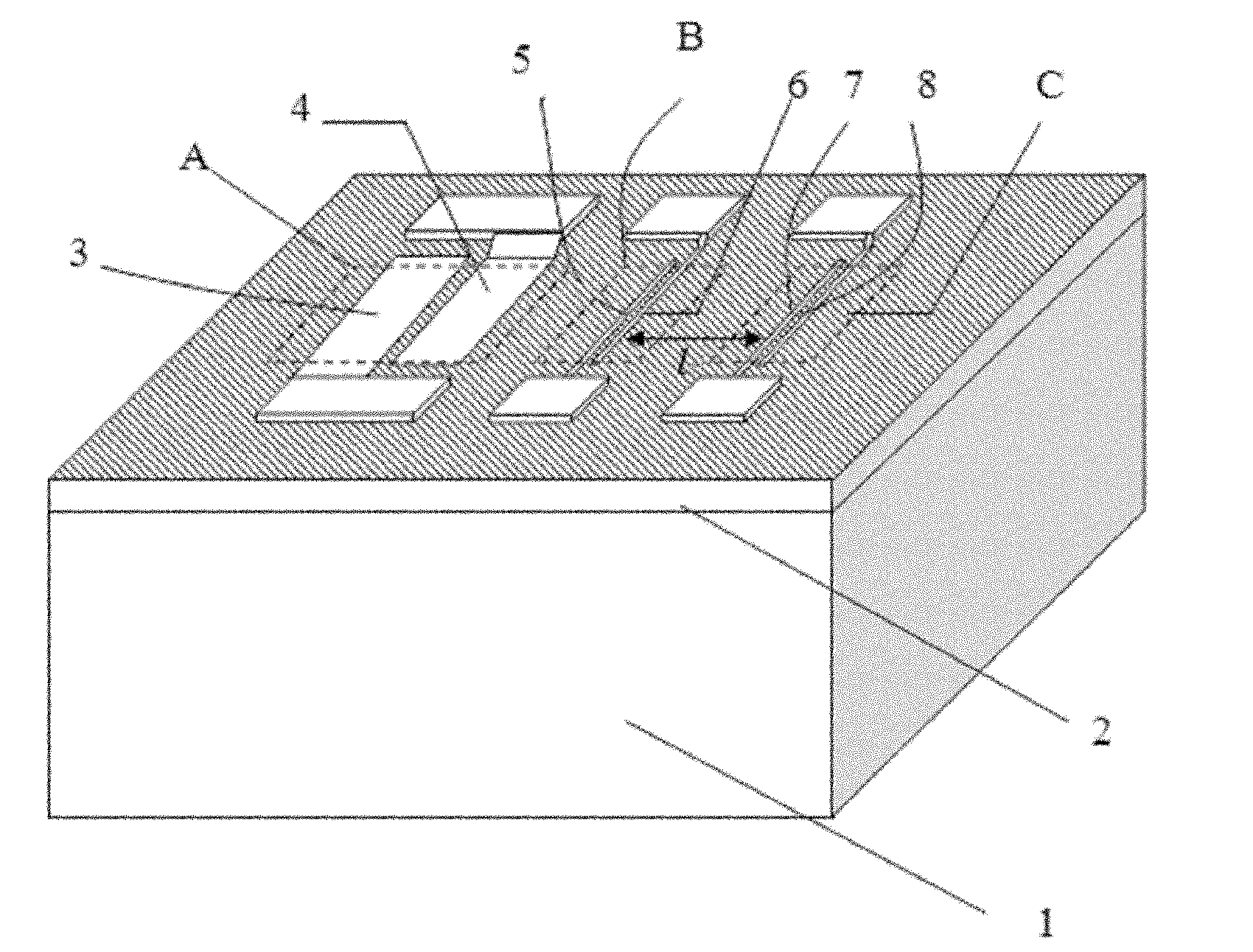

[0019] See figure 1 As shown, a 1.5 micron gallium nitride (GaN) active region thin layer 2 is epitaxially grown on a 400 micron thick silicon carbide (SiC) substrate layer 1 by means of epitaxy. Since the heat source region is used to apply electric power to generate heat, its power The stronger the load capacity, the more conducive to improving the test accuracy. Therefore, the area of the first ohmic contact electrode and the second ohmic contact electrode is required to be larger. The first ohmic contact electrode 3 with a length of 10 microns and a width of 100 microns is prepared by the ohmic contact process. and the third ohmic contact electrode 4 to form a heat source region, using the Schottky junction preparation process to prepare the first Schottky contact electrode 5 and the second Schottky contact electrode 7 with a length of 0.5 microns and a width of 100 microns respectively, The third ohmic contact electrode 6 and the fourth ohmic contact electrode 8 with a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com