Semiconductor plastic-sealed body and layered scanning method

A layered scanning, semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of slow grinding speed, slow speed, incompatibility, etc., to avoid the effect of slow speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

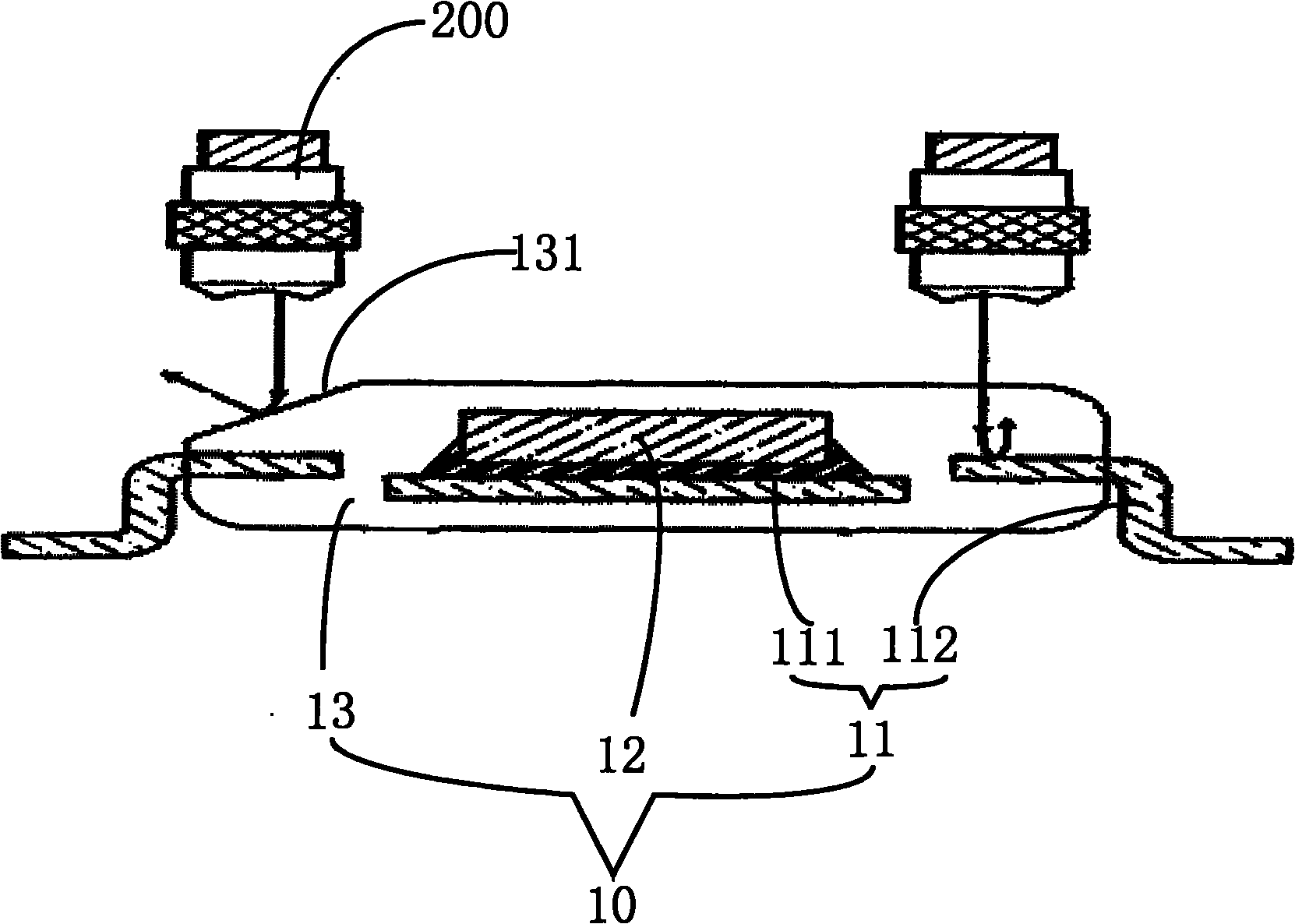

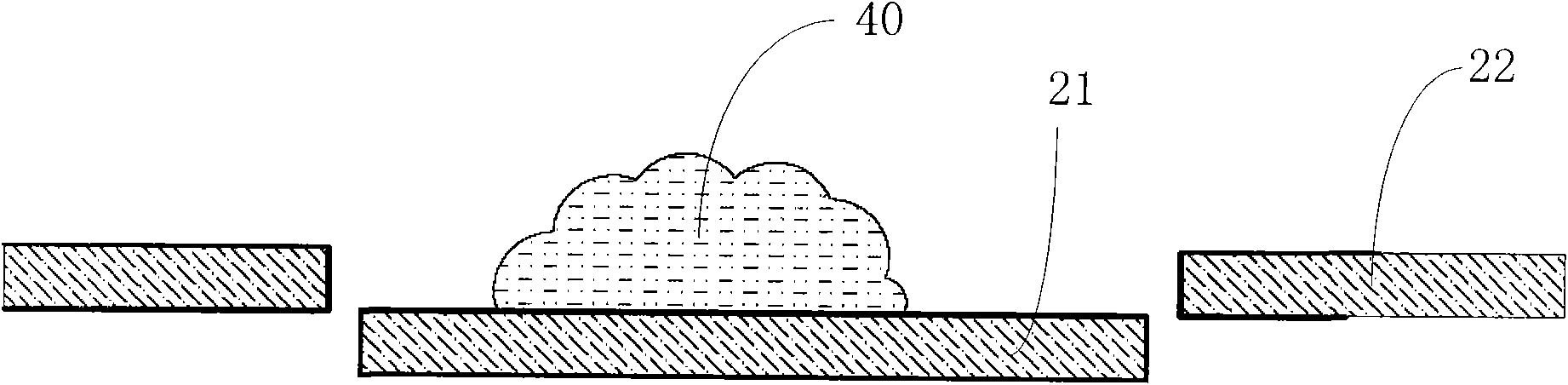

[0026] Please refer to figure 2 , the layered scanning method of the present invention is used for figure 1 The semiconductor plastic packaged device 10 to be inspected is scanned in layers to detect the layering of the interface between different media inside the semiconductor device 10 .

[0027] The semiconductor device 10 includes an inner lead frame 11, a chip 12 fixed on the inner lead frame 11 and an inner plastic package 13 that encapsulates the inner lead frame 11 and the chip 12, the inner lead The frame 11 has a carrier table 111 for fixing the chip 12 and a plurality of pins 112 protruding from the inner plastic package 13 , and the surface of the inner plastic package 13 is formed with a slope 131 .

[0028] The layered scanning method of the present invention utilizes at least one scanner 200 to scan the semiconductor device 10...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com