Method for forming groove

A trench and wafer technology, used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as uneven surface, semiconductor device damage, and deep trench etching, avoiding over-etching problems, The effect of reducing damage and improving quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

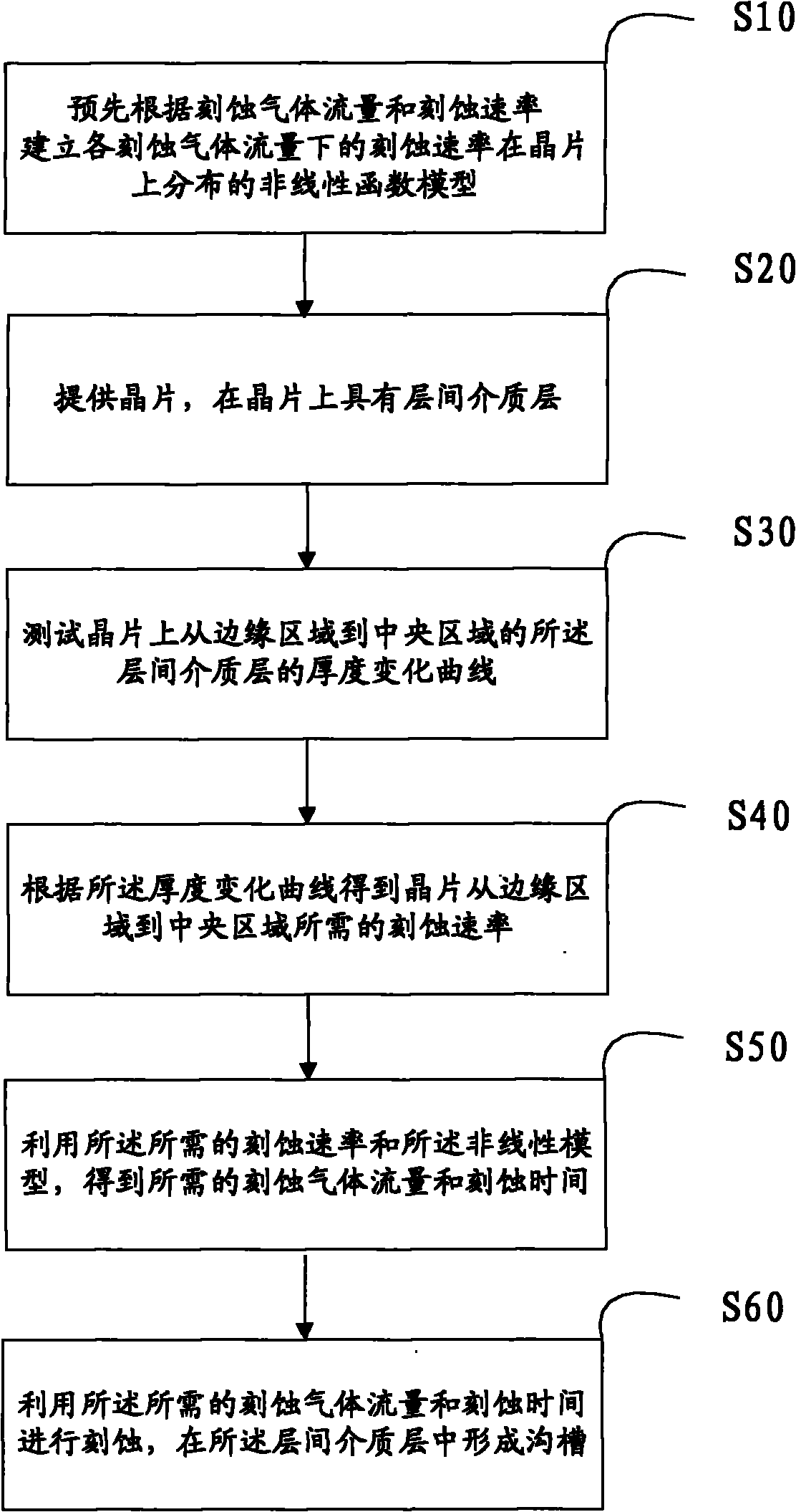

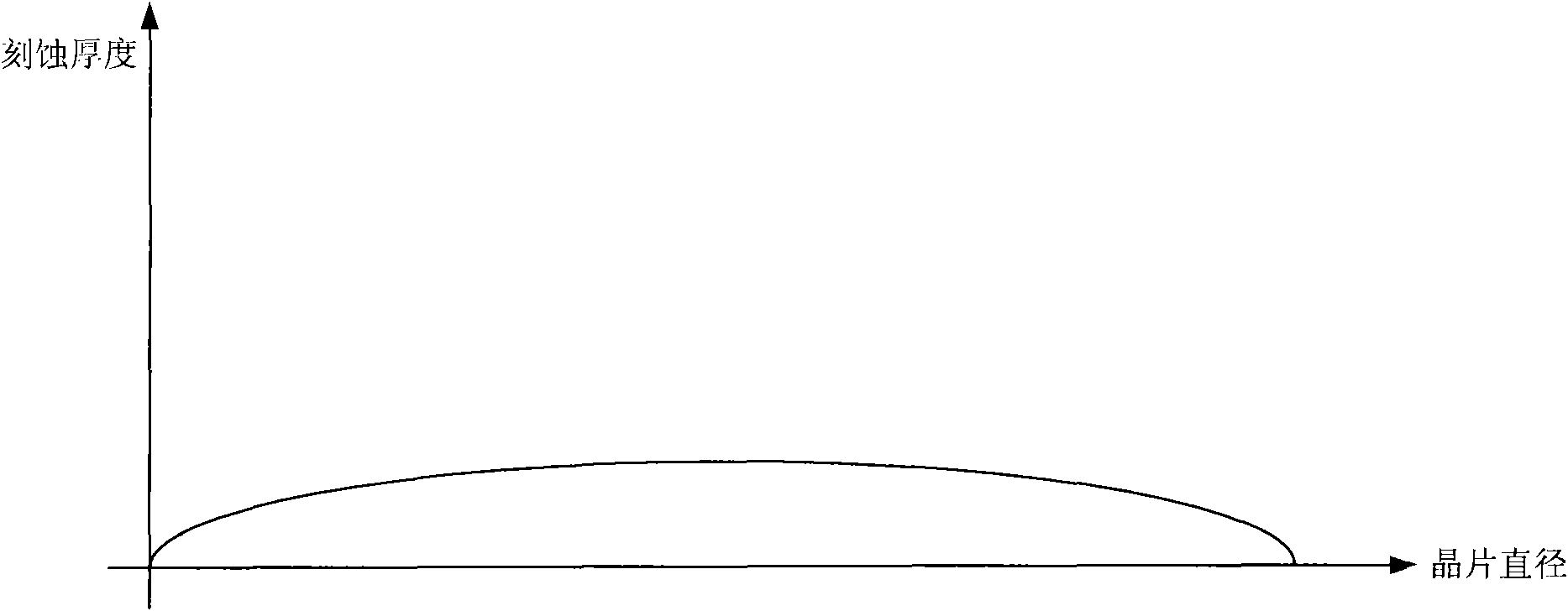

[0027] It can be seen from the background technology that since the thickness of the interlayer dielectric layer in the edge region of the wafer is different from the thickness of the interlayer dielectric layer in the central region of the wafer, the depths of the grooves in the edge region of the wafer formed by etching are different from those in the central region of the wafer. It is easy to etch the trenches in the edge region of the wafer too deeply, thereby causing damage to the underlying semiconductor devices.

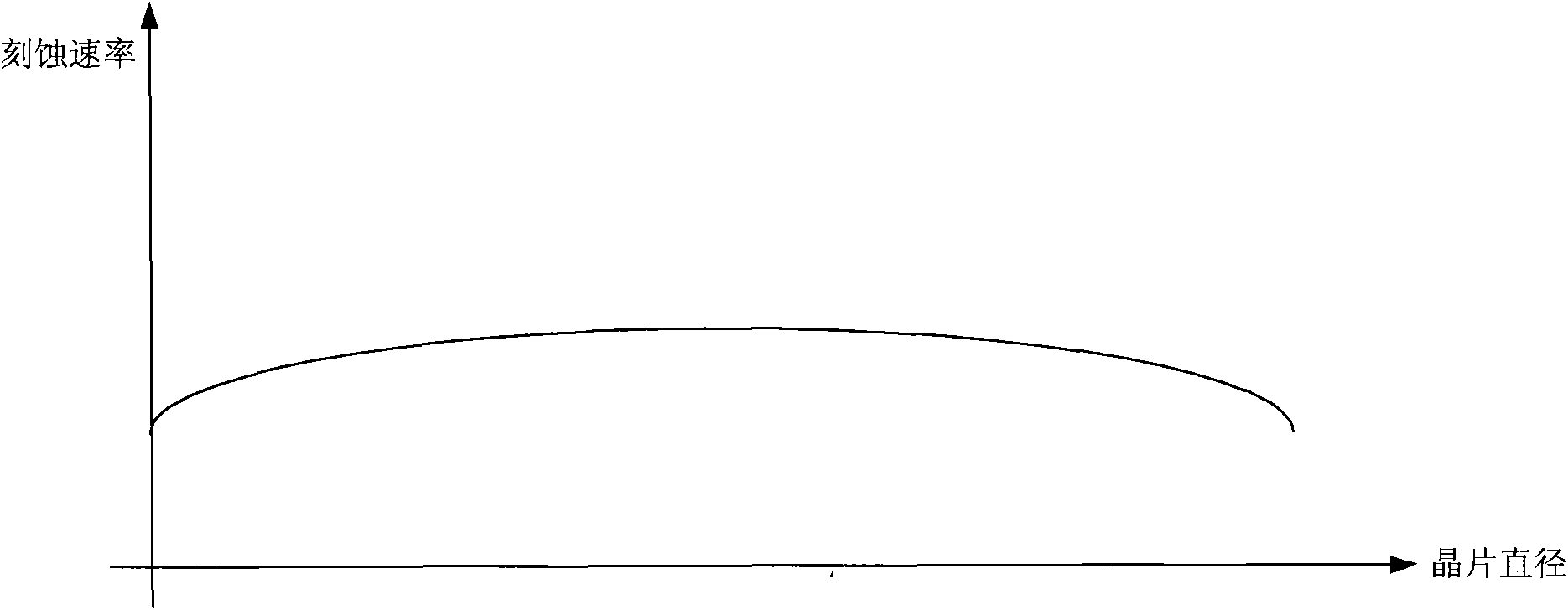

[0028] The inventor of the present invention thinks through a large number of experiments: because the etching gas is not evenly distributed in the etching chamber, usually the distribution of the etching gas flow in the center of the etching chamber and the edge of the etching chamber is different, so that the flow rate of the wafer edge region The etching rate of the interlayer dielectric layer and the interlayer dielectric layer in the wafer central region i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com