Method for debugging 8051 core-based system on chip (SOC) on line

A system-on-chip, monitor-51 technology, applied in the detection of faulty computer hardware, etc., can solve problems such as complex structure, and achieve the effect of solving mismatch, saving time and manpower, and being simple and convenient.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

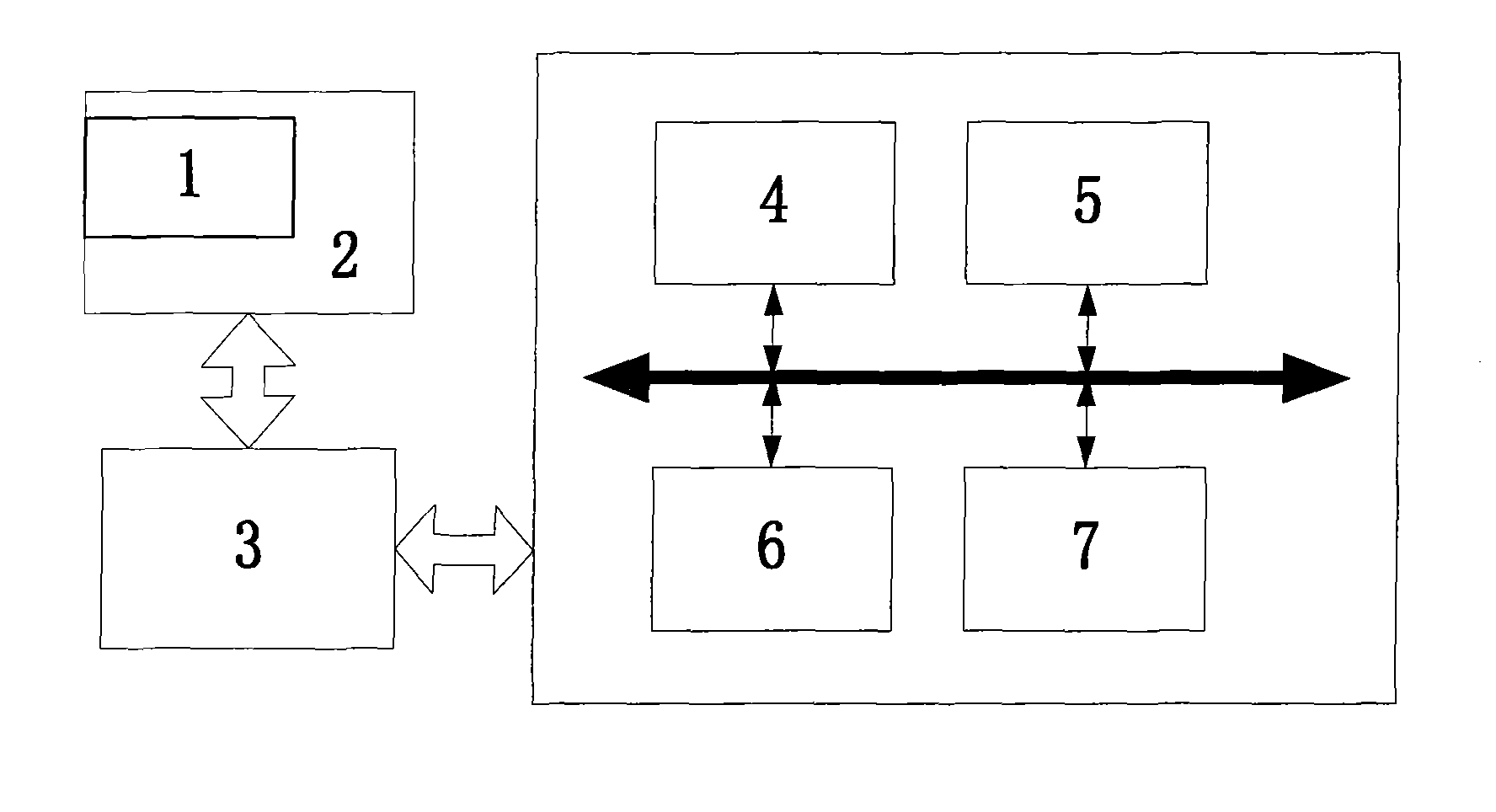

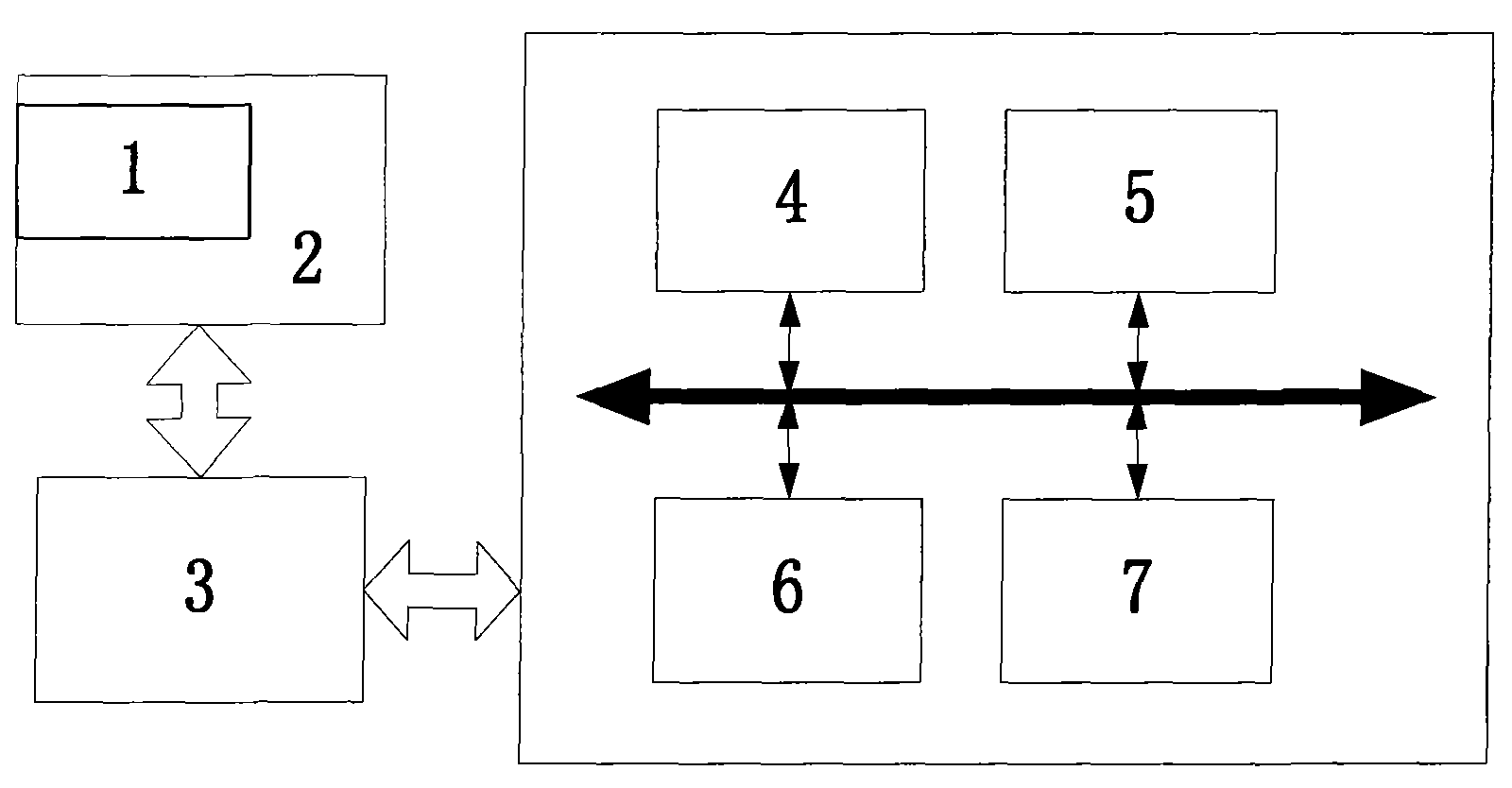

[0028] A kind of online debugging method based on 8051 core system on chip, such as figure 1 As shown, the system-on-chip with 8051 core processor is used as an application platform, and the system includes an upper computer (PC) 2, 232 level conversion circuits 3 and a system-on-chip, and the system-on-chip includes an 8051-core processor 5, a memory 6, a clock Reset circuit 4 and asynchronous serial communication module 7, clock reset circuit 4 provides clock and reset signal for system-on-chip; 8051 core processor 5 is connected with memory 6, clock reset circuit 4 and respectively by data line, address line and read-write control lead wire The asynchronous serial communication module 7 is connected; The upper computer (PC) 2 is connected to the 232 level conversion circuit 3 through the computer serial interface and the serial data line, and the level conversion is carried out through the 232 level conversion circuit 3, and its output The terminal is connected to the seria...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com