Conductive layer under SOI oxygen buried layer and manufacturing process thereof

A manufacturing process and conductive layer technology, applied in the field of microelectronics, can solve the problems that the buried oxide layer cannot be effectively released and restrict the performance of SOI materials, etc., and achieve the effect of reducing the self-heating effect and alleviating the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

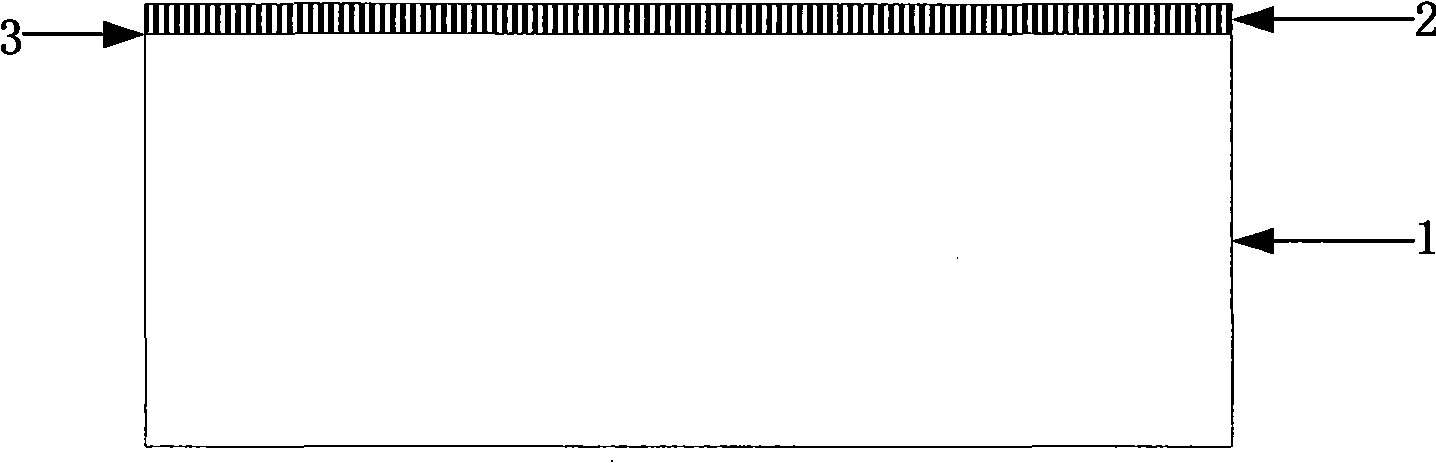

[0038] This embodiment provides a conductive layer under the SOI buried oxide layer, such as Figures 1 to 4 As shown, wherein, the SOI includes a bottom silicon film 1, a buried oxide layer 4, and a top silicon film 5 grown from bottom to top; the conductive layer is grown between the bottom silicon film 1 and the buried oxide layer 4; the conductive The layers comprise a charge guiding layer 2 and a blocking layer 3 grown on the upper and lower surfaces of said charge guiding layer 2 . The charge guiding layer 2 is a conductive metal layer with a melting point higher than 1000°C and difficult to diffuse in an environment of 900°C. The material of the charge guiding layer 2 is copper; the material of the blocking layer 3 is tantalum nitride, and the thickness of the blocking layer 3 is 70, 72, 75, 78 or 80 angstroms.

Embodiment 2

[0040] The difference between this embodiment and the first embodiment is that the charge guiding layer 2 is a non-metallic good conductor layer.

Embodiment 3

[0042] This embodiment provides a manufacturing process of the conductive layer under the SOI buried oxide layer described in Embodiment 1, the process is as follows Figures 1 to 8 shown, including the following steps:

[0043] 1. Deposit a layer of tantalum nitride barrier layer (about 75 angstroms) on the first bulk silicon wafer, and then deposit a layer of metal copper, the thickness of which is 1 / 2 of the thickness of the target metal conductive layer;

[0044] 2. Form a silicon dioxide layer by thermal oxidation on the second bulk silicon wafer, then deposit a layer of tantalum nitride barrier layer (about 75 Angstroms), and finally deposit a layer of metal copper, the thickness of which is the target metal conductive layer 1 / 2 of the thickness;

[0045] 3. Bond the first bulk silicon wafer and the second bulk silicon wafer by metal bonding technology;

[0046] 4. Use hydrogen injection stripping technology to thin the silicon material on the back of the second silico...

PUM

| Property | Measurement | Unit |

|---|---|---|

| melting point | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com