Multi-core processor

A processor and multi-core technology, applied in the combination of various digital computers, etc., can solve the problems of limited expansion capability and limited chip power consumption, etc., and achieve the effect of easy expansion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

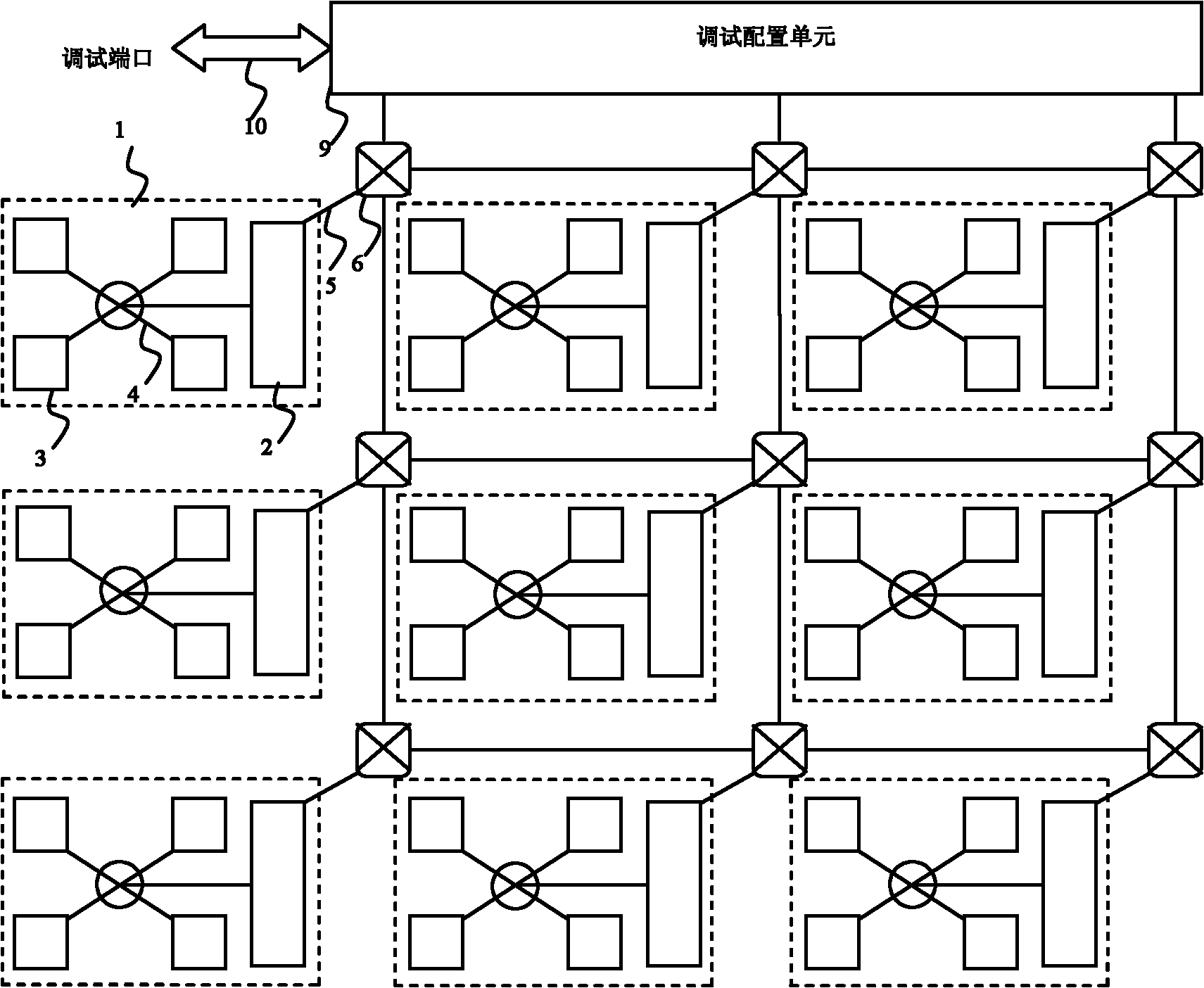

[0034] figure 1 It includes multiple processor sets 1. The processor set includes a master processor 2 and a number of slave processors 3. The master processor and the slave processor and the slave processor and the slave processor are connected by a local bus 4. The processor sets and the processor sets and the debugging configuration unit are connected by the global bus 5 and the switching unit (SWITCH) 6. Some peripherals or hardware acceleration units may be integrated on the multi-core processor. figure 1 Not shown in, these peripherals or hardware acceleration units can also be connected to the debug configuration unit and the processor assembly through the global bus 5.

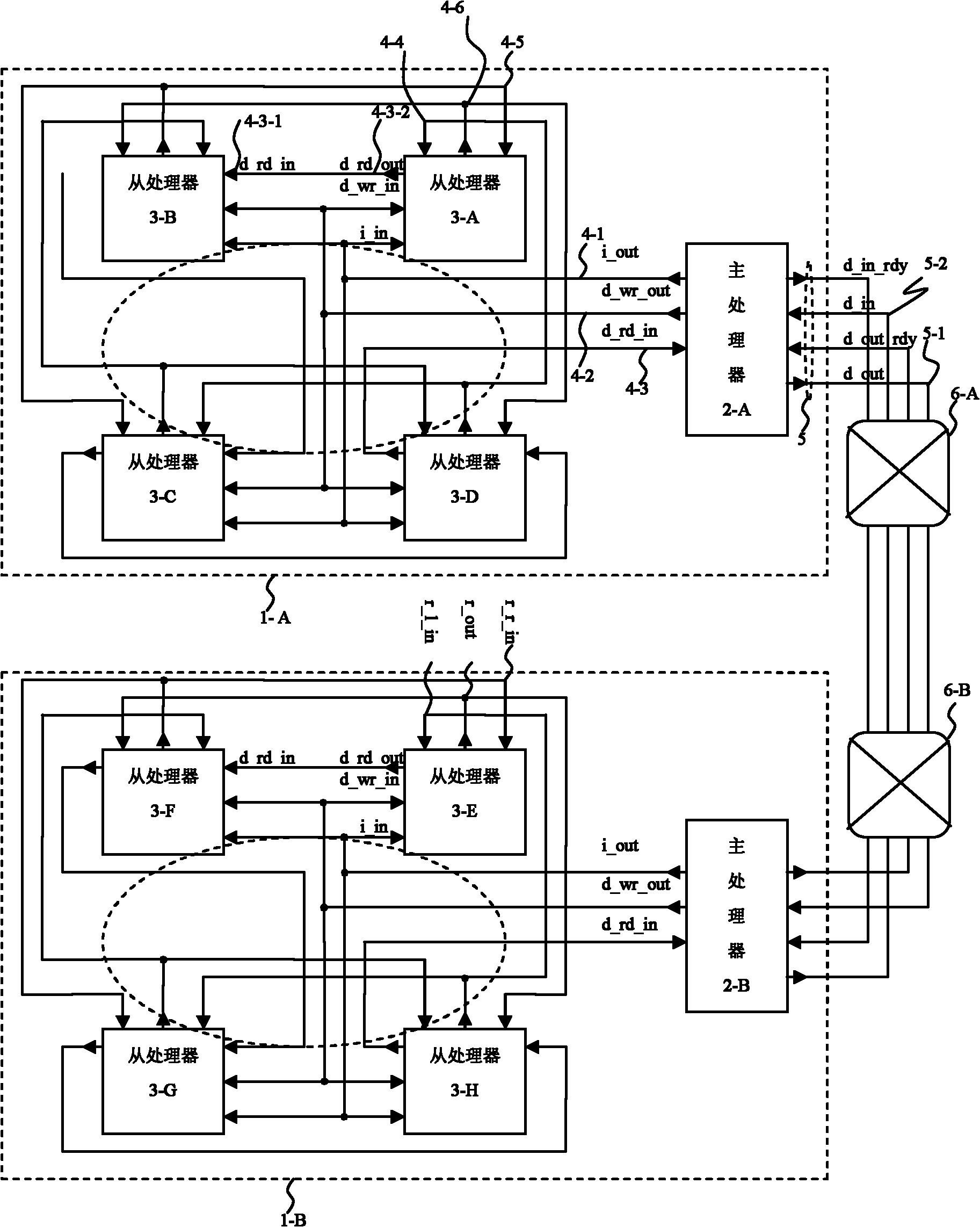

[0035] The master processor 2 controls the instructions and data executed by the slave processor 3. The slave processor may have no program memory and instruction fetching unit. The master processor sends an ultra-long instruction word to the slave processor 3 via the instruction bus in the local bus 4. Th...

Embodiment 2

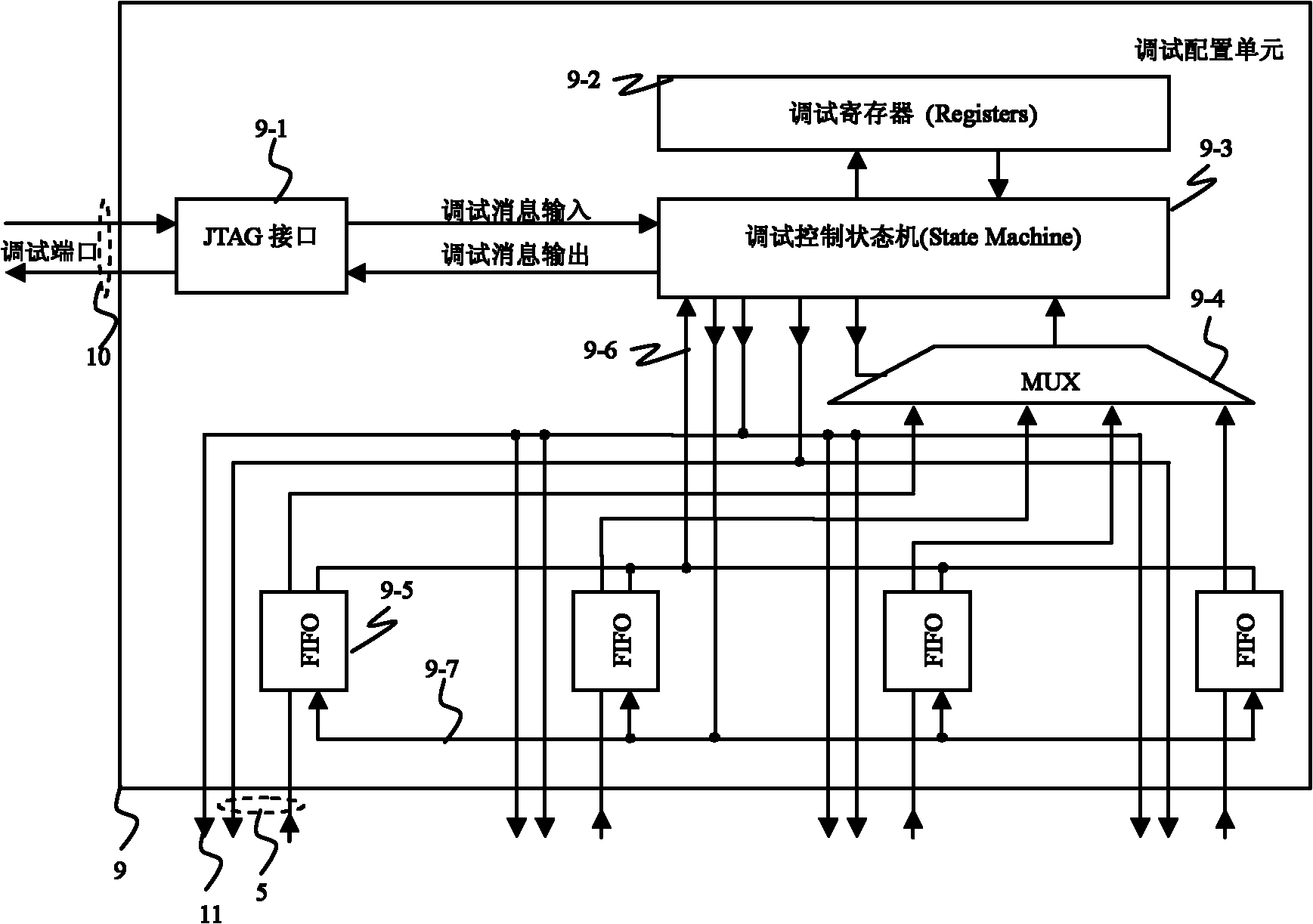

[0056] figure 1 The mid-global bus 5 can not only transmit multipoint-to-multipoint data communication between the processor sets, but also transmit configuration, debugging, and tracking control information between the debugging configuration unit and the processor sets. The multi-core processor system can work in two modes, debug mode and non-debug mode. Regardless of whether it is in debug mode or non-debug mode, before the multi-core processor starts to run code, the debug configuration unit 9 is responsible for configuring the program memory of the main processor in all the processor sets on the entire multi-core processor, that is, placing the need in the processor set The code executed in is loaded into the program memory of the main processor. At the same time, the debug configuration unit may also need to initialize the register files, data memory or other special registers of the master processor and the slave processor in the processor set.

[0057] After the multi-co...

Embodiment 3

[0071] according to figure 2 The bus setting mode shown in includes a global bus 5, a global bus switching unit 6 and a local bus 4. All slave processors 3-A,..., 3-D in a processor set 1-A work together under the control and coordination of the master processor 2-A to complete the task of single instruction multiple data or multiple instruction multiple data At the same time, different processor sets can handle different tasks. In order to increase the processing capacity of the multi-core processor, or to increase the number of slave processors in each processor set, the number of processor sets can also be increased. The increase in the number of slave processors in the processor set does not change the structure of the bus and the bus input and output ports of the master and slave processors. Increasing the number of processor sets does not change the structure of the global bus and the global bus switching unit, so the processor capability of the multi-core processor of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com