Stacked multi-encapsulation structure device, semiconductor encapsulation structure and manufacturing method thereof

A manufacturing method, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of not being able to reduce the risk of solder overflow, not having openings, and not being able to reduce the possibility of short circuits between lines, etc. problem, achieve the effect of reducing the risk of solder overflow, reducing the possibility, and avoiding the deviation of package structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

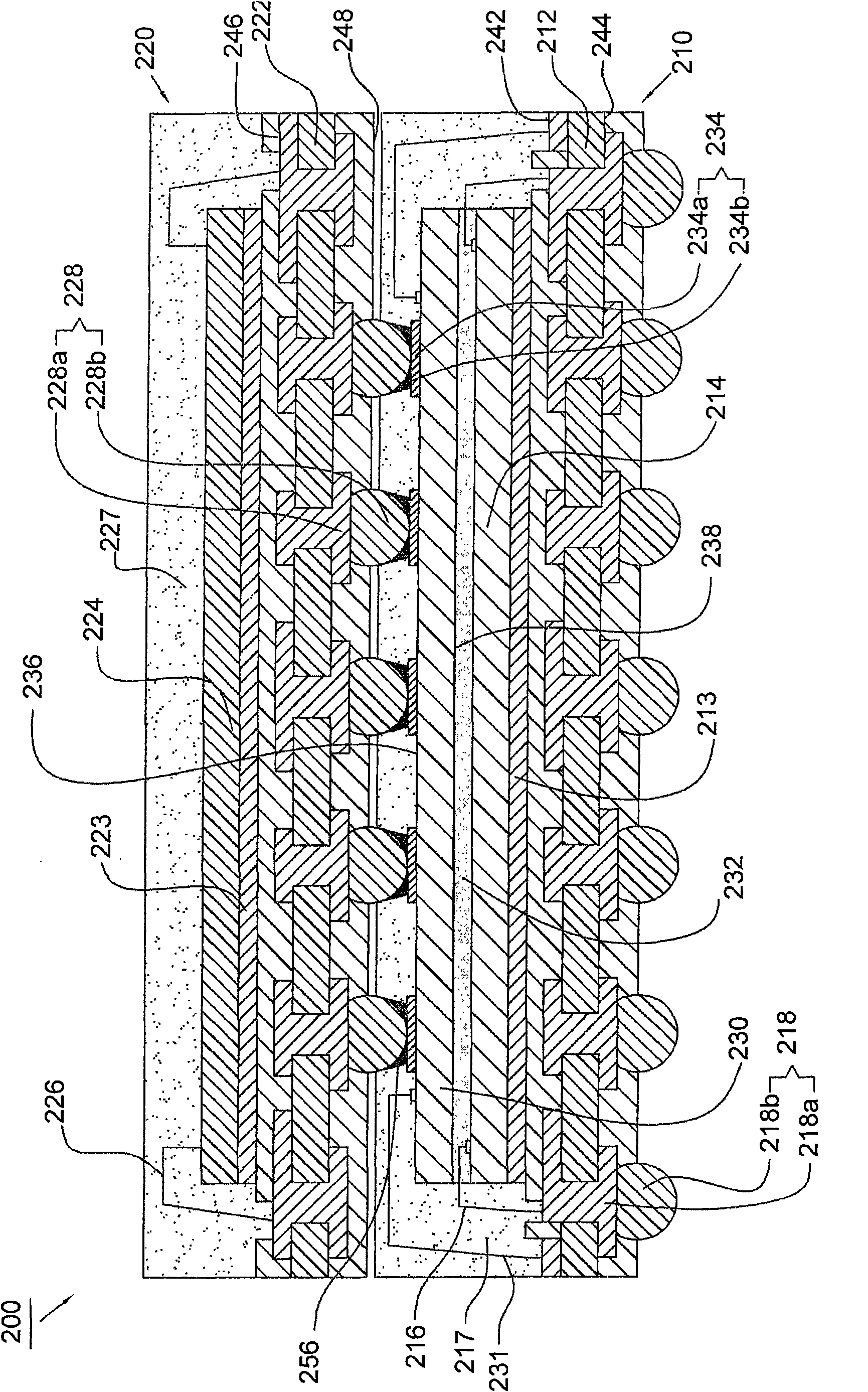

[0069] refer to image 3 , which shows a stacked multi-package construction device (Package On Package; POP) 200 according to the first embodiment of the present invention. The stacked multi-package structure device 200 includes a lower package structure 210 and an upper package structure 220 .

[0070] The lower packaging structure 210 includes a first chip 214 fixed and electrically connected to an upper surface 242 of a first substrate 212 . The first substrate 212 has an upper metal layer and a lower metal layer, which can be patterned to provide appropriate circuitry, and are electrically connected to each other through plated through holes. An interposer 230 can be fixed on the first chip 214 via glue 232 and electrically connected to the upper surface 242 of the first substrate 212 . The intermediary substrate 230 can be a circuit board or a substrate. The intermediary substrate 230 has an upper surface 236 and a lower surface 238 , the lower surface 238 is opposite t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com