BCD device and manufacturing method thereof

A device and the same technology, applied in the field of semiconductor power devices, can solve problems such as high on-resistance, increase in on-resistance, and reduce surface field, and achieve the goal of increasing conductive channels, reducing paths, and reducing on-resistance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

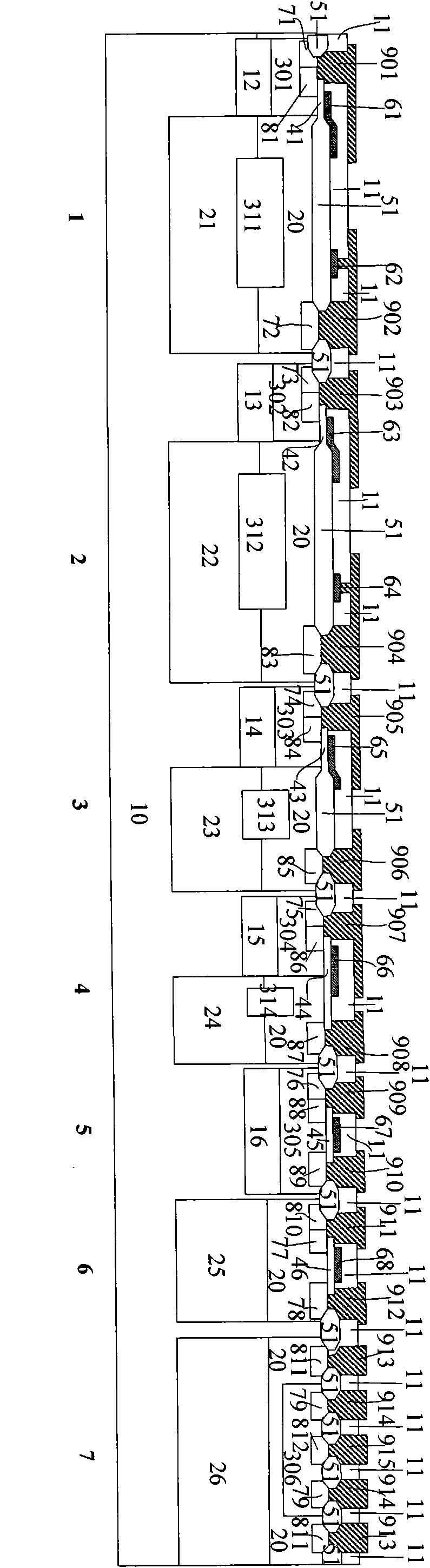

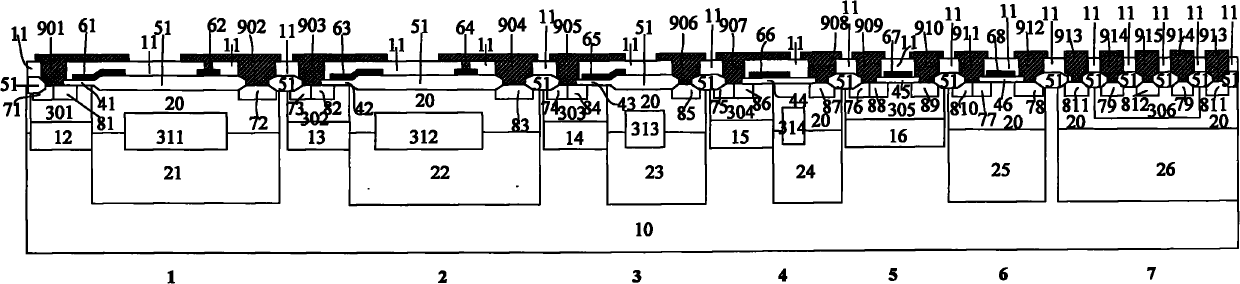

[0026] A BCD semiconductor device such as figure 1 As shown, including high-voltage nLIGBT device 1 integrated on the same chip, the first type of high-voltage nLDMOS device 2, the second type of high-voltage nLDMOS device 3, the third type of high-voltage nLDMOS device 4, low-voltage NMOS device 5, low-voltage PMOS device 6 and low-voltage NPN device7.

[0027] The high-voltage nLIGBT device 1 is directly made in the p-type substrate 10, and the p-type field drop layer 311 is located under the field oxide layer 51 and surrounded by the n-type drift region well 21 and the n-type epitaxial layer 20; p + The anode region 72 is under the anode metal 902 and surrounded by the n-type epitaxial layer 20; n + Cathode region 81 and p + The well contact region 71 is located side by side under the cathode metal 901 and is surrounded by the p-type body region 301; the p-type buried layer 12 is located between the p-type body region 301 and the p-type substrate 10; the polysilicon gate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com