AMBA interface circuit

A technology of interface circuit and main equipment, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of bus access delay, waste of resources, etc., to reduce waiting time and memory access delay, avoid data packet loss, and save resources Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

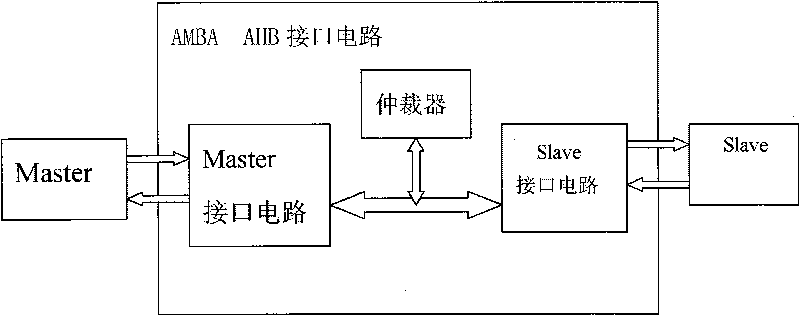

[0027] Such as figure 1 As shown, a kind of AMBA interface circuit of the present invention comprises Master interface circuit, Slave interface circuit and bus arbiter thereof, and Master interface circuit is connected with main equipment Master, and Slave interface circuit is connected with slave equipment Slave, is connected by bus arbiter Arbitration determines the right to use the bus, and then performs data exchange between the master device and the slave device.

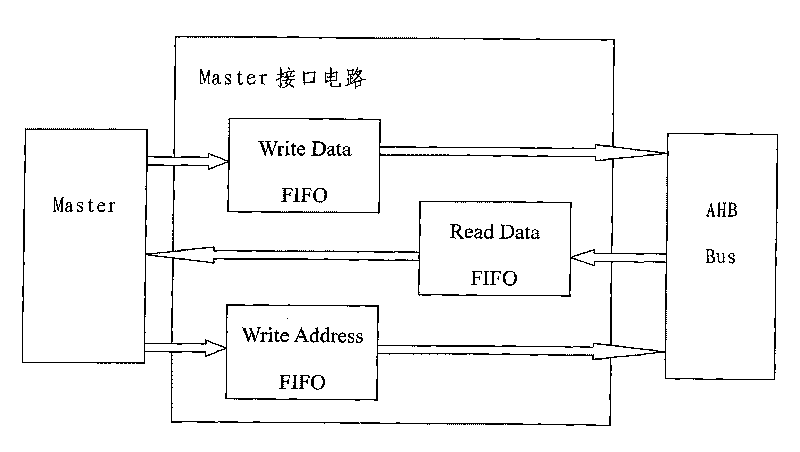

[0028] Such as figure 2 As shown, the present invention is characterized in that the Master interface circuit has built-in 3 first-in first-out data registers FIFO, wherein:

[0029] Write Data FIFO is used to receive data transmitted from the master device. When the master device has not obtained the right to use the bus, it can write the data into the Write Data FIFO first, and then transmit the data after obtaining the right to use the bus;

[0030] Write Address FIFO is used to receive the address transm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com