Time-domain parallel digital demodulation system

A digital demodulation and time-domain technology, applied in the field of digital information transmission, can solve problems such as high technological conditions, inability to meet general demodulation requirements, and huge investment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

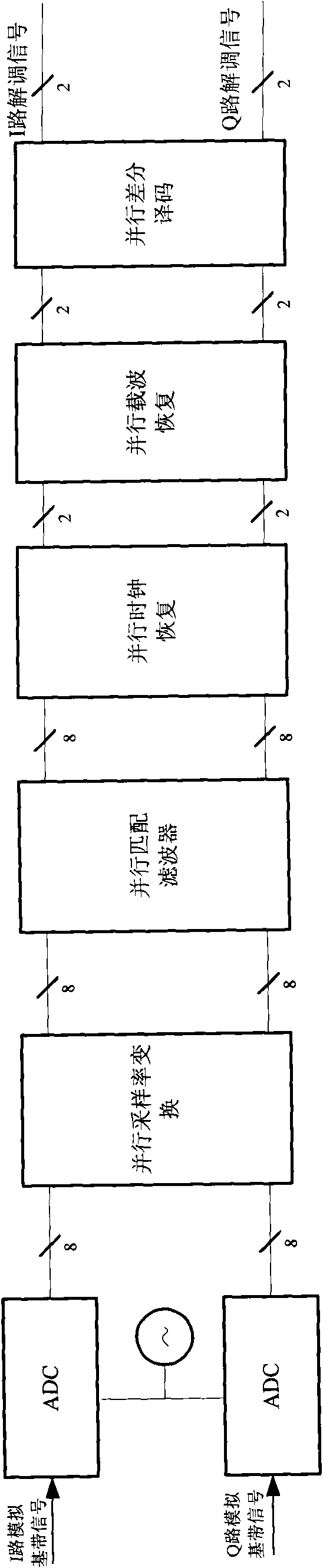

[0080] In this implementation case, the implementation of the demodulation method of the system of the present invention will be described by taking 8-channel parallel QPSK 4 times symbol rate digital demodulation as an example. figure 1 Shown is the system structure diagram of 8-way parallel demodulation, including: parallel sampling rate conversion module, parallel matched filter, parallel clock recovery loop, parallel carrier recovery loop, parallel differential decoder; the above modules are in accordance with figure 1 Connect in sequence as shown.

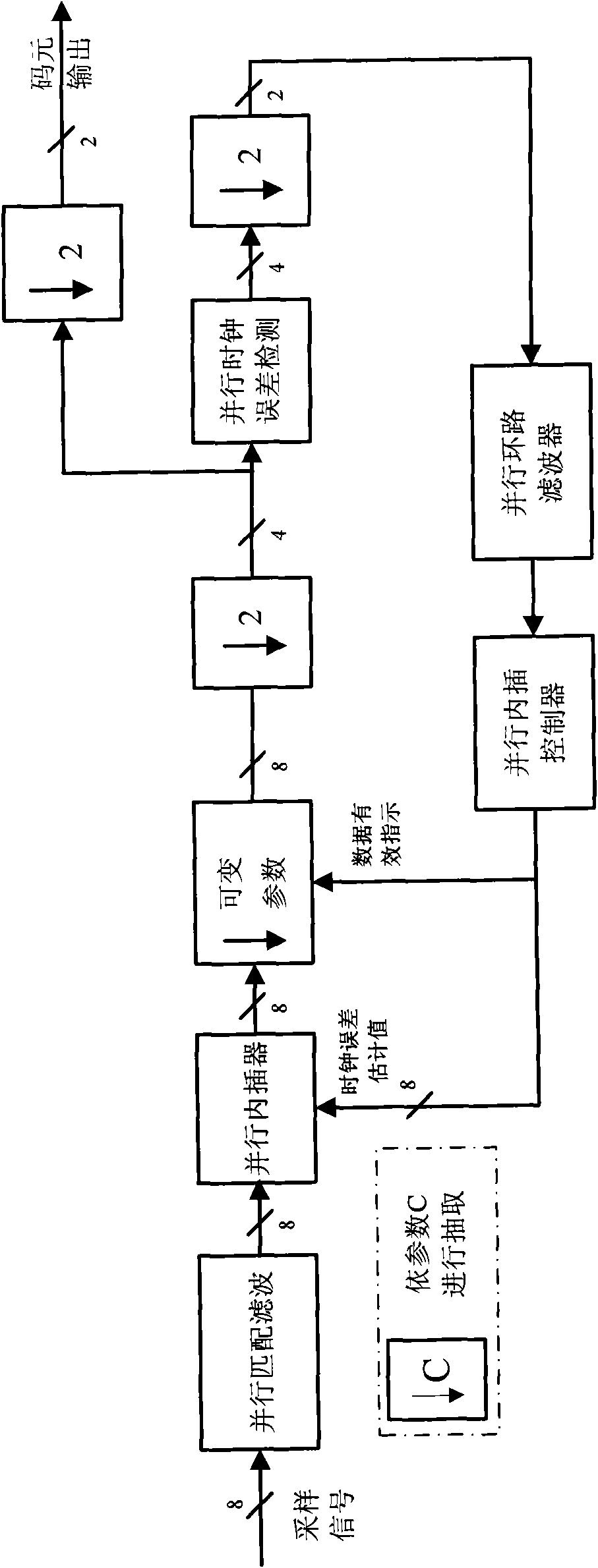

[0081] Module 1: The sampling signal obtained from the high-speed ADC is converted into 8 channels of parallel signals after serial-to-parallel conversion, which are represented by phase 0, phase 1, ..., phase 7 in chronological order. The ADC in this embodiment adopts a sampling rate of 2000MHz. The corresponding parallel signal is 250MHz for each channel. The signal first passes through the time-domain parallel sampling rat...

Embodiment 2

[0128] In this embodiment, the implementation of the demodulation method of the system of the present invention will be described by taking 4-channel parallel digital demodulation as an example.

[0129]Module 1: The sampling signal signal obtained from the high-speed ADC is converted into 4 channels of parallel signals through serial-to-parallel conversion. Through 4 parallel sampling rate conversion modules, the signal sampling rate is slightly higher than 4 times the symbol rate, and this embodiment takes 4.02 times the symbol rate.

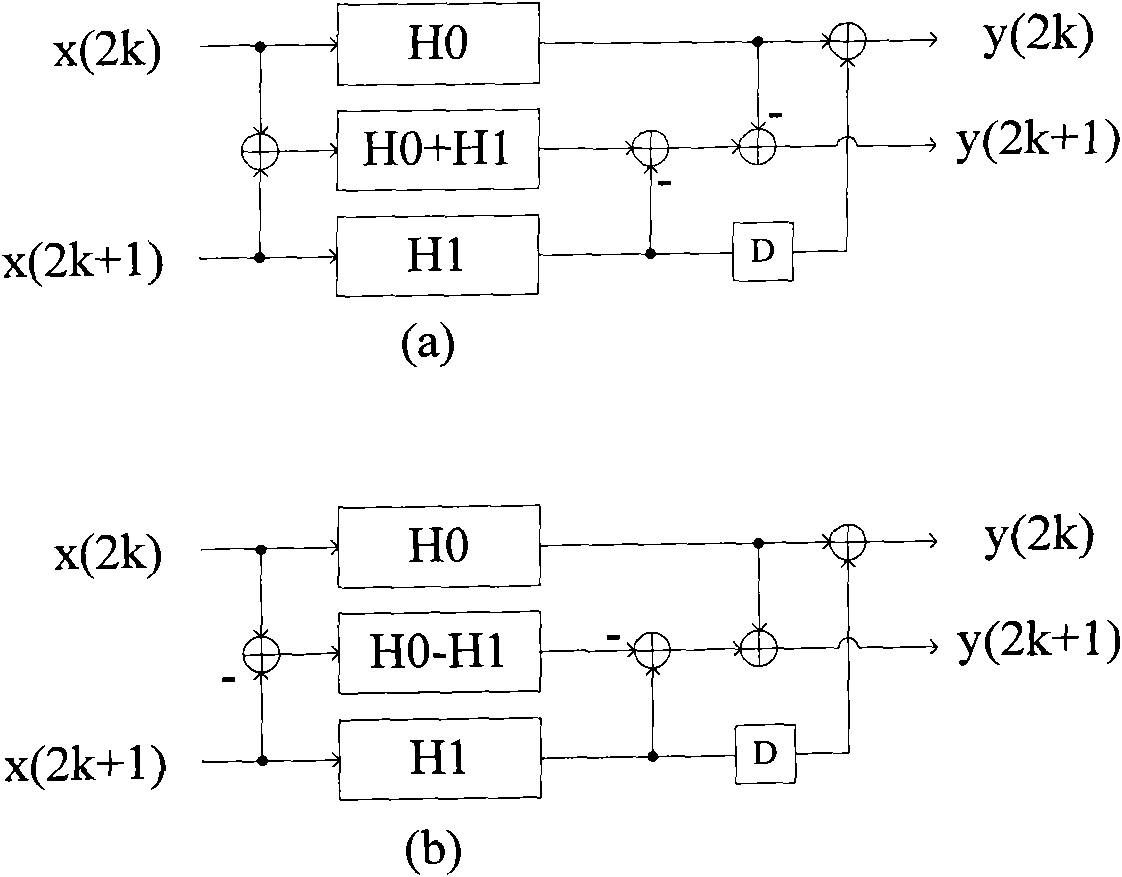

[0130] Module 2: Perform matched filtering on the signal that has undergone sampling rate conversion. The coefficients of the matched filter are the same as those in Example 1, using Figure 4 In the structure shown, this block precedes the parallel clock recovery loop.

[0131] Module 3: Send the matched filtered signal into the parallel clock recovery loop. In this embodiment, the input signal of the clock recovery loop is 4 parallel signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com