10 Gbps bit error analyzing instrument

A technology of bit error test and tester, applied in error detection/prevention using signal quality detector, electromagnetic wave transmission system, digital transmission system, etc. It can solve the problem of loss of synchronization of load signal, and achieve low power consumption and circuit structure. Simple and stable effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the accompanying drawings and implementation examples.

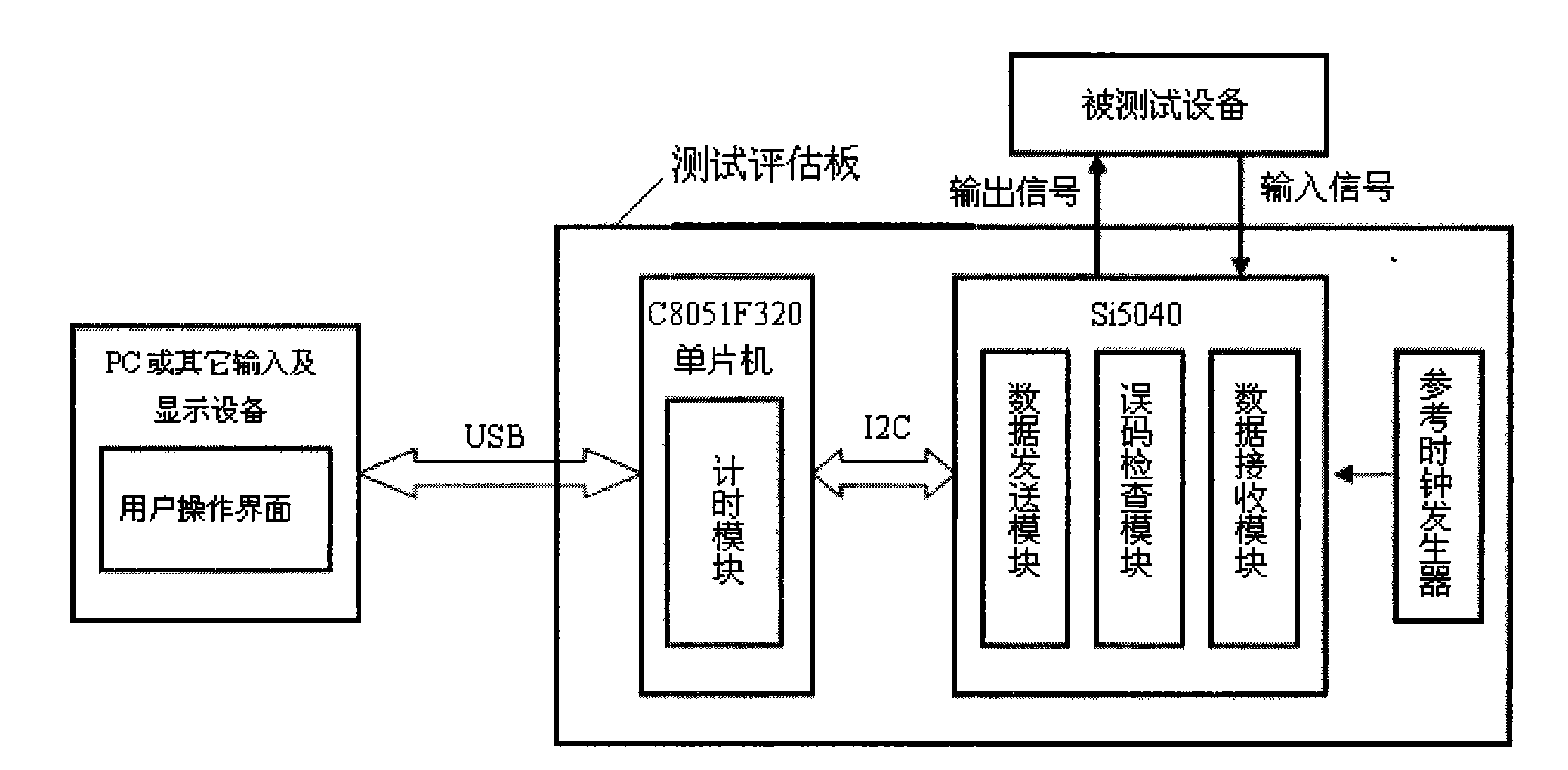

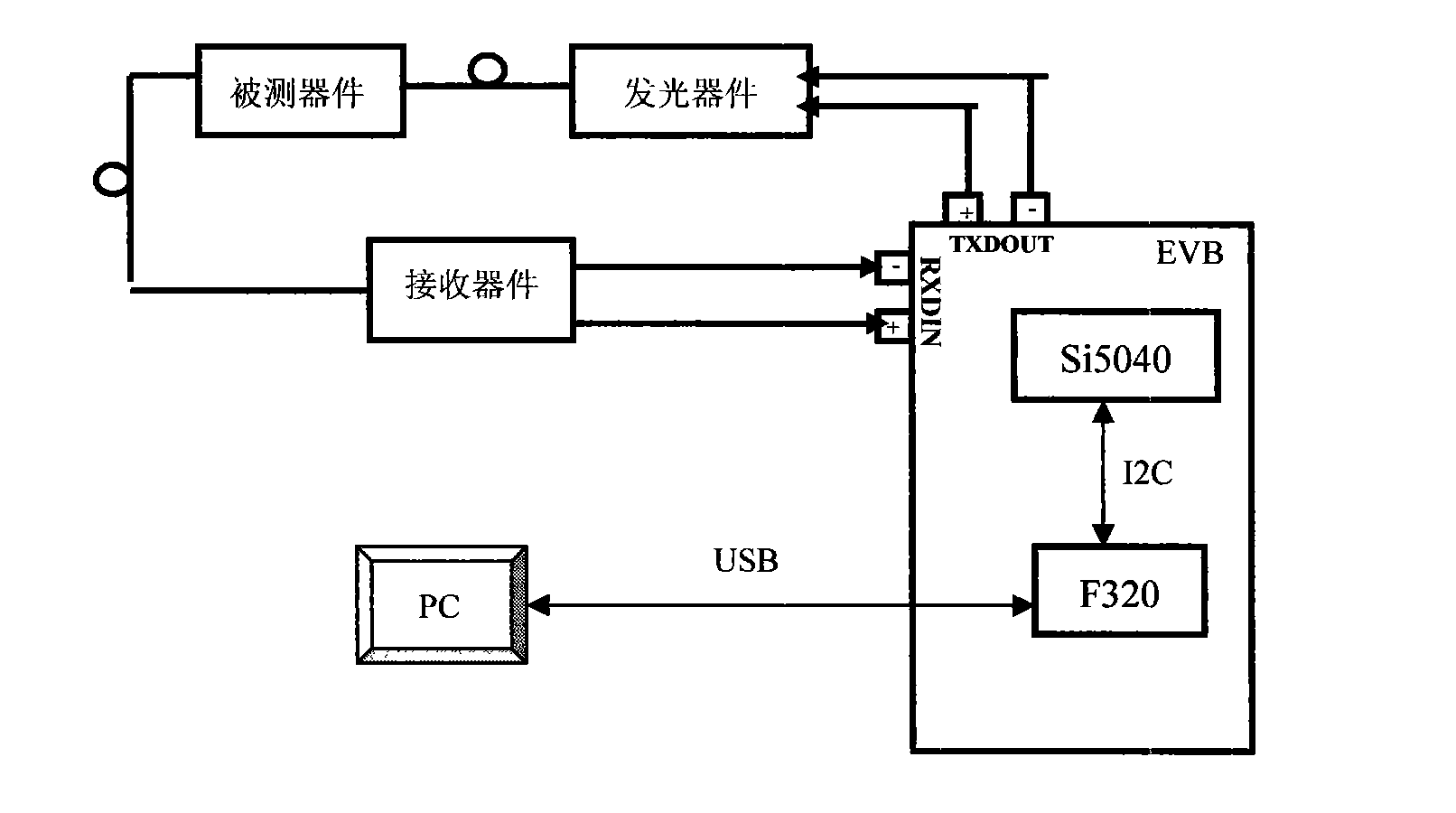

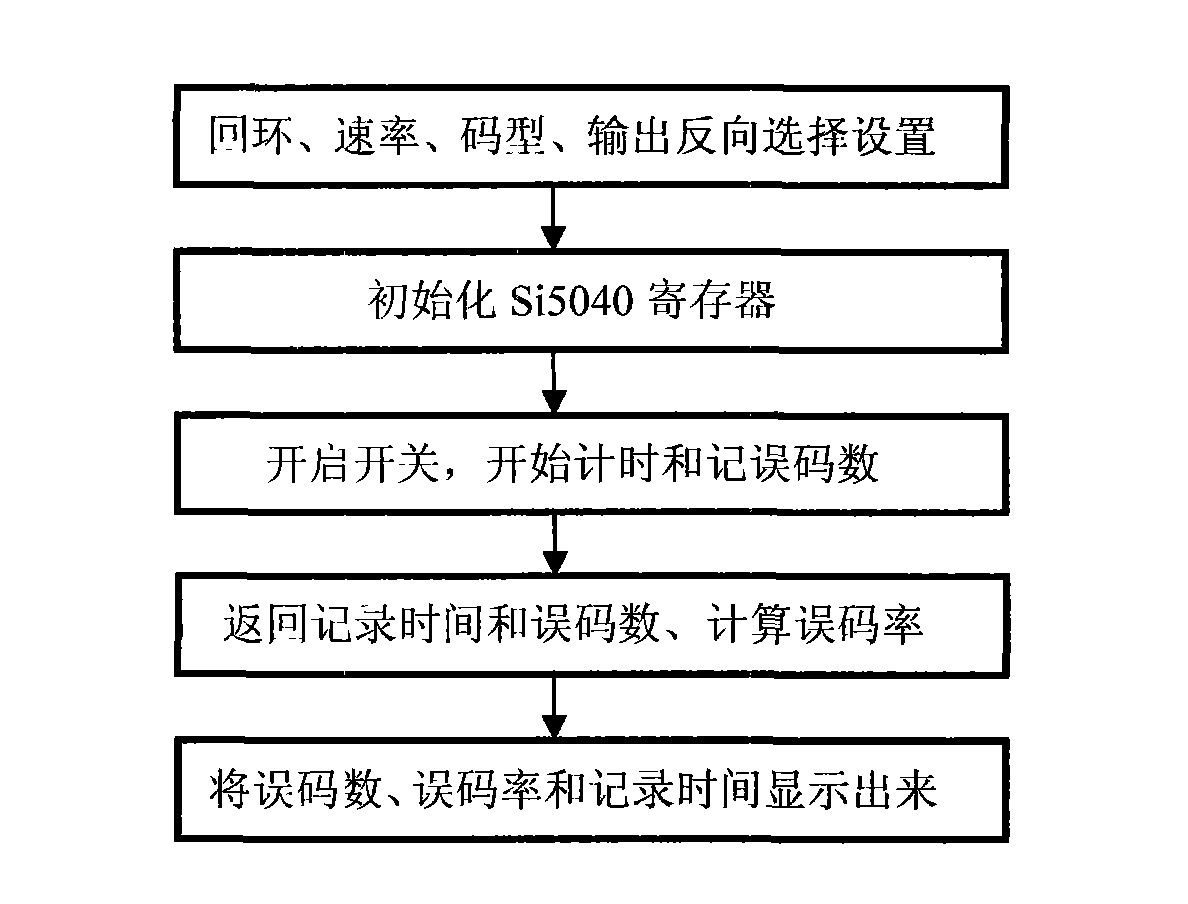

[0020] refer to figure 1 . figure 1 A preferred embodiment of the invention has been described. The 10Gbps error code analysis tester of the present invention mainly includes a test evaluation board connected with the device under test, and it can communicate with the user interaction interface software set on the PC. exist figure 2 On the test evaluation board shown, a bit error test chip module for sending, receiving, and error detection and counting of pseudo-random code sequences is set. The bit error test chip is connected to the device under test, and simultaneously outputs and inputs signals to the device under test.

[0021] The microcontroller is a C8051 series single-chip microcomputer, which is used to communicate with the upper PC and the lower test chip. There are firmware codes on the single-chip microcomputer, which is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com