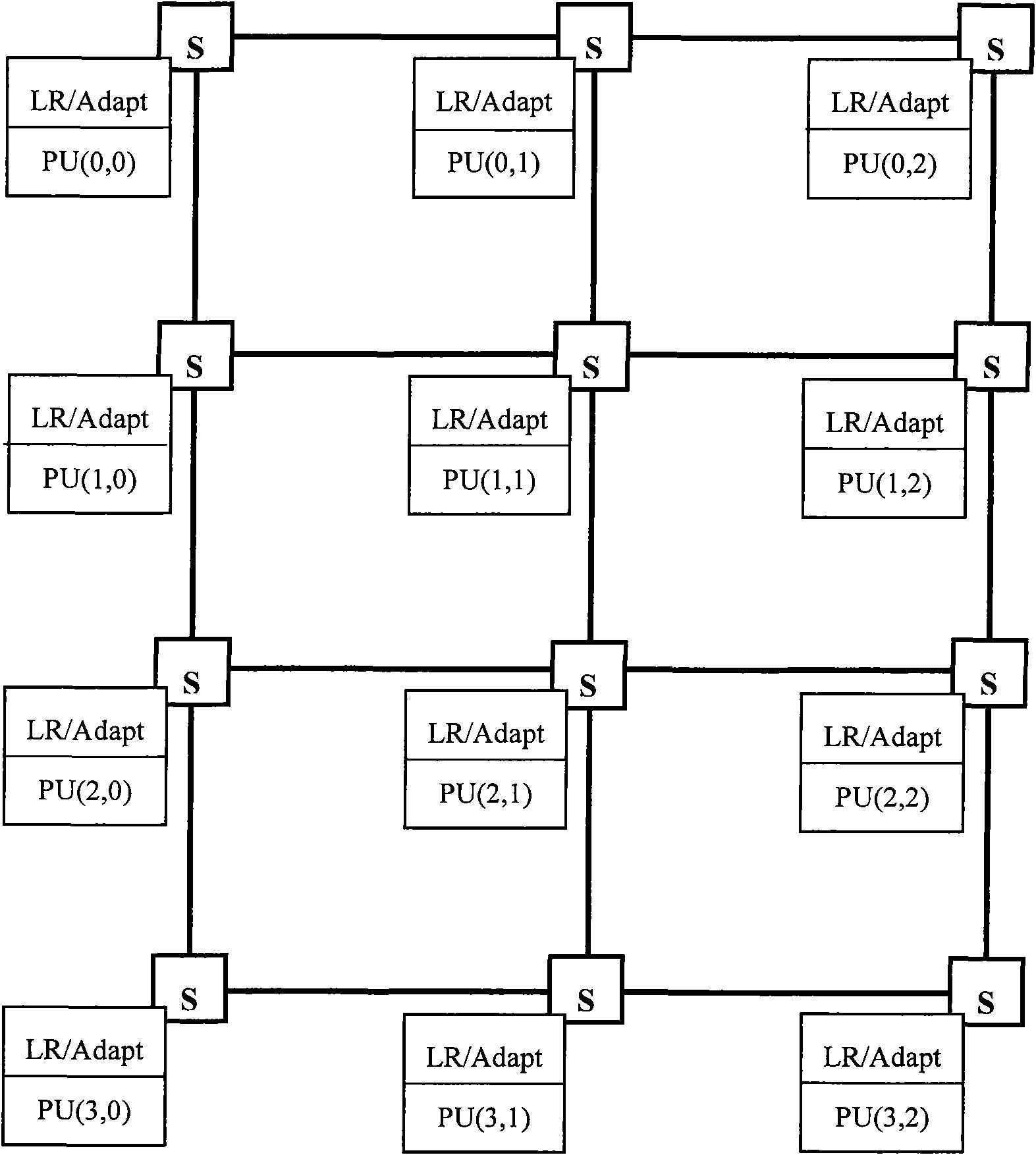

Method for mapping task of network on two-dimensional grid chip

A two-dimensional grid and network-on-chip technology, which is applied to instruments, multi-channel program devices, and electrical digital data processing, can solve problems such as long execution time and unguaranteed degree of optimization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

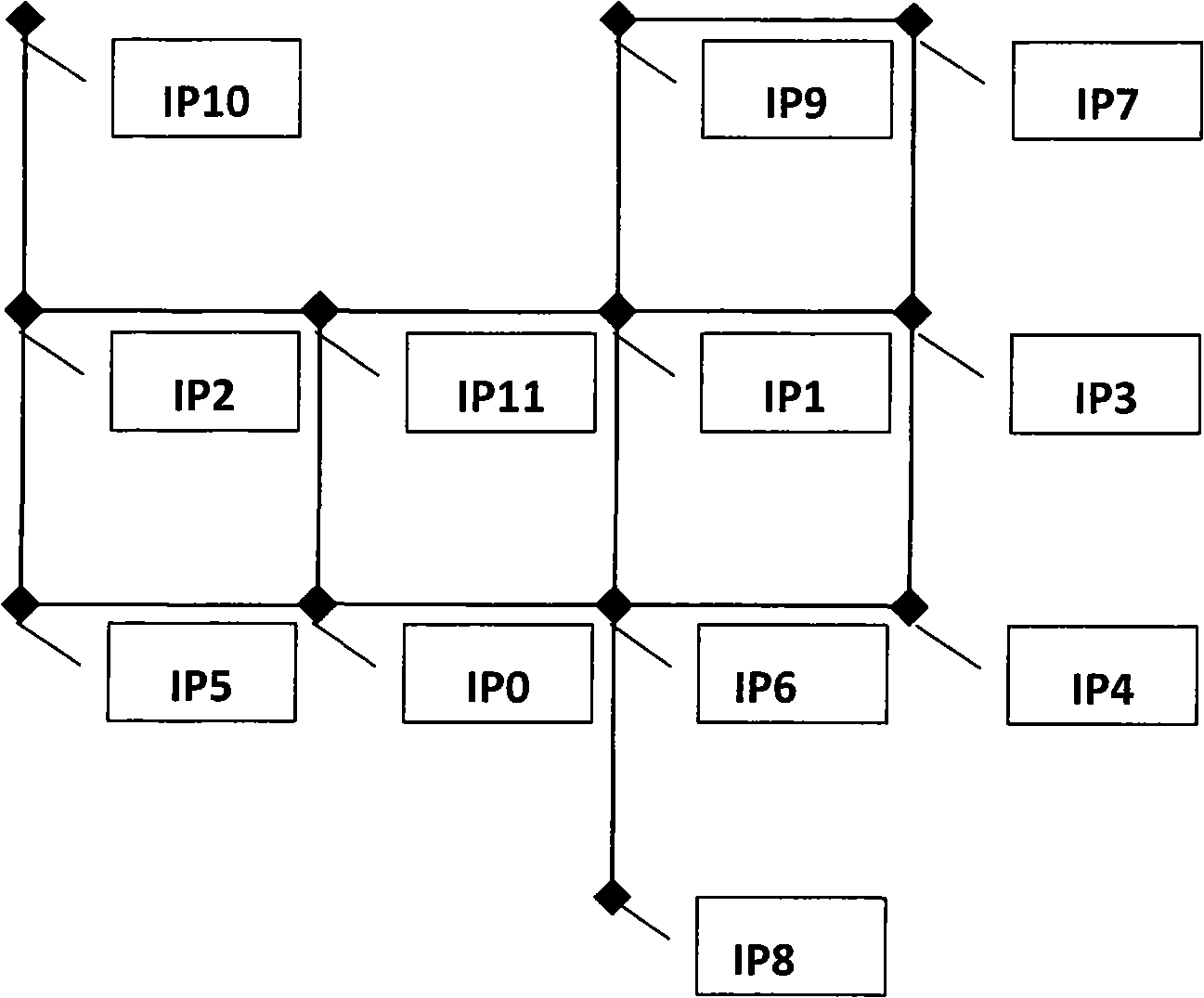

Examples

specific Embodiment approach

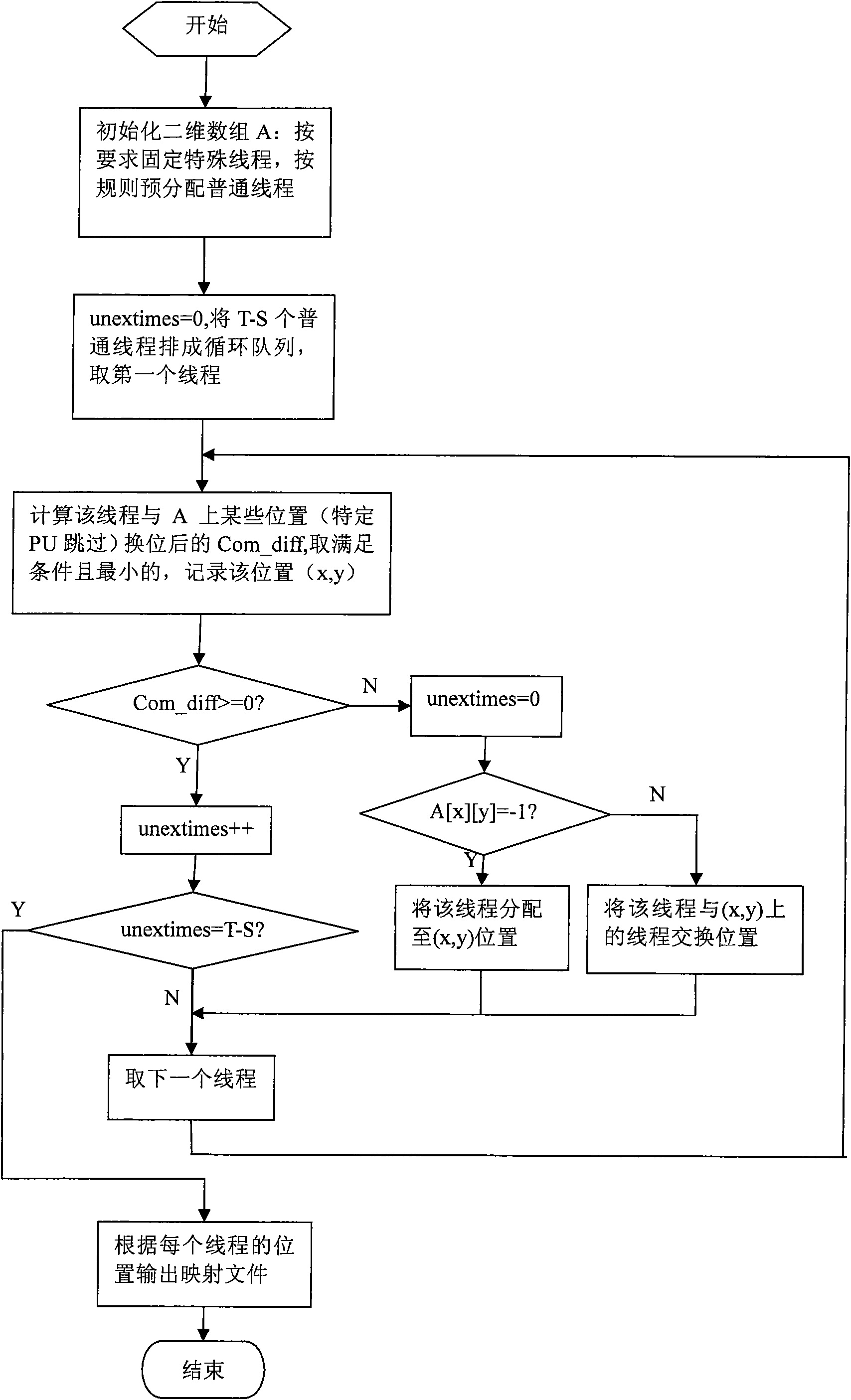

[0058] Based on the above theoretical calculation, the specific implementation of the present invention is as follows:

[0059] Suppose that in a certain task, the number of special threads is S, and the number of ordinary threads is T-S. All special threads are listed in a sorted queue, and all ordinary threads are also added to the queue. Preferably, ordinary threads can be added to the queue in order according to the size of the communication volume between the thread and other threads in the queue. Take a pair of threads with the largest amount of communication, including at least one ordinary thread that has not yet joined the queue. If two threads are not in the queue, both threads are attached to the end of the queue. Their order depends on the maximum communication volume between these two threads and other threads in the queue, with the larger value first; If one is already in the queue, another thread is added to the end of the sorting queue. Then take the next pair o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com