Test pattern generator of integrated circuit and test method thereof

An integrated circuit and test pattern technology, applied in the low-power test pattern generator and its testing field, can solve the problems of reducing internal circuit jumping activities, hardware overhead and delay increase, etc., to reduce test power consumption and reduce scanning The effect of power consumption and short test length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

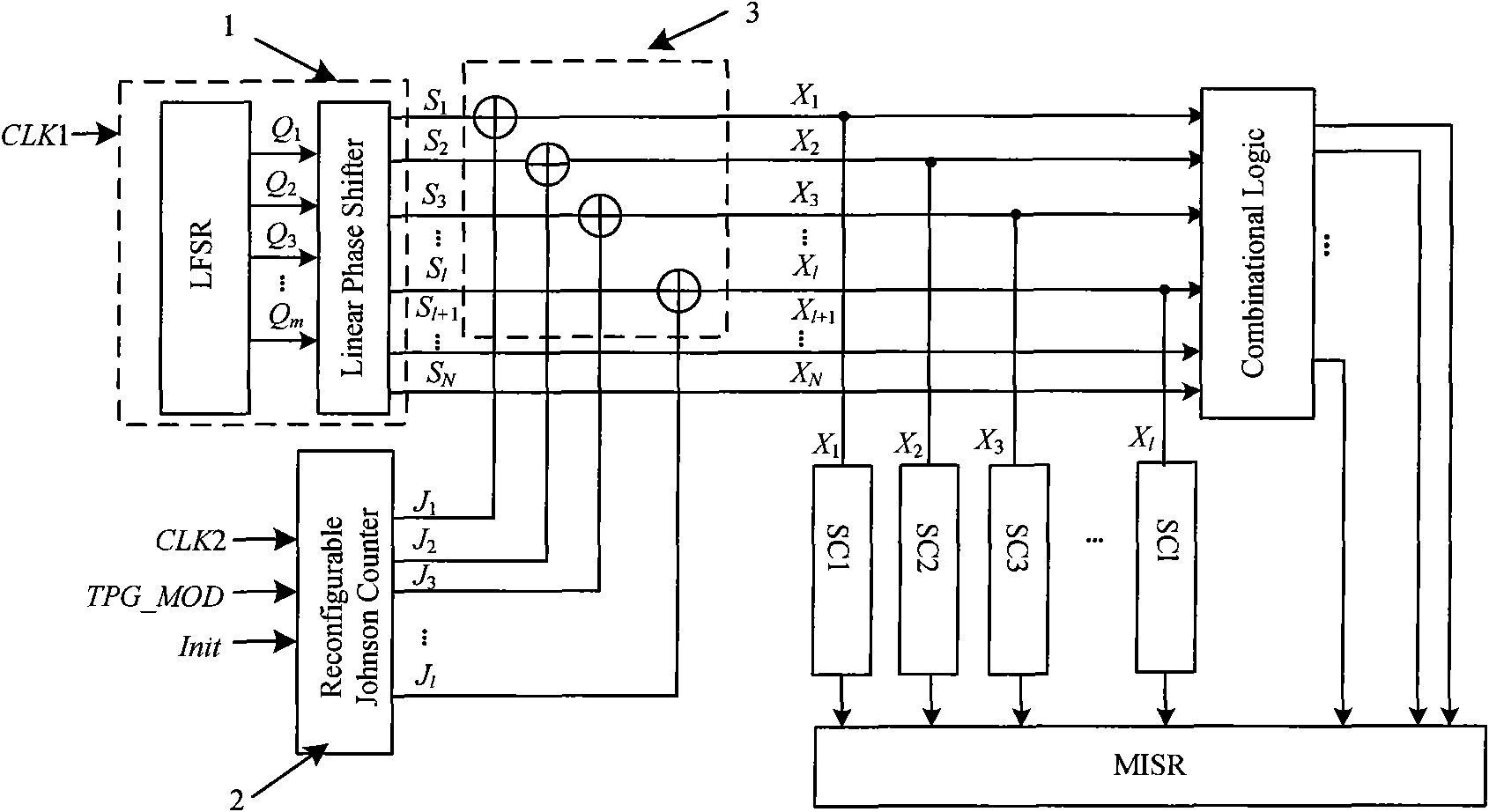

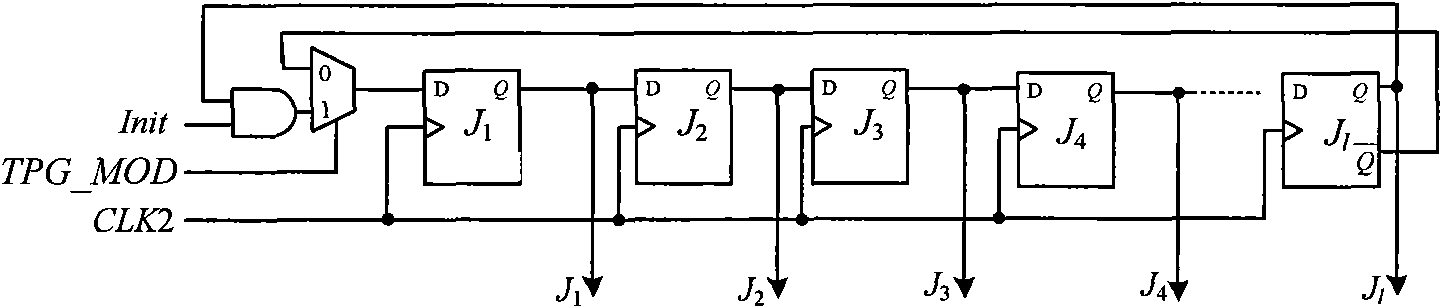

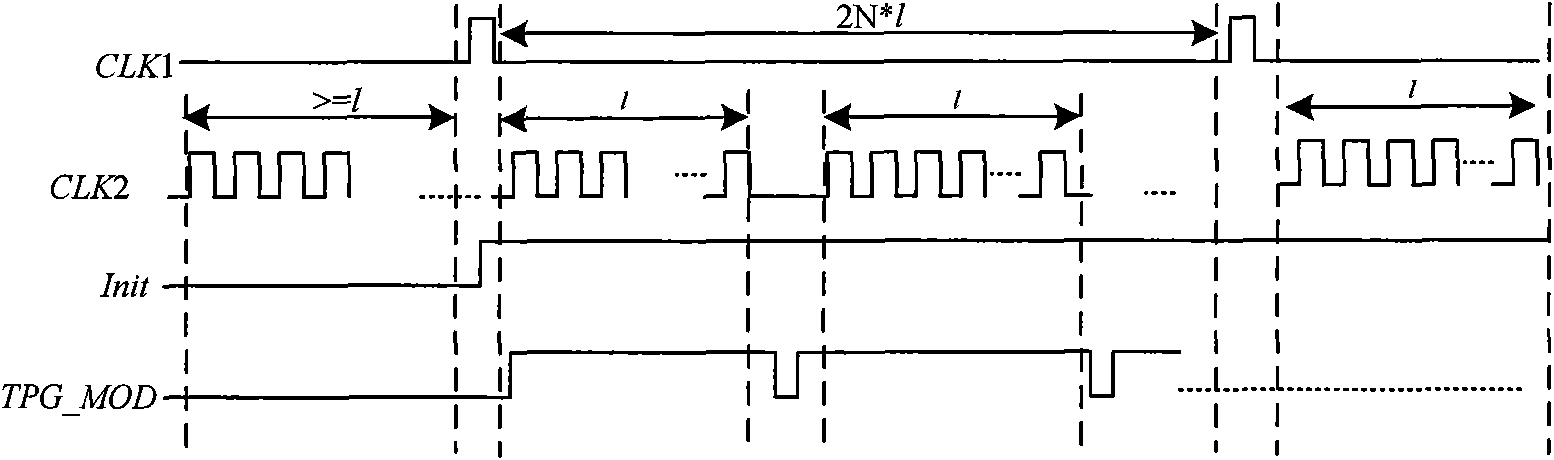

[0024] refer to figure 1, RJ-LFSR mainly includes: Reconfigurable Johnson Counter (ReconfigurableJohnson Counter) 2, Linear Feedback Shift Register (LFSR) 101, Linear Phase Shifter (Linear PhaseShifter) 102 and Exclusive OR Gate Network (XOR-Network) 3.

[0025] A seed sequence generator (Seed Generator) 1 is composed of a linear feedback shift register 101 and a linear phase shifter 102, and is used to generate a seed sequence. Among them, the clock (CLK1) frequency f of the linear feedback shift register 101 1 , generating sequence Q=[Q 1 Q 2 ...Q m ], m is a natural number; in the present invention, the output of the LFSR is allowed to be all 0 states. Linear phase shifter 102 will sequence Q=[Q 1 Q 2 ...Q m ] logically expanded to N-bit output sequence S=[S 1 S 2 ... S m S m+1 ... S N ], that is, the seed sequence, and satisfy N>m.

[0026] For a linear phase shifter and a linear feedback shift register with an N-bit width, the following logical relationship i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com