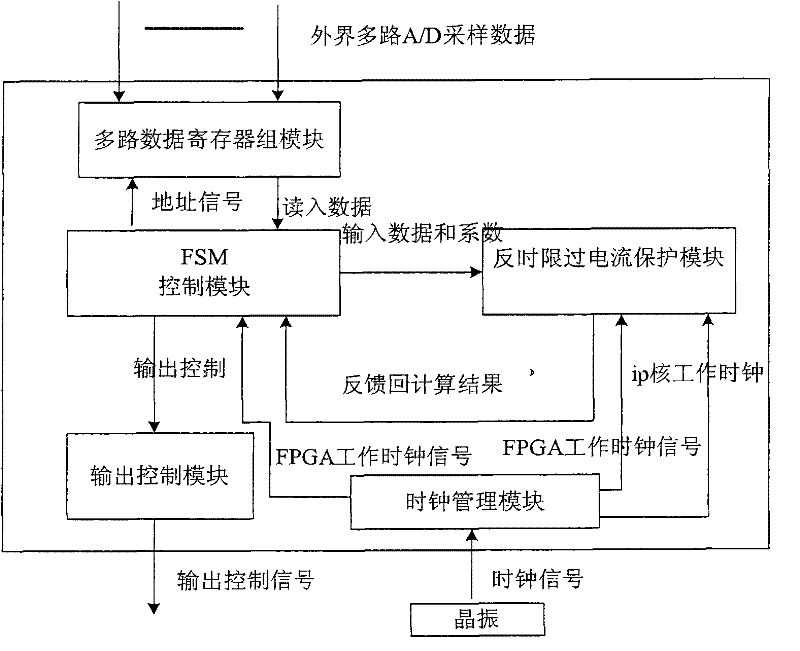

FPGA-based solid-state power controller inverse time over-current protection device

A protection device and solid-state power technology, applied in the direction of program control design, instruments, memory systems, etc., can solve the problems of poor anti-electromagnetic interference performance, insufficient stability, and insufficient precision, and achieve strong real-time performance, strong stability, The effect of simple module structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

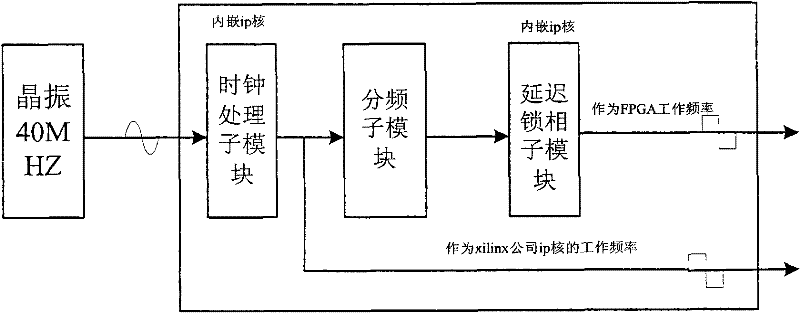

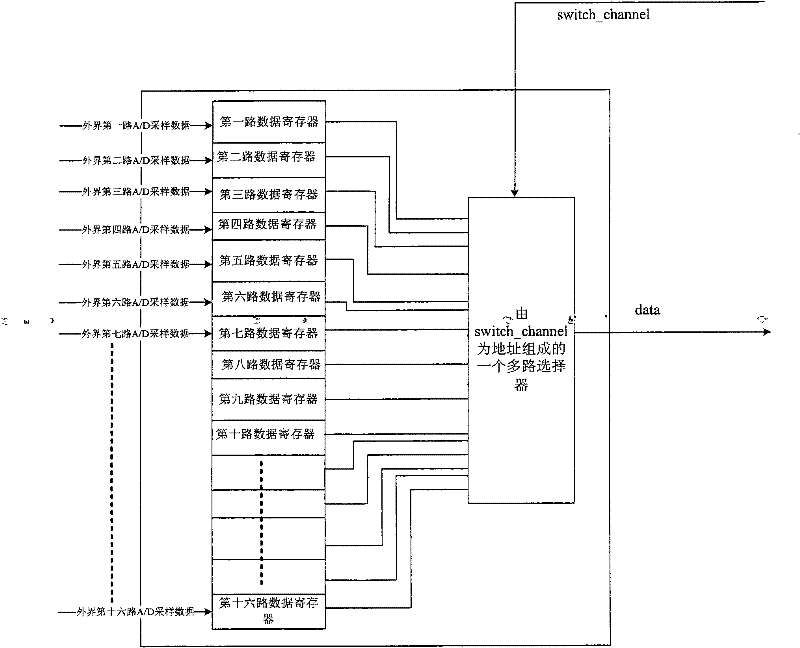

[0031] The concrete realization of the present invention is to finish inside FPGA, and this FPGA uses the xcv300 of the virtex series of xilinx company, and the register described below is spliced by LUT, and adder and multiplier adopt the ip core that xilinx company provides, And their operating frequency is 40MHZ, and each operation requires two clock cycles. The adder is a signed adder, and the multiplier is integer multiplication. The comparators, latches, and finite state machines used The counter and the counter are spliced based on FPGA LUT, flip_flop, and slice. The memory is the block_ram block embedded in the FPGA. The size of each block_ram block is 4Kbit. The working clock of the entire FPGA is 1.818181MHZ.

[0032] The basic principle of the inverse time overcurrent protection algorithm is: the mathematical expression of the transmission line inverse time overcurrent protection characteristic curve equation is t = k ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com