Semi-conductor device, shallow groove isolation construction forming method

A technology of isolation structure and shallow trench, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc. Trench leakage current, effect of size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

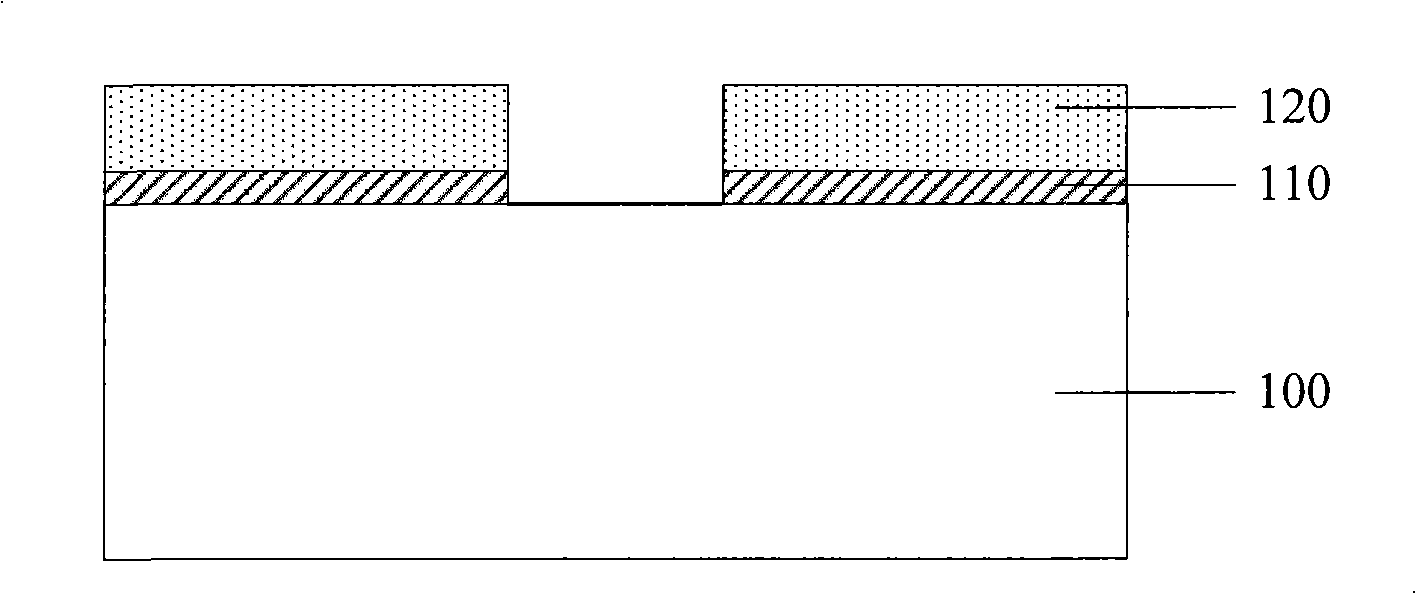

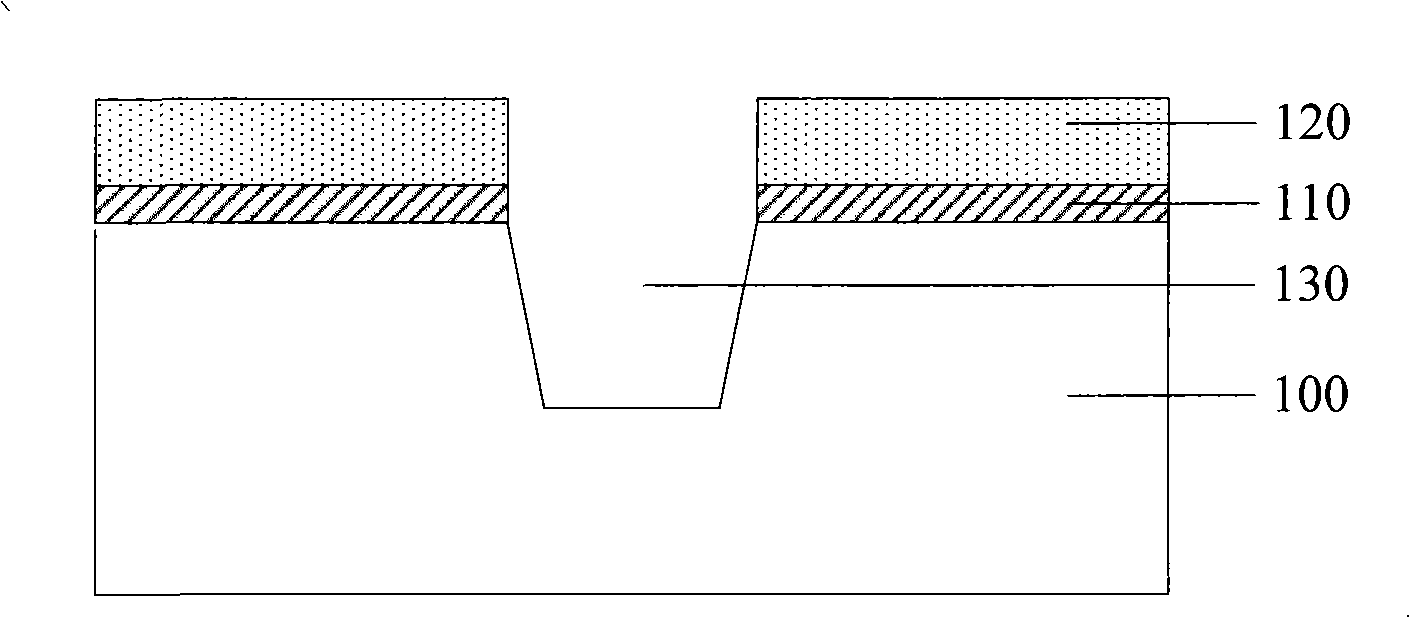

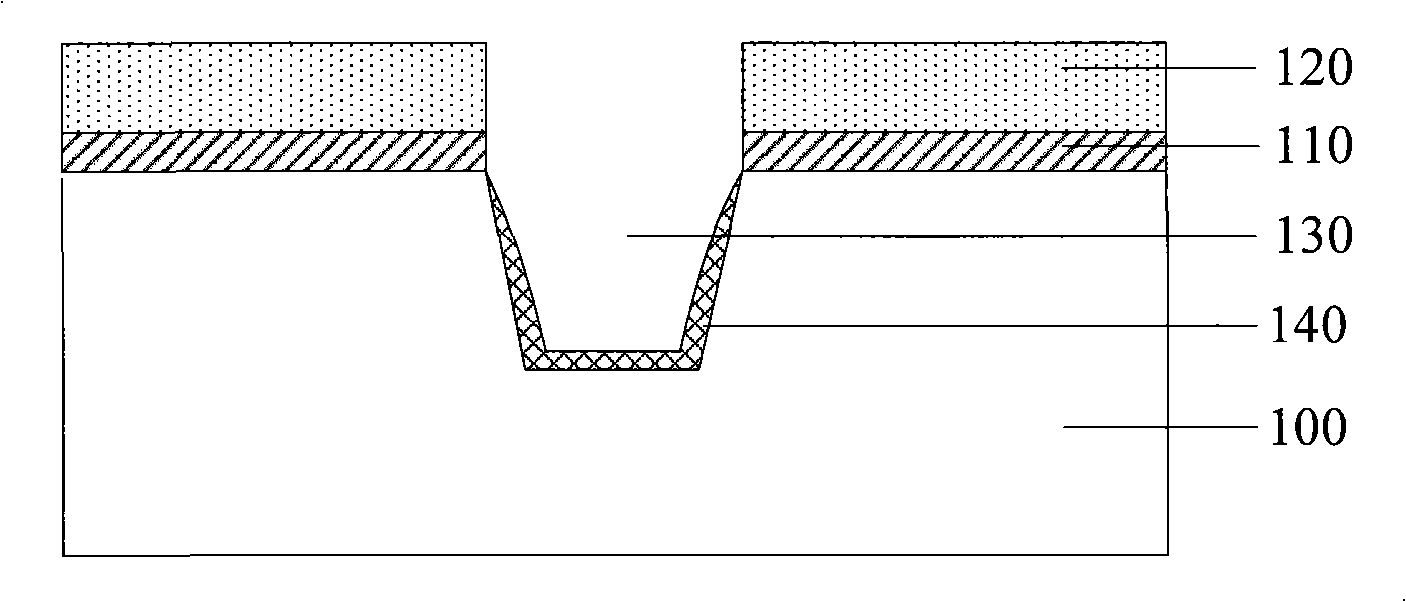

[0034] In traditional CMOS circuits, the width and depth of the isolated shallow trench isolation (STI) determine whether the isolation is effective, and too small a size may cause the STI to break down and fail when subjected to high voltage. Therefore, in the common CMOS device area, STI must ensure sufficient width and depth. But in the pixel unit circuit of CMOS image sensor, such as figure 2 As shown, in order to maintain high photosensitive sensitivity, the potential of the N region of the left photodiode 1 should not be too high, generally not exceeding 0.7V. Therefore, for the pixel unit circuit, the depth and width requirements of the STI are very low, and reducing the size of the STI is equivalent to expanding the P well covering the STI, and can also achieve the purpose of preventing STI leakage current.

[0035] Therefore, in the implementation manner of the present invention, semiconductor devices with different STI sizes can be formed by taking advantage of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com