Parameter computation method of RFCMOS model with expandability

A parameter calculation and model technology, applied in the direction of calculation, electrical digital data processing, special data processing applications, etc., can solve problems such as poor scalability, and achieve the effects of improving model accuracy, achieving scalability, and reducing design costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

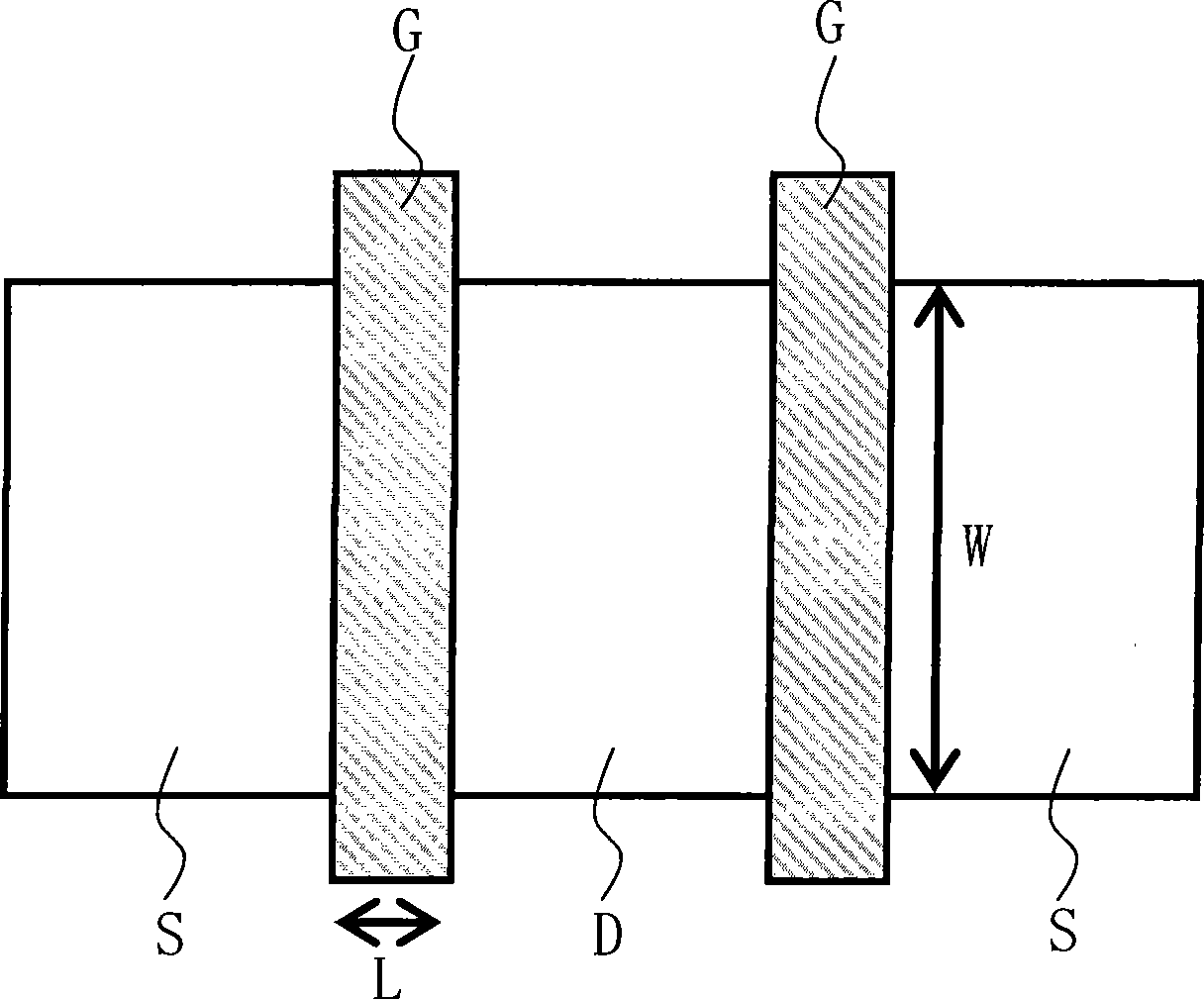

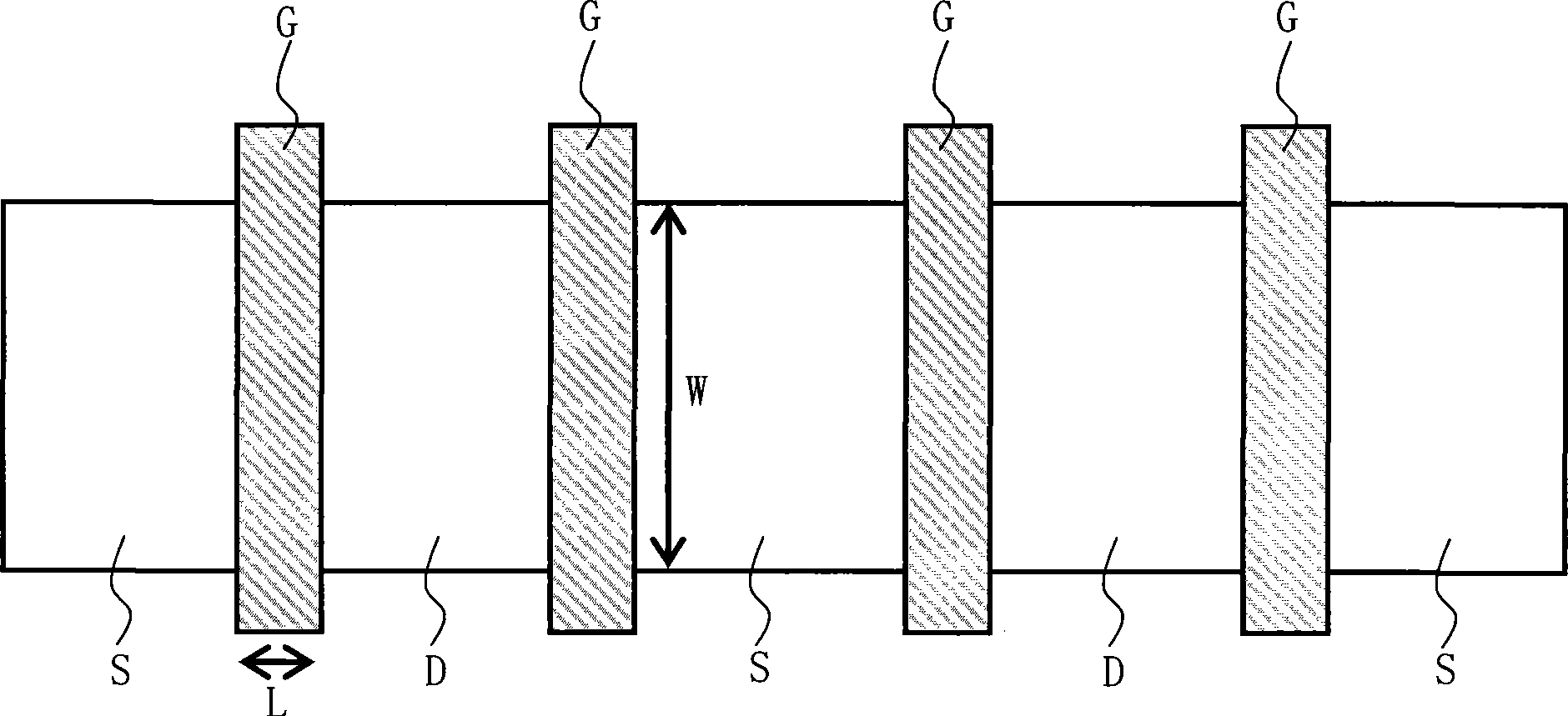

[0015] In RFCMOS circuit design, in order to reduce the impact of gate parasitic resistance and various parasitic PN junctions on the high frequency performance of RFCMOS devices, RFCMOS devices generally adopt a multi-gate parallel layout structure (Multi-finger structure). see figure 2 RFCMOS devices with a parallel gate count of 2 are shown and image 3 The schematic diagram of an RFCMOS device with four parallel gates is shown, and its layout parameters include transistor channel length L, transistor channel width W, and the number nf of transistor parallel gates.

[0016] exist figure 1 In the RFCMOS model shown, the source resistor R S and drain resistance R D It can be comprehensively reflected by the parameter Rdsw of the BSIM3v3 model. The parameter Rdsw represents the source-drain parasitic resistance per unit width (Parasitic resistance per unit width), so the source resistance R S and drain resistance R D It does not need to be calculated separately, and can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com