Method for manufacturing double-stress membrane complementary metal oxide semiconductor (CMOS) transistor

A technology of oxide semiconductors and complementary metals, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of the stability of complementary metal oxide semiconductor transistors, affecting the process, etc., so as to improve stability and increase The effect of the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

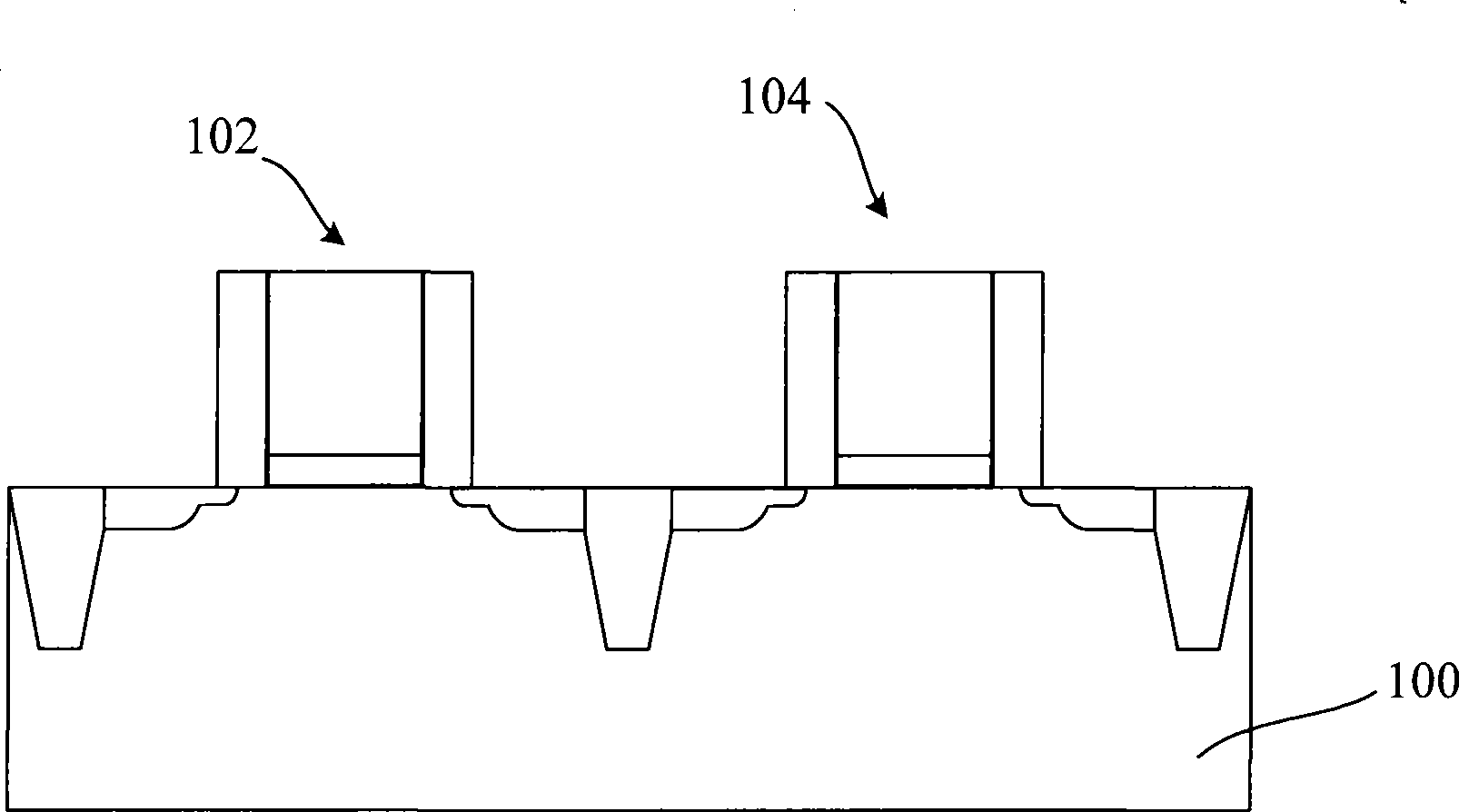

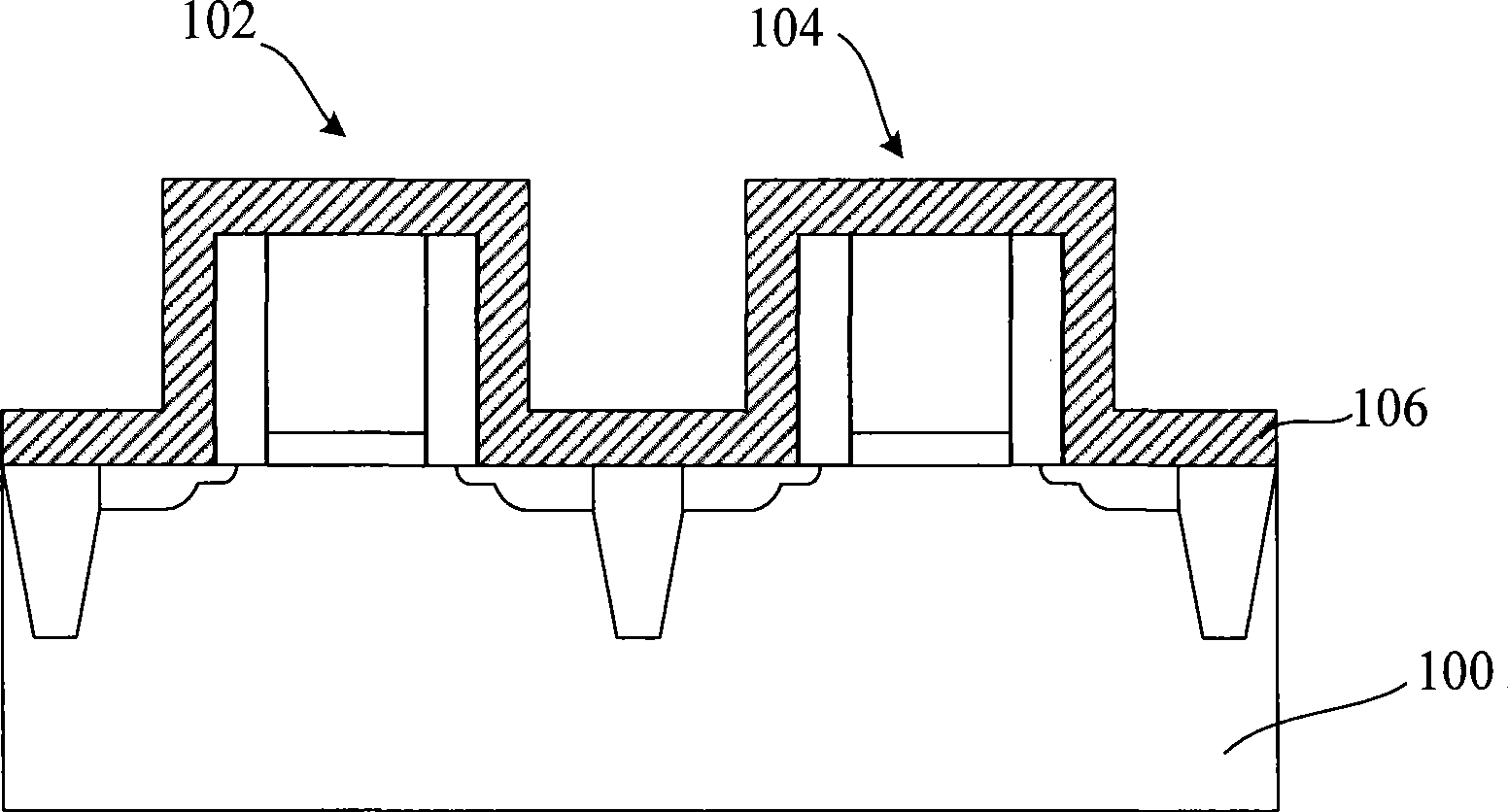

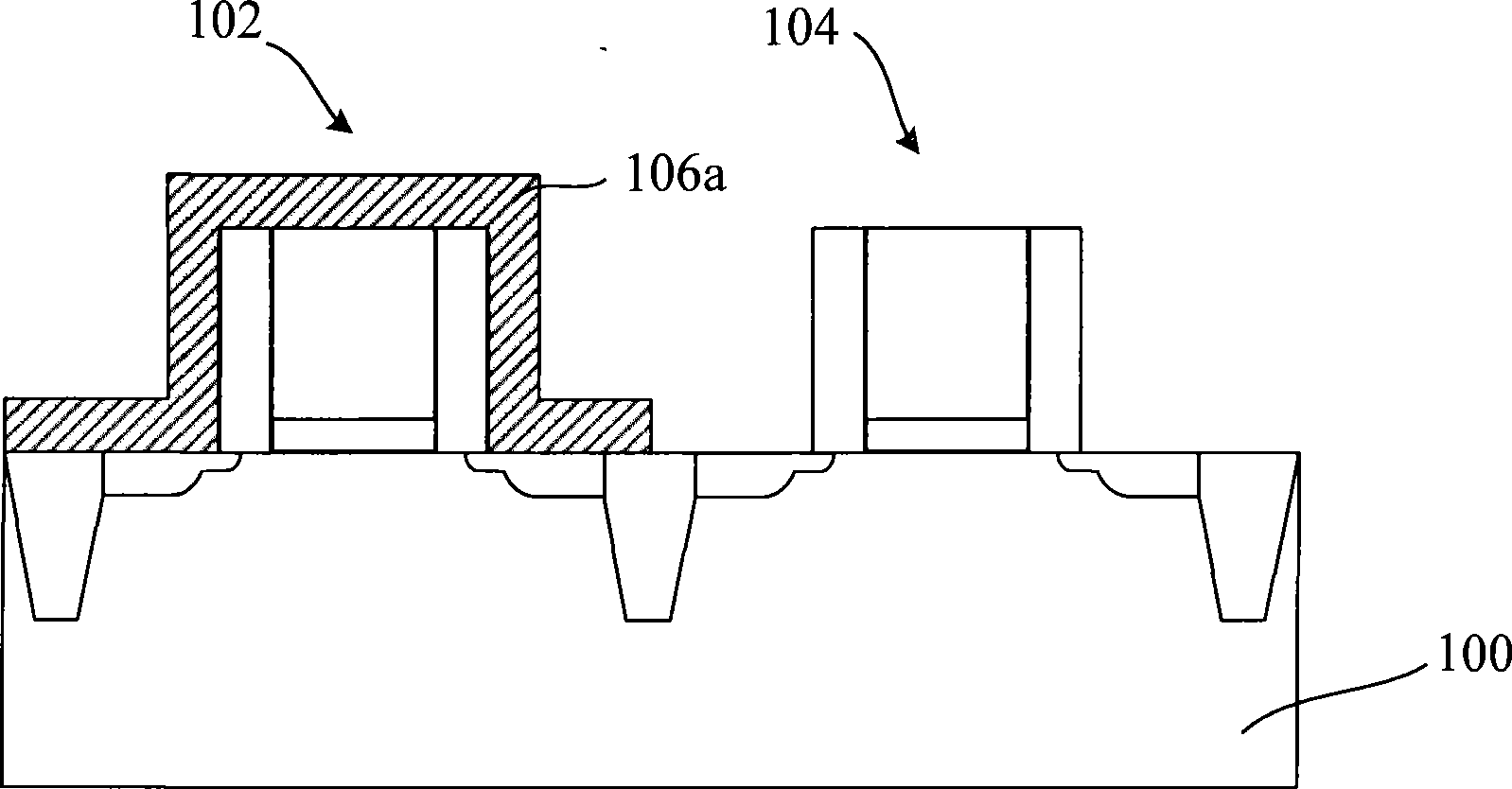

[0054] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0055]Covering the stress film on the MOS transistor can increase the mobility of carriers in the conduction channel, thereby improving the response rate of the MOS device. The NMOS transistor in the CMOS is covered with a tensile stress film, and the PMOS transistor is covered with a compressive stress film, which can improve the carrier mobility of electrons and holes in the NMOS and PMOS transistors, respectively.

[0056] In an embodiment of the present invention, a method for manufacturing a dual stress film complementary metal oxide semiconductor transistor is provided;

[0057] Firstly, a first stress film for improving carrier mobility of the first transistor is formed on the first transistor, and then a first stress film for improving carrier mobility of the second transistor is formed on the first stress film and the second trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com