Inside imbedded type line board technique with conductive hole

An embedded, conductive hole technology is applied in the manufacturing of multilayer circuits, the formation of electrical connection of printed components, etc., and can solve the problem of uneven contact stress distribution, uneven patterned circuit layer 150, and the quality of electrical connection between chips and circuit boards 100. Poor and other problems, to achieve good quality results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

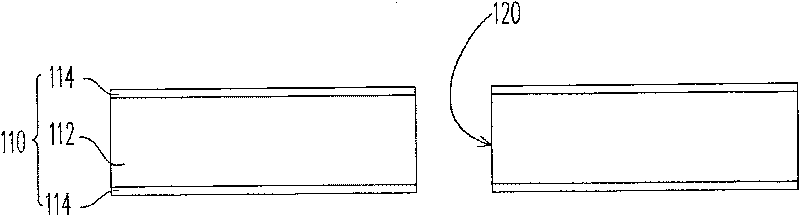

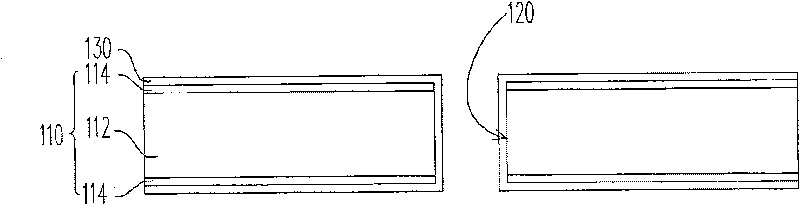

[0030] figure 2 A flow chart of manufacturing an embedded circuit board with conductive vias according to a preferred embodiment of the present invention is shown. Please refer to figure 2 , The embedded circuit board process of this embodiment includes the following steps: First, step S1 is performed to provide an embedded circuit board. Next, step S2 is executed to form openings on the embedded circuit substrate. Then, step S3 is executed to form a conductive layer on the first surface, the second surface and the inner wall of the opening of the embedded circuit substrate. Afterwards, step S4 is performed to remove the conductive layer on the first surface, the second surface and outside the opening to form a conductive hole. Hereinafter, this embodiment will illustrate the above circuit board process with a detailed process sectional view.

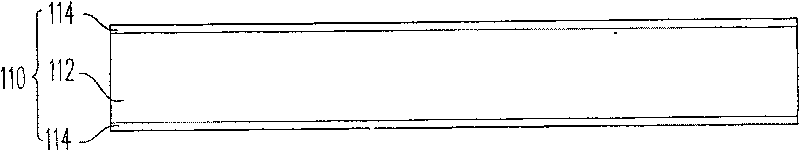

[0031] Figures 3A to 3E shown as figure 2 The process cross-section of the embedded circuit board with conductive vias. The...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com