Processor and method by using batten check to switch instruction mode

An instruction mode and processor technology, applied in the direction of the address formation of the next instruction, machine execution device, etc., can solve the problem that 32-bit instructions and 16-bit instructions cannot be mixed and stored, the program code storage space cannot be optimized, and mixed storage is in the Issues such as the same block

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

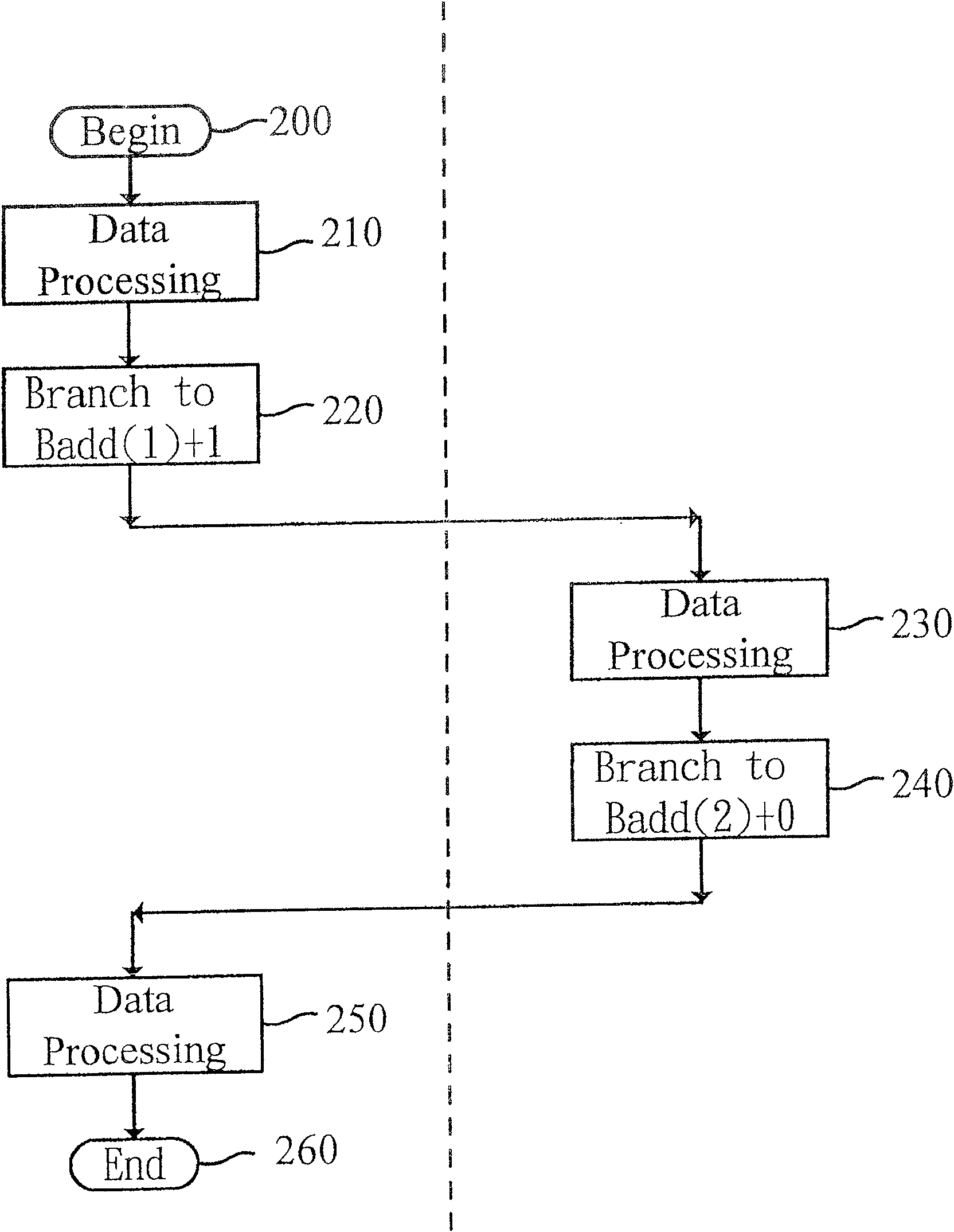

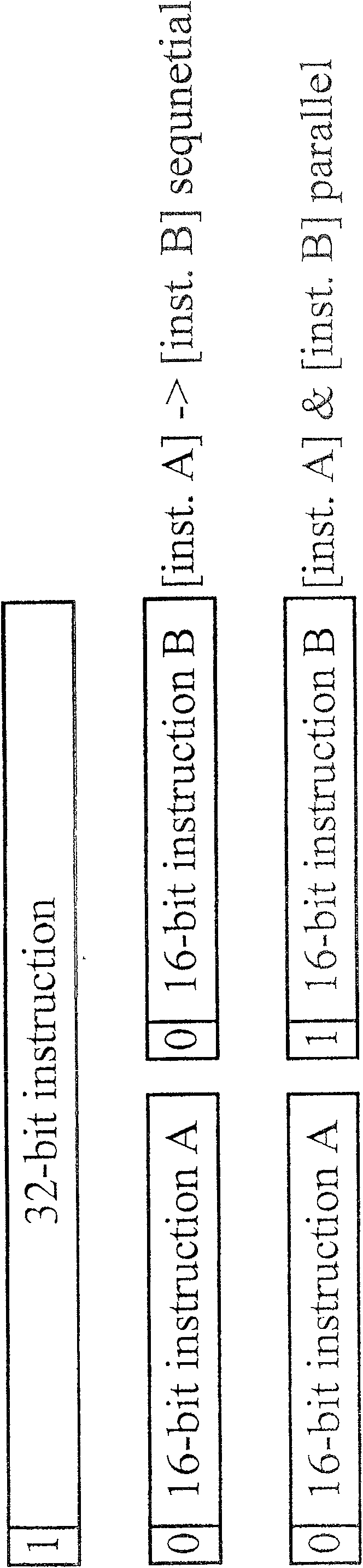

[0020] The processor and method for switching instruction modes using the same bit check of the present invention can respectively execute N-bit and 2N-bit mode instructions in N-bit and 2N-bit modes, N is an integer greater than or equal to 4, and the N-bit mode instructions are composed of An N-bit word group, the 2N-bit mode command is composed of two N-bit word groups, each N-bit word group contains P parity bits and (N-P) bit instruction codes, P is greater than or equal to 1 Integer, in the present embodiment, the N value is preferably 16 (also can be 8, 9, 32...), the P value is preferably 1, but it is only for the convenience of explanation, is not to limit the use of the present invention scope and powers.

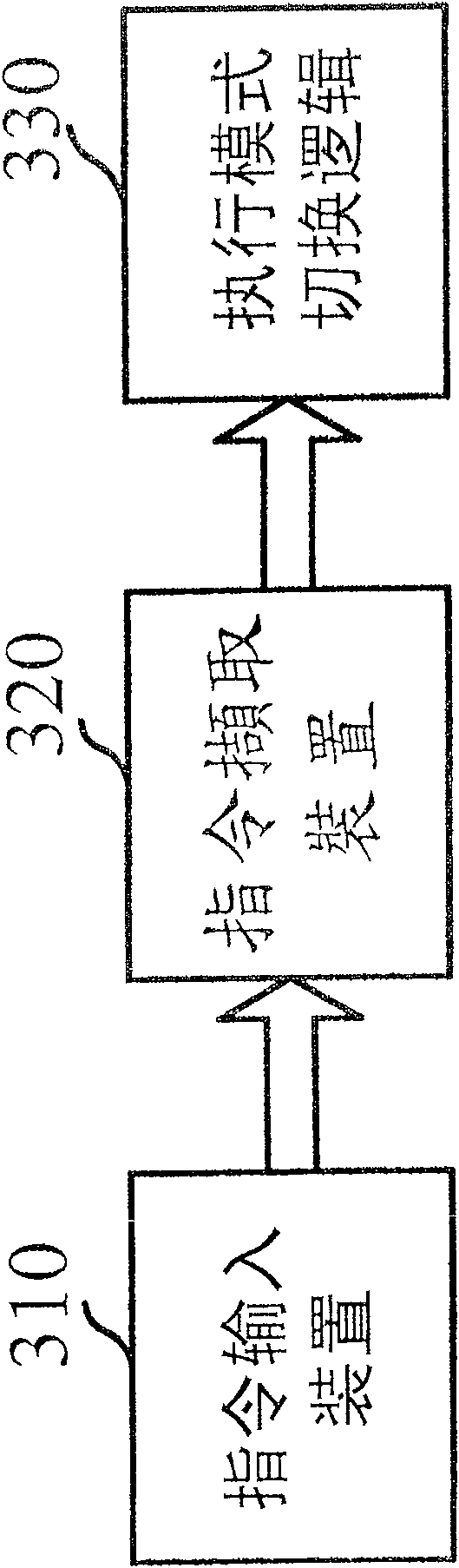

[0021] image 3 It shows the system architecture of the processor using parity check to switch the instruction mode of the present invention, which includes an instruction input device 310, an instruction fetch device 320 and an execution mode switching logic 330...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com