High speed deposition micro crystal silicon solar battery P/I interface processing method

A technology of solar cells and processing methods, which is applied to circuits, electrical components, sustainable manufacturing/processing, etc., can solve the problems of increasing the P/I interface defect state and the thickness of the amorphous incubation layer, so as to improve battery efficiency and reduce interface State, the effect of increasing the initial crystallization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

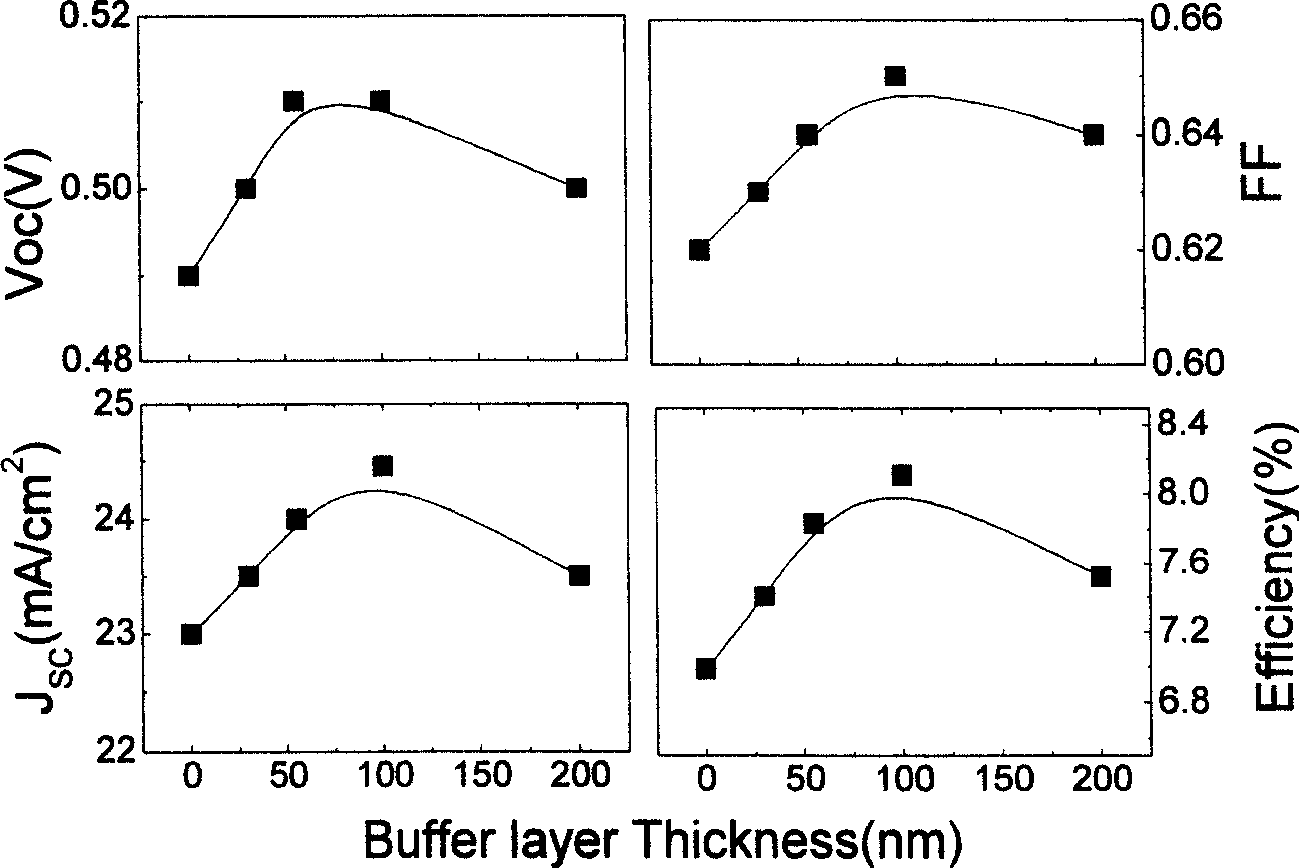

[0025] Embodiment 1, the preferred implementation conditions of the present invention are as follows: the substrate is placed in the reaction chamber, the air pressure in the reaction chamber is maintained at 1.6 torr, and the electrode distance is 12 mm. Power on to start deposition, first set the glow power to 25W, the silane concentration to 3%, the first deposition rate under this condition is about 3 / s, keep the first deposition rate for 5 minutes and 30 seconds, and form the first intrinsic microcrystalline silicon thin film layer with low defect and high crystallization of about 100nm; 50W, silane concentration is 5%, the second deposition rate under this condition is about The second deposition rate was maintained for 27 minutes to form a second intrinsic microcrystalline silicon film layer of about 1400 nm. From figure 2 It can be seen that the cell efficiency with the 100nm low-defect and high-crystallization low-velocity interfacial layer increases by about on...

Embodiment 2

[0026] Example 2, if only the second deposition rate is used to deposit the intrinsic microcrystalline silicon film, the corresponding figure 2 Intrinsic microcrystalline silicon film layer thickness is 0nm, that is, there is no low-speed intrinsic microcrystalline silicon film layer. The implementation conditions are as follows: the substrate is placed in the reaction chamber, the air pressure in the reaction chamber is kept at 1.6torr, and the electrode The distance is 12mm. The glow power was set to 50W, and the silane concentration was 5%, the deposition rate under these conditions was about The deposition rate was maintained for 29 minutes (time), and an intrinsic microcrystalline silicon thin film layer of about 1500 nm (thickness) was formed. From figure 2 It can be seen that the efficiency of the cell without the low-speed intrinsic microcrystalline silicon thin film layer is the lowest relative to the cell efficiency with the low-speed intrinsic microcrystalline ...

Embodiment 3

[0027] Embodiment 3, if the thickness of the first intrinsic microcrystalline silicon film deposited by the first deposition rate is thicker, the implementation conditions are as follows: the substrate is placed in the reaction chamber, the air pressure in the reaction chamber is maintained at 1.6torr, and the electrode The distance is 12mm. Electricity begins to deposit, first set glow power to be 25W, silane concentration is 3%, the first deposition rate under this condition is about The first deposition rate is maintained for 11 minutes to form a first intrinsic microcrystalline silicon thin film layer with a thickness of about 200 nm, low defects and high crystallization. Then under the condition of other process conditions unchanged, only the glow power is changed to 50W, the silane concentration is 5%, the second deposition rate under this condition is about The second deposition rate is maintained for 25 minutes to form a second intrinsic microcrystalline silicon fil...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com