Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Reducing replay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Programmable load replay precluding mechanism

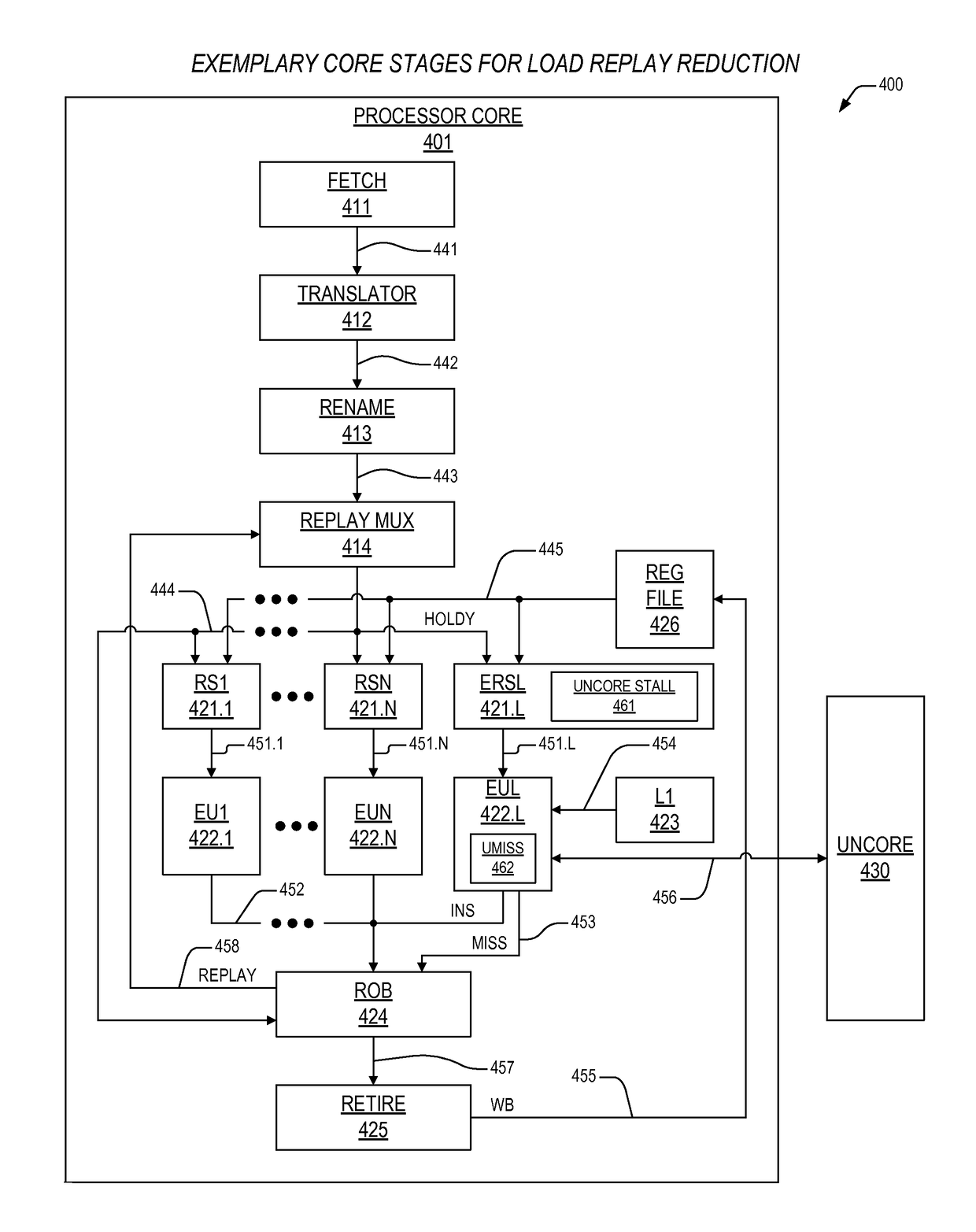

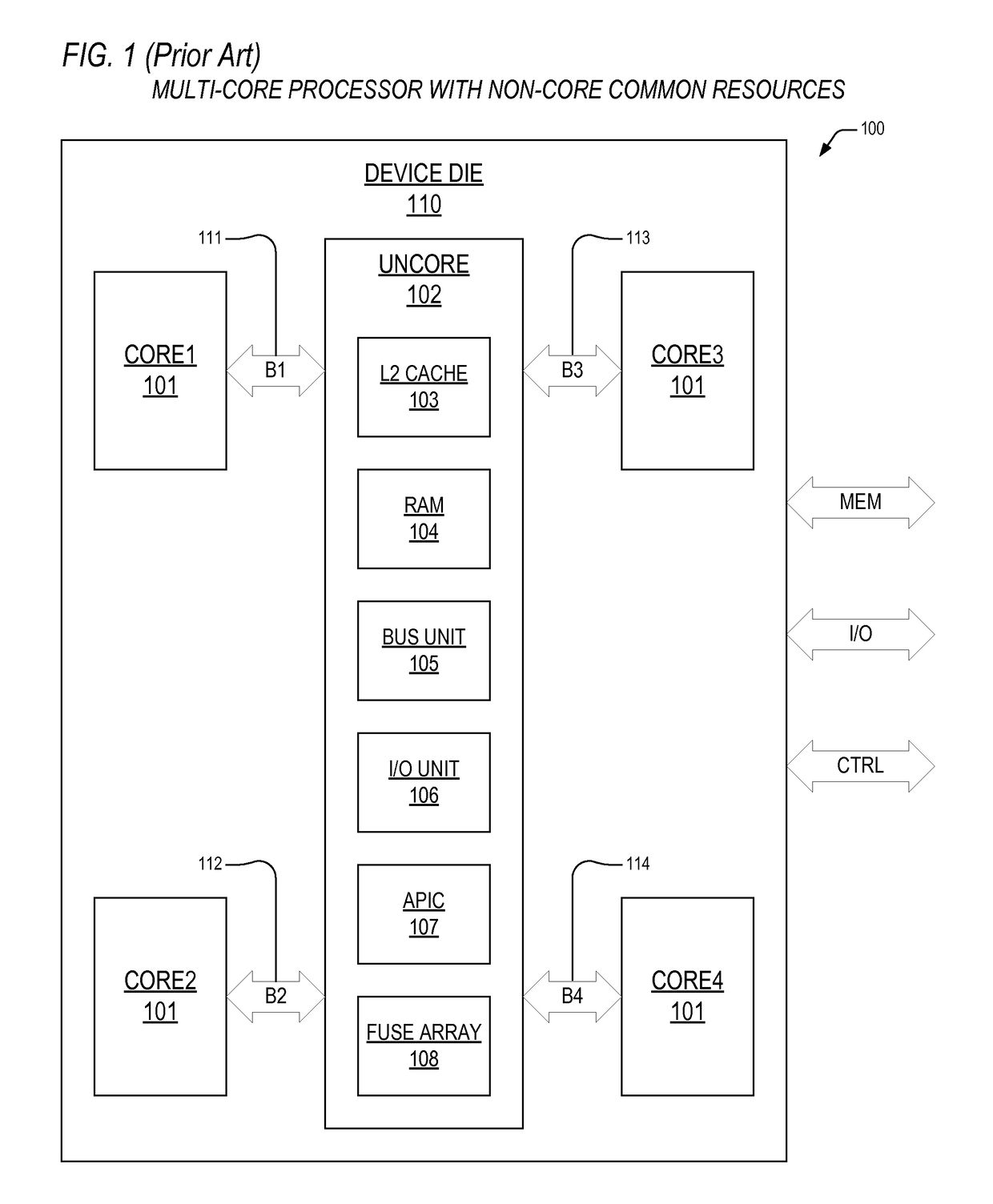

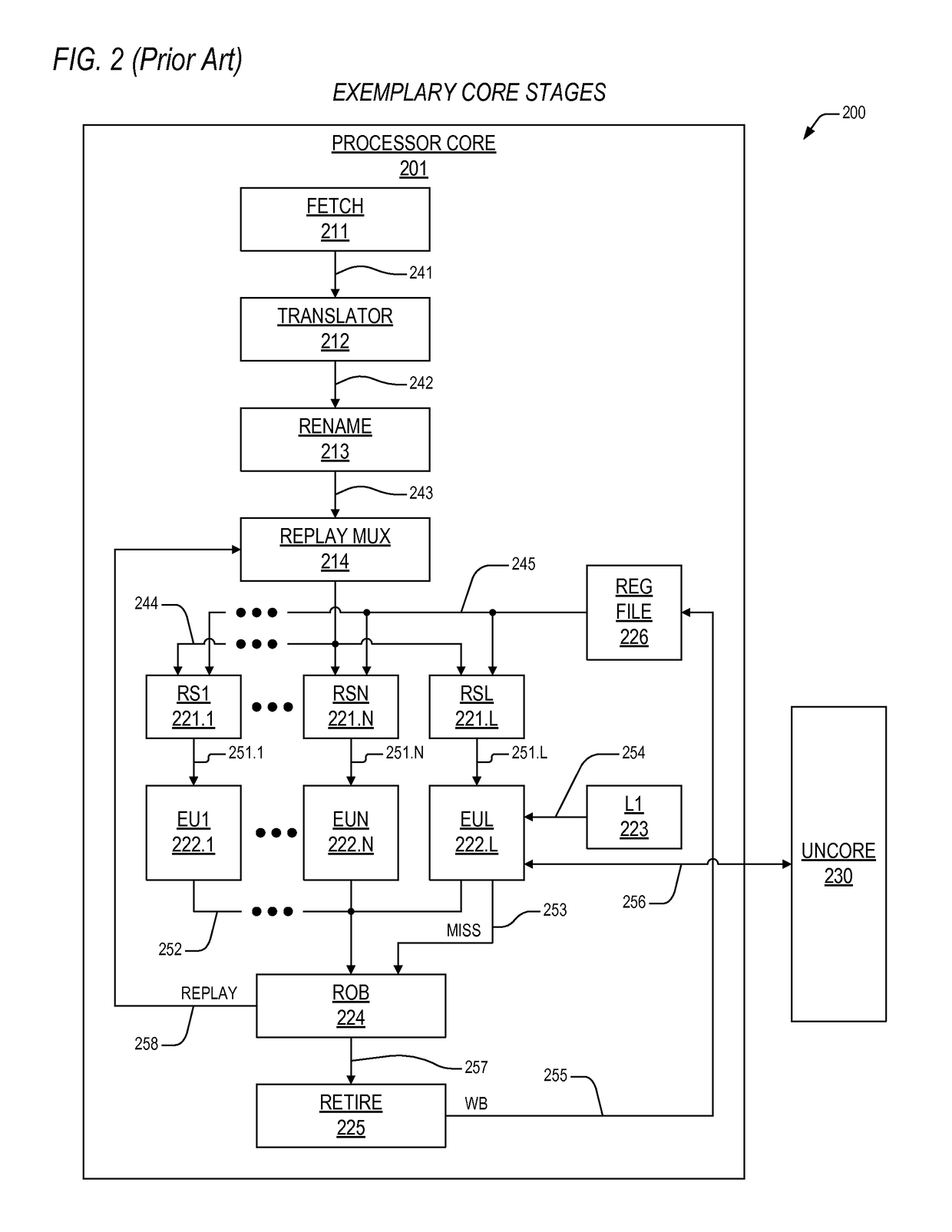

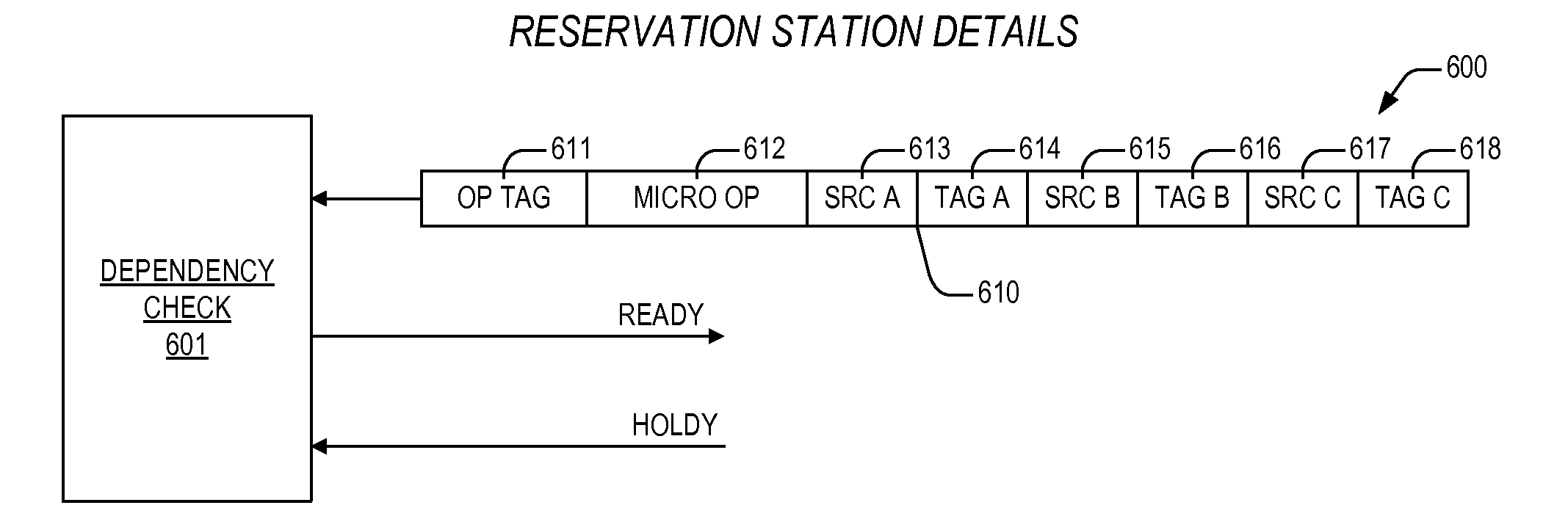

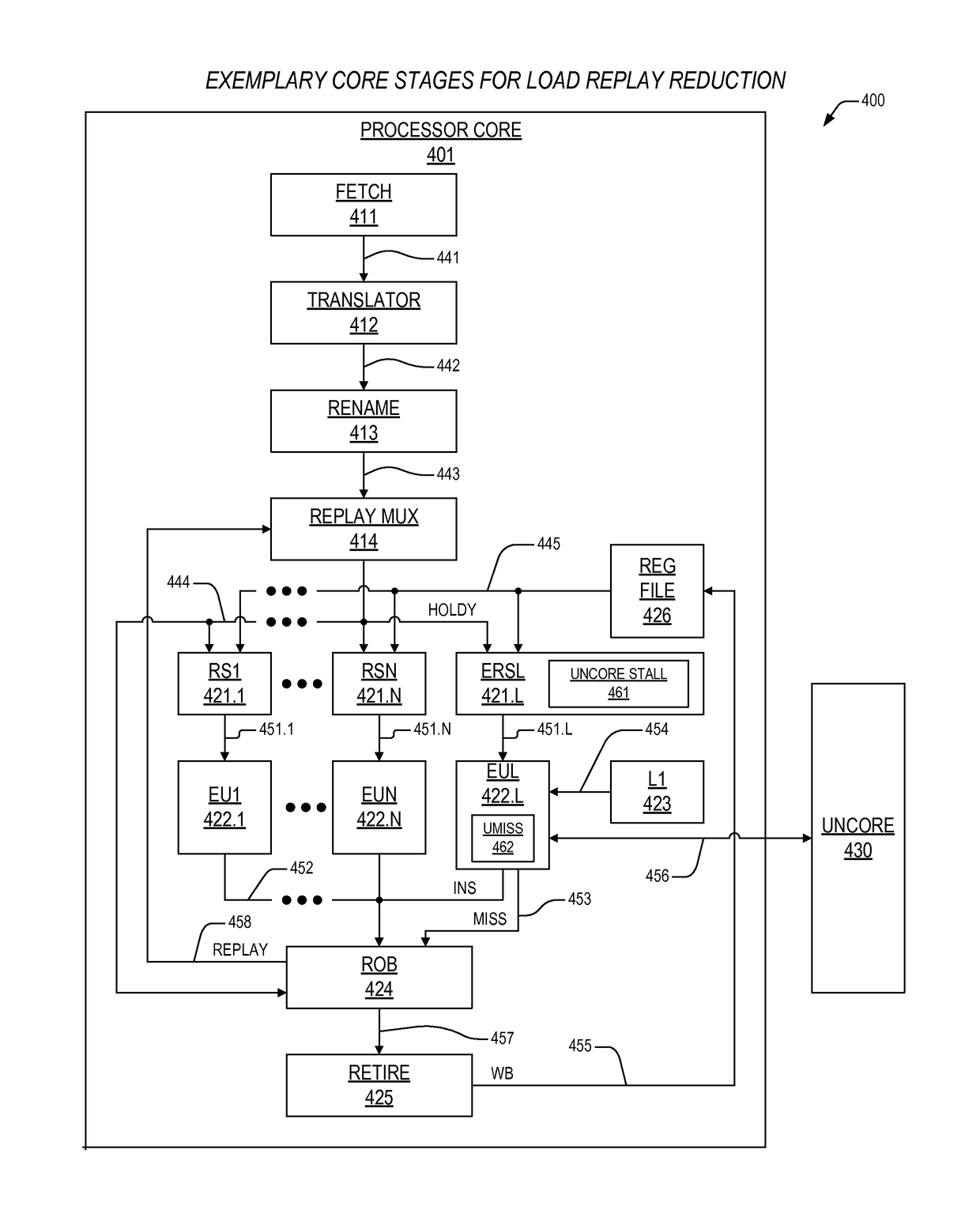

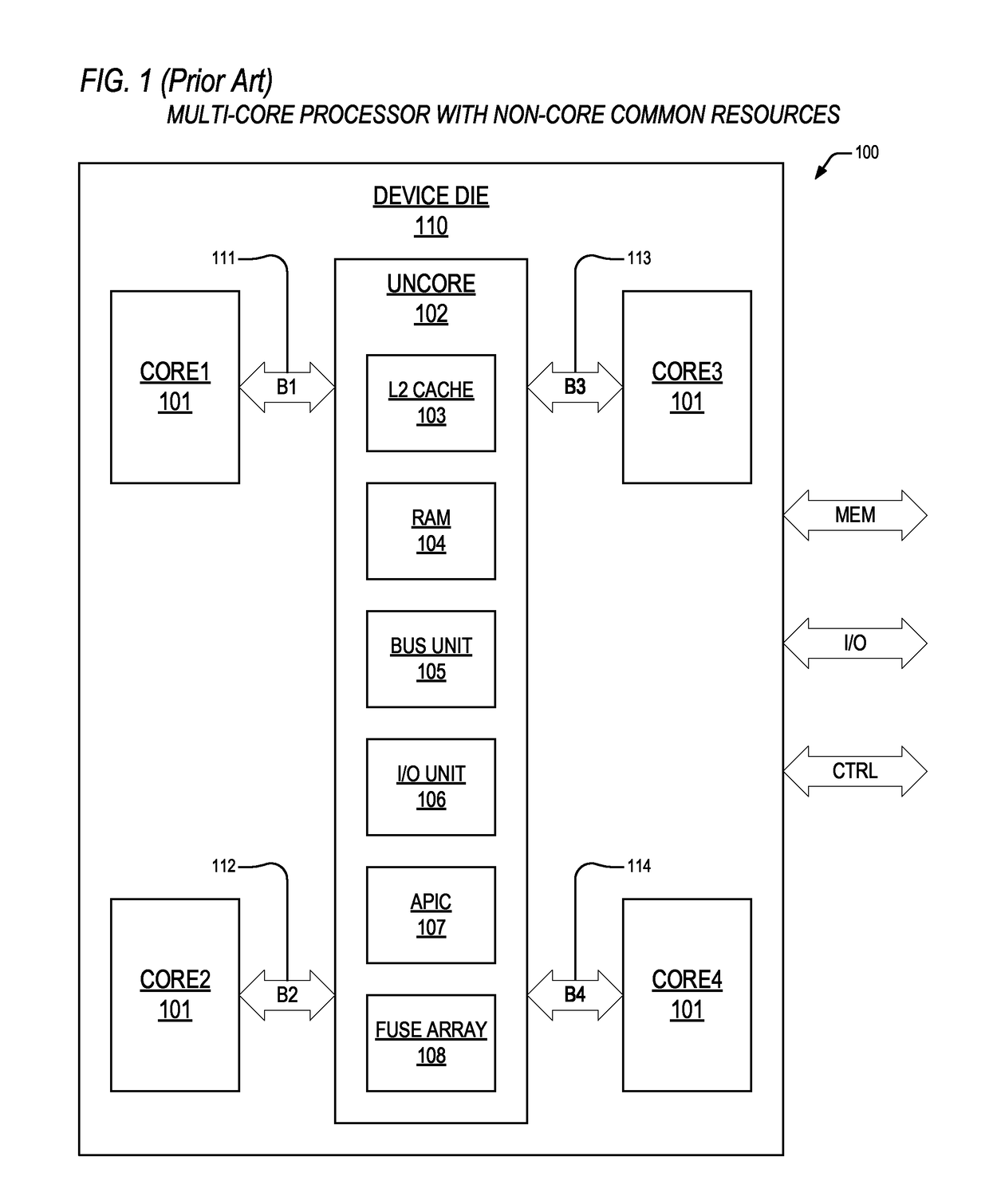

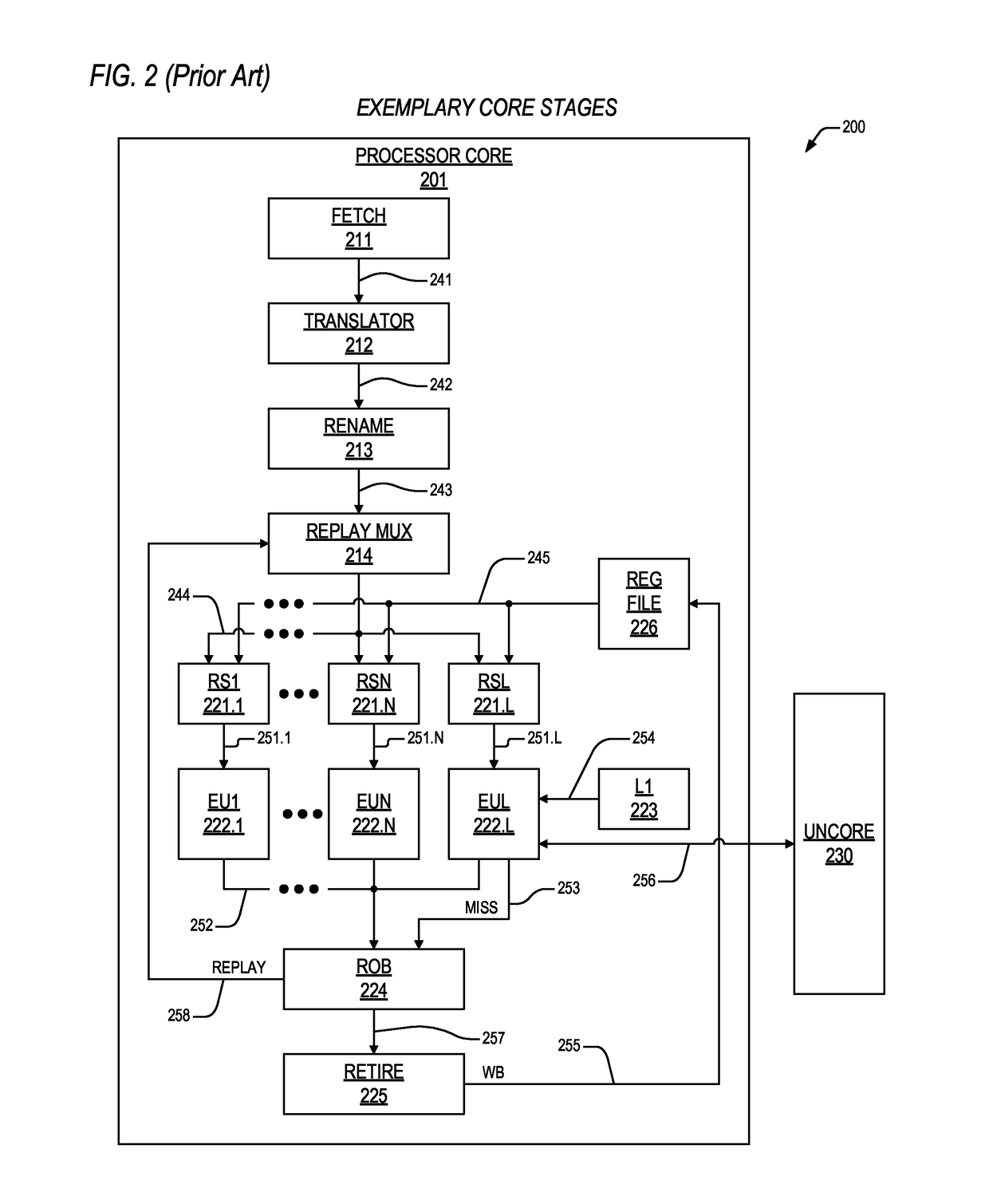

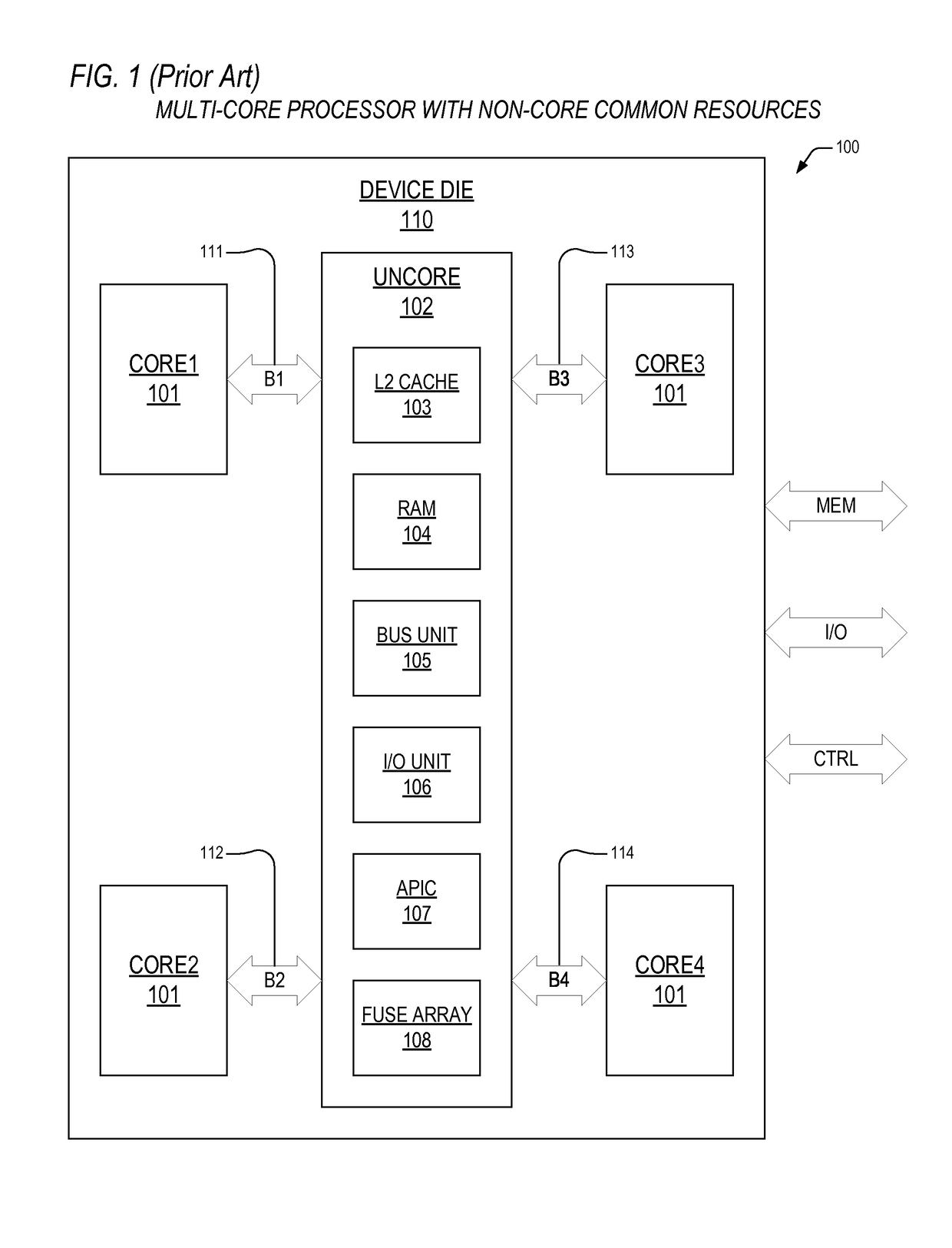

ActiveUS10114794B2Reducing replayDigital data processing detailsConcurrent instruction executionReservation stationProgrammable load

Owner:VIA ALLIANCE SEMICON CO LTD

Load replay precluding mechanism

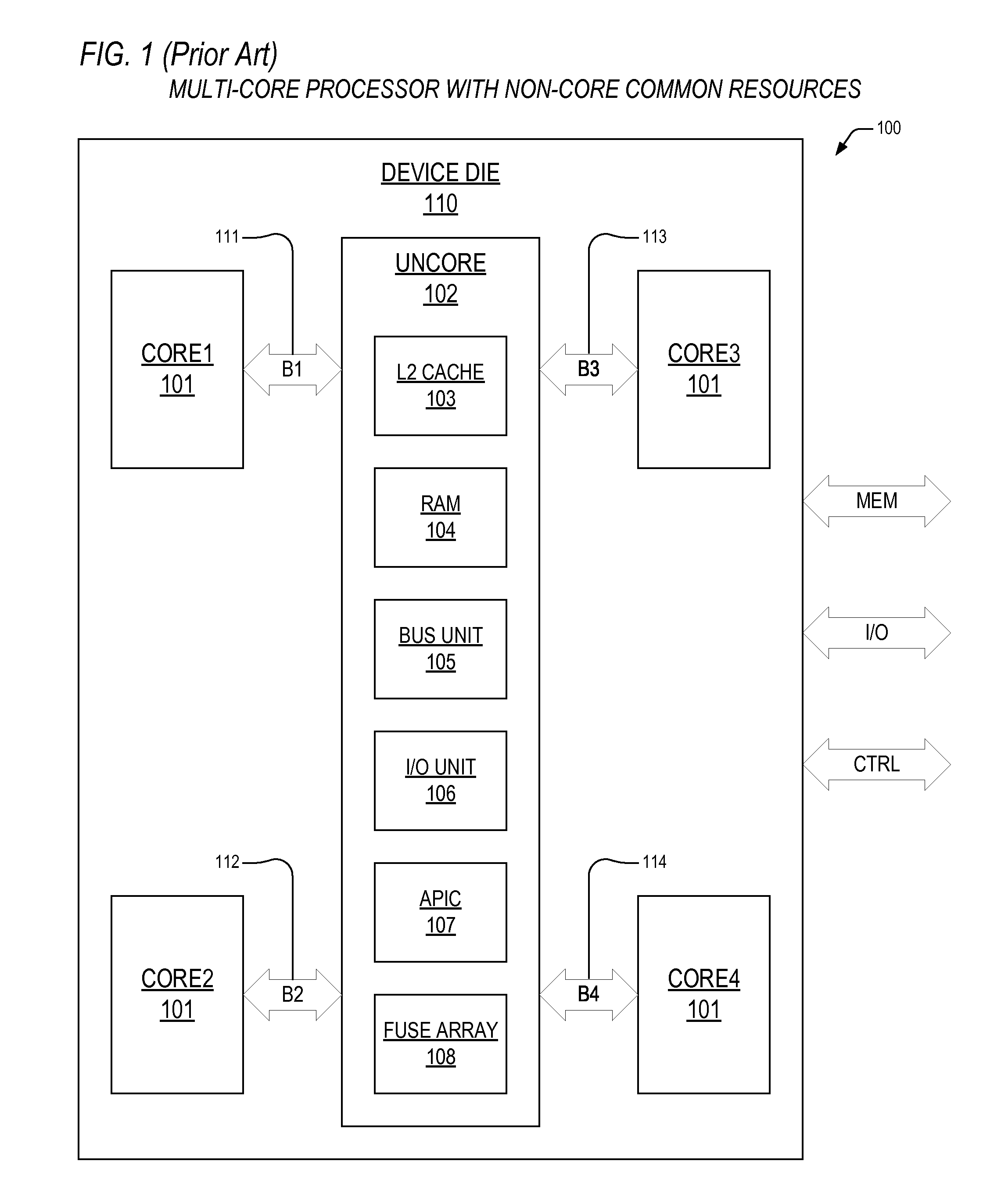

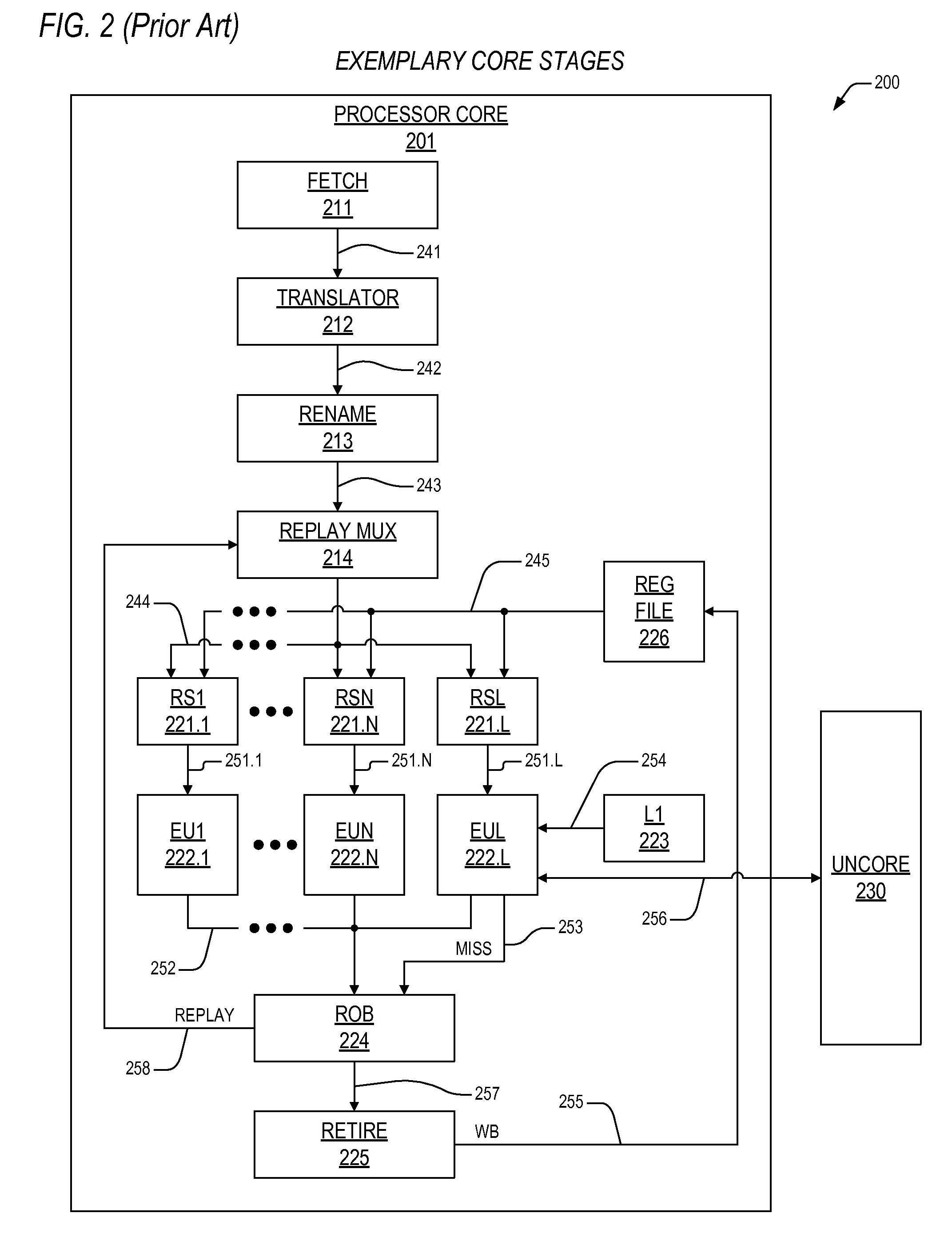

ActiveUS20160350119A1Reducing replayConcurrent instruction executionEnergy efficient computingReservation stationProgrammable Interrupt Controller

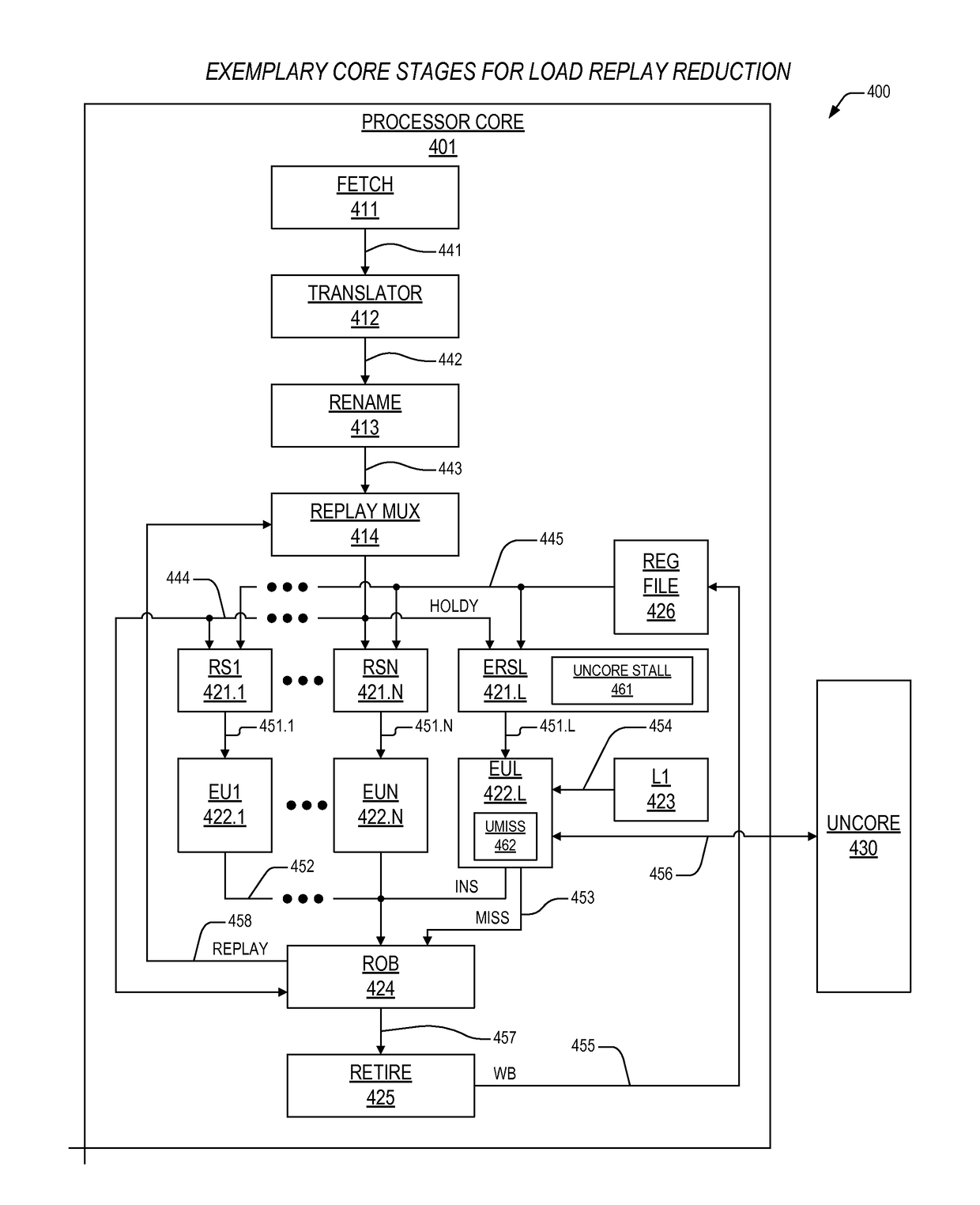

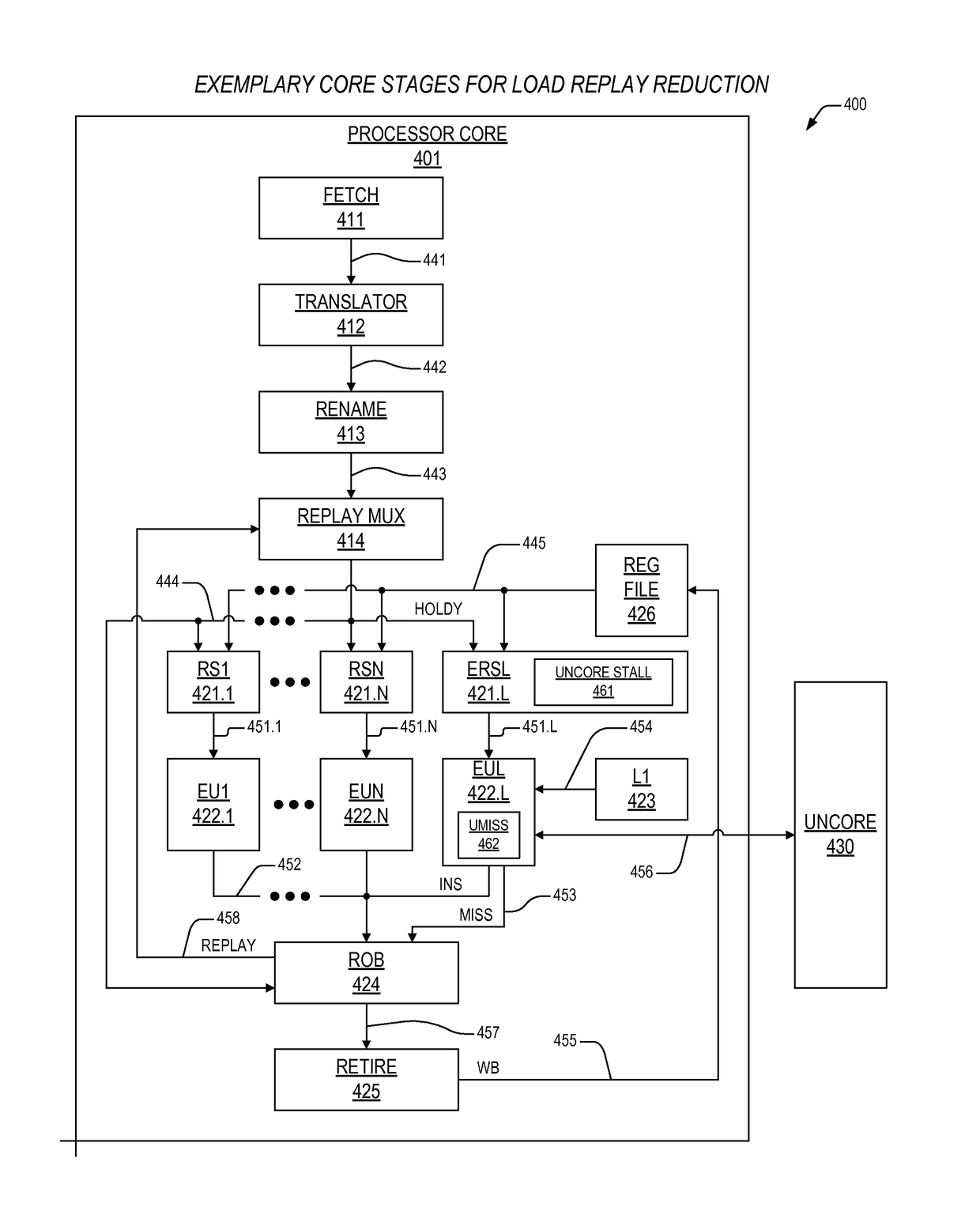

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include an advanced programmable interrupt controller (APIC), configured to perform interrupt operations.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on fuse array access in an out-of-order processor

ActiveUS20160170751A1Reducing replayVolume/mass flow measurementDigital computer detailsReservation stationEngineering

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include a fuse array that stores configuration data.

Owner:VIA ALLIANCE SEMICON CO LTD

Programmable load replay precluding mechanism

ActiveUS20160170757A1Reducing replayDigital computer detailsPower supply for data processingSpecified loadReservation station

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes a fuse array, configured to store the plurality of specified load instructions corresponding to the out-of-order processor which, upon initialization, accesses the fuse array to determine the plurality of specified load instructions.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on page walks in an out-of-order processor

ActiveUS10083038B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationMemory bus

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include a system memory that is accessed via a memory bus, the system memory comprising one or more page tables, configured to store one or more mappings between virtual addresses and physical addresses.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method to preclude non-core cache-dependent load replays in an out-of-order processor

ActiveUS10175984B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationOperand

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes an off-core cache memory, configured to store memory operands which may have been cached from a system memory that are not present in one or more on-core cache memories.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude I/O-dependent load replays in an out-of-order processor

ActiveUS10095514B2Reducing replayMemory architecture accessing/allocationDigital computer detailsReservation stationOperand

Owner:VIA ALLIANCE SEMICON CO LTD

Programmable load replay precluding mechanism

ActiveUS20160170766A1Reducing replayDigital data processing detailsMemory systemsReservation stationProgrammable load

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes a fuse array, configured to store the plurality of specified load instructions corresponding to the out-of-order processor which, upon initialization, accesses the fuse array to determine the plurality of specified load instructions.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method to preclude non-core cache-dependent load replays in an out-of-order processor

ActiveUS20160170760A1Reduce replayReducing replayDigital computer detailsPower supply for data processingEngineeringReservation station

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes an off-core cache memory, configured to store memory operands which may have been cached from a system memory that are not present in one or more on-core cache memories.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method to preclude load replays dependent on write combining memory space access in an out-of-order processor

ActiveUS10146540B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationMemory bus

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of prescribed resources includes system memory, coupled to the out-of-order processor via a memory bus, where the specified load micro instruction is known to resolve to write combining memory space in the system memory.

Owner:VIA ALLIANCE SEMICON CO LTD

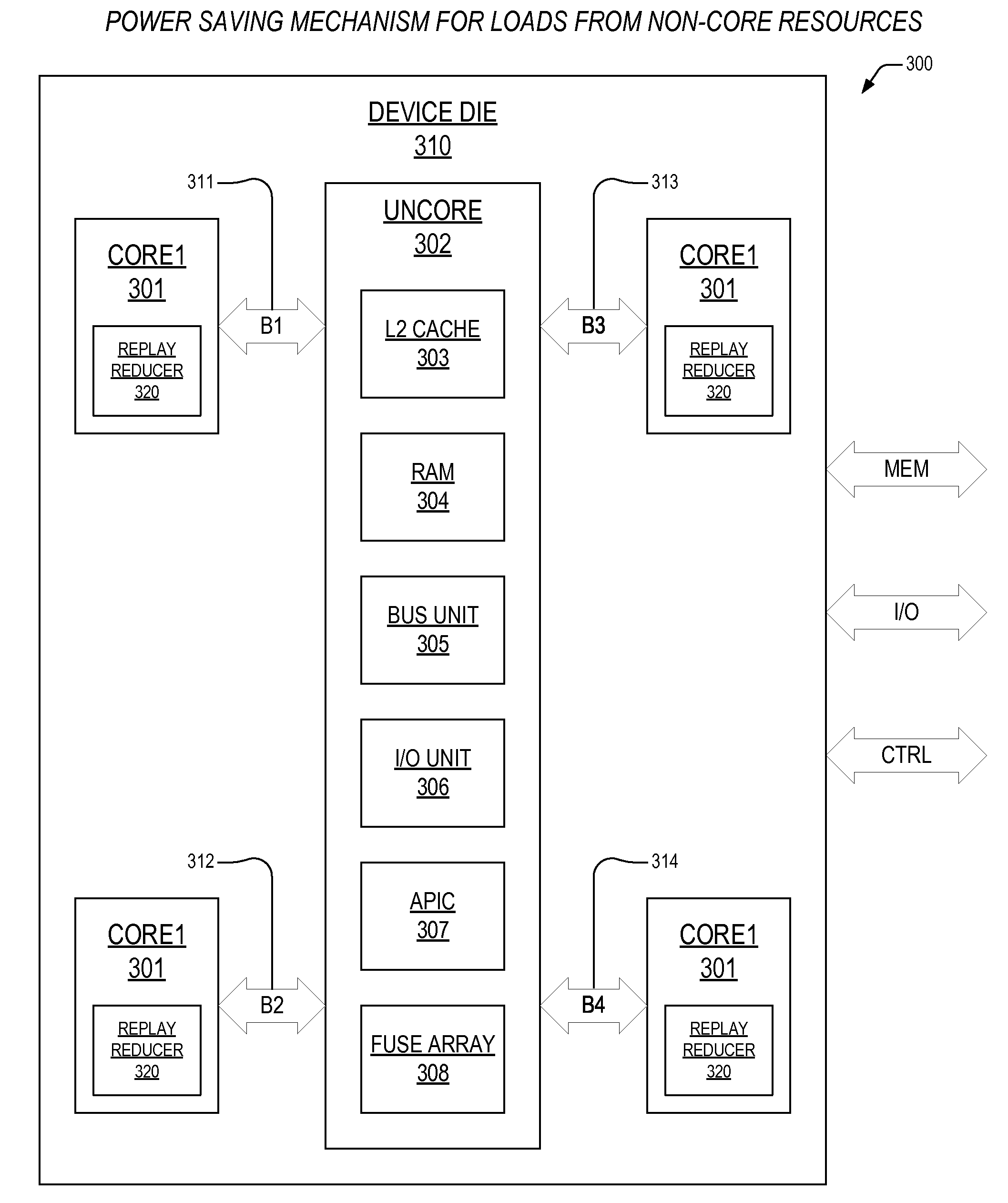

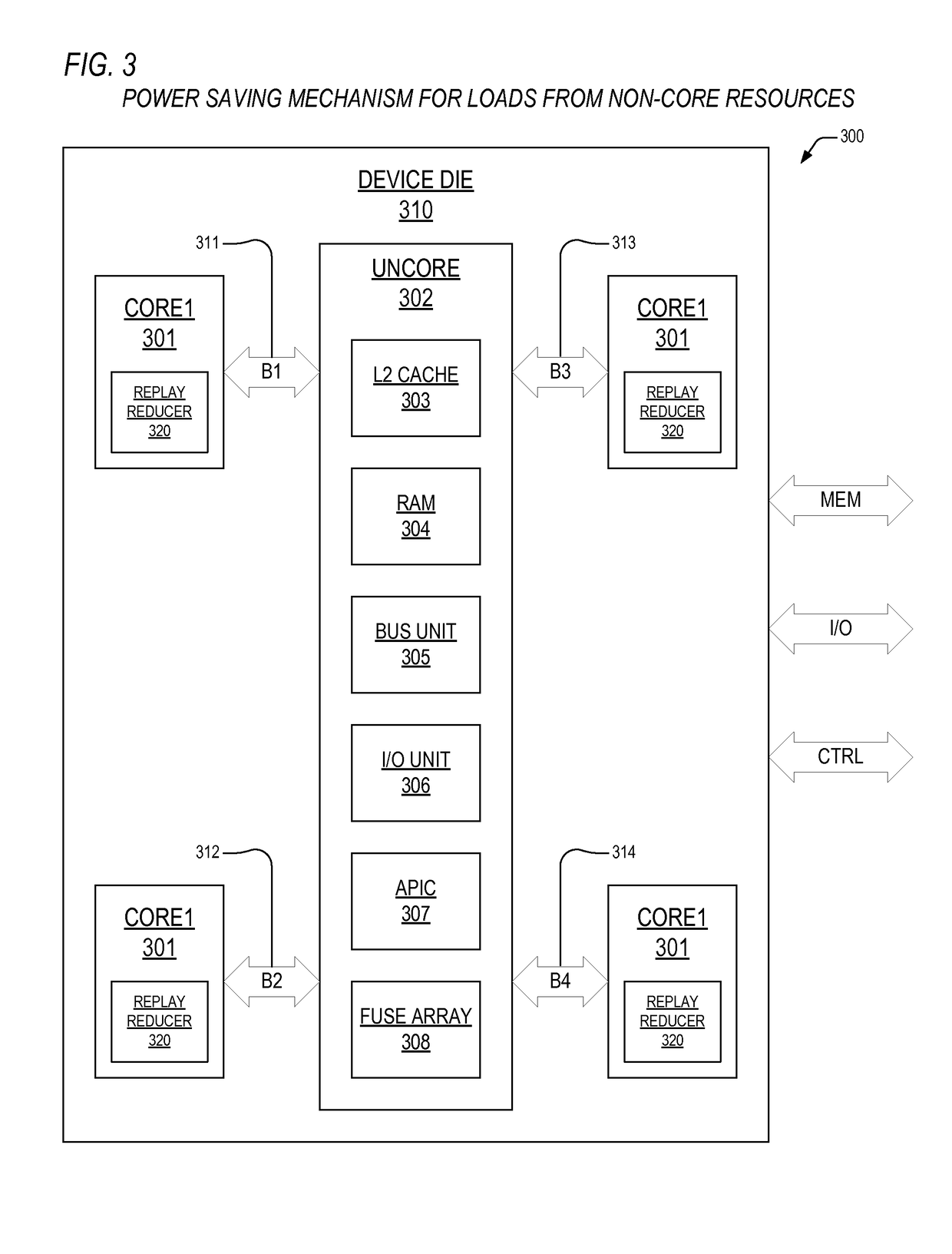

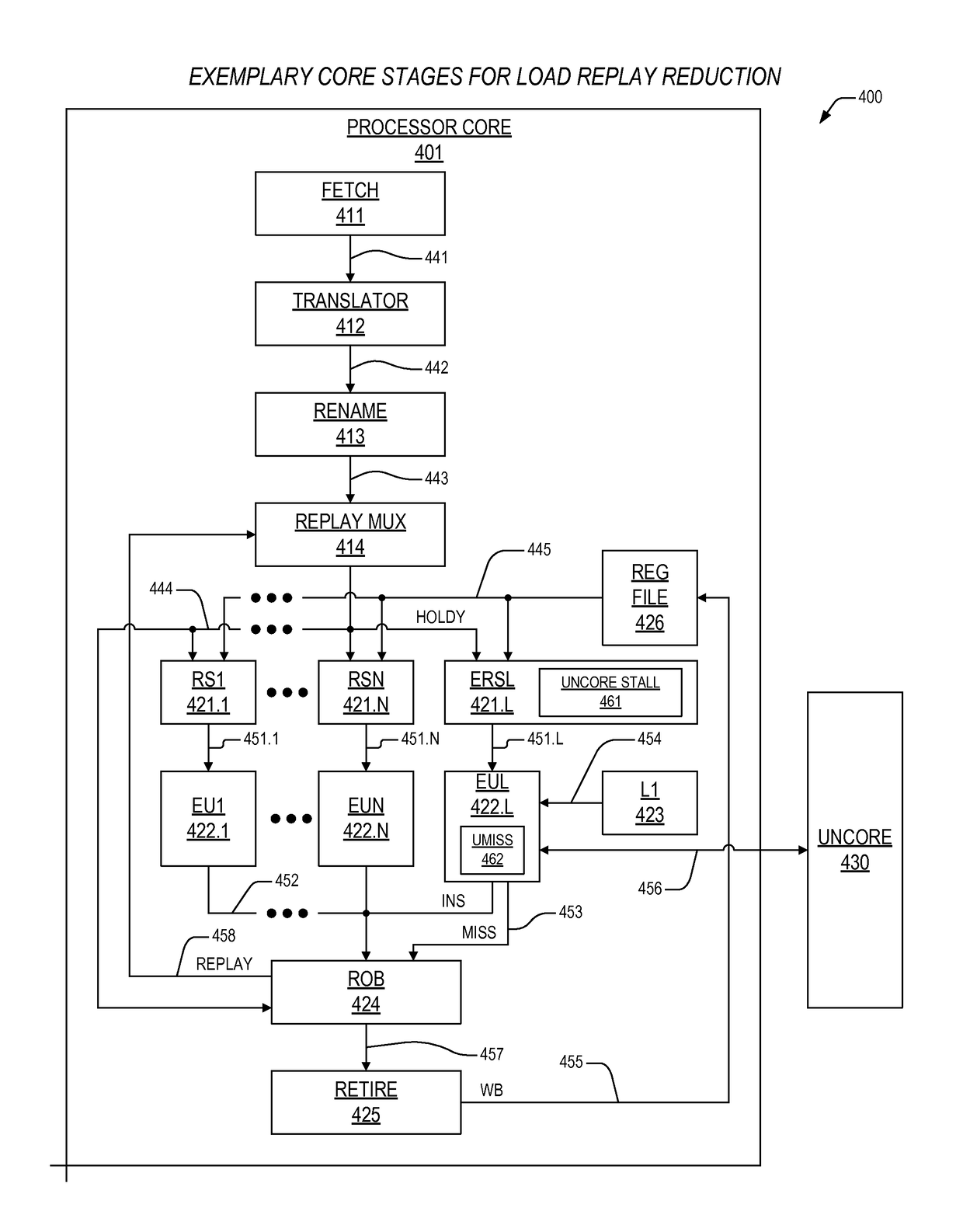

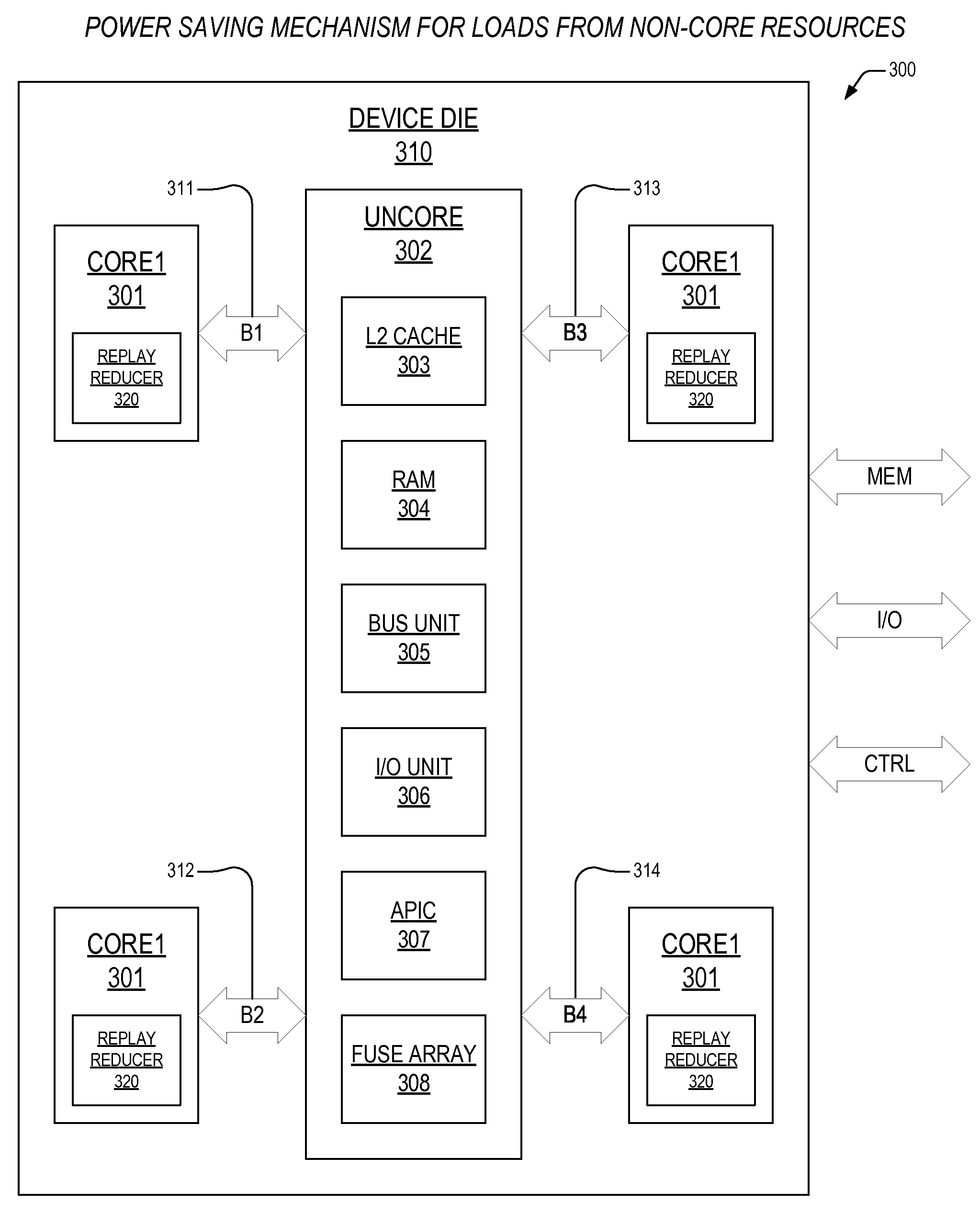

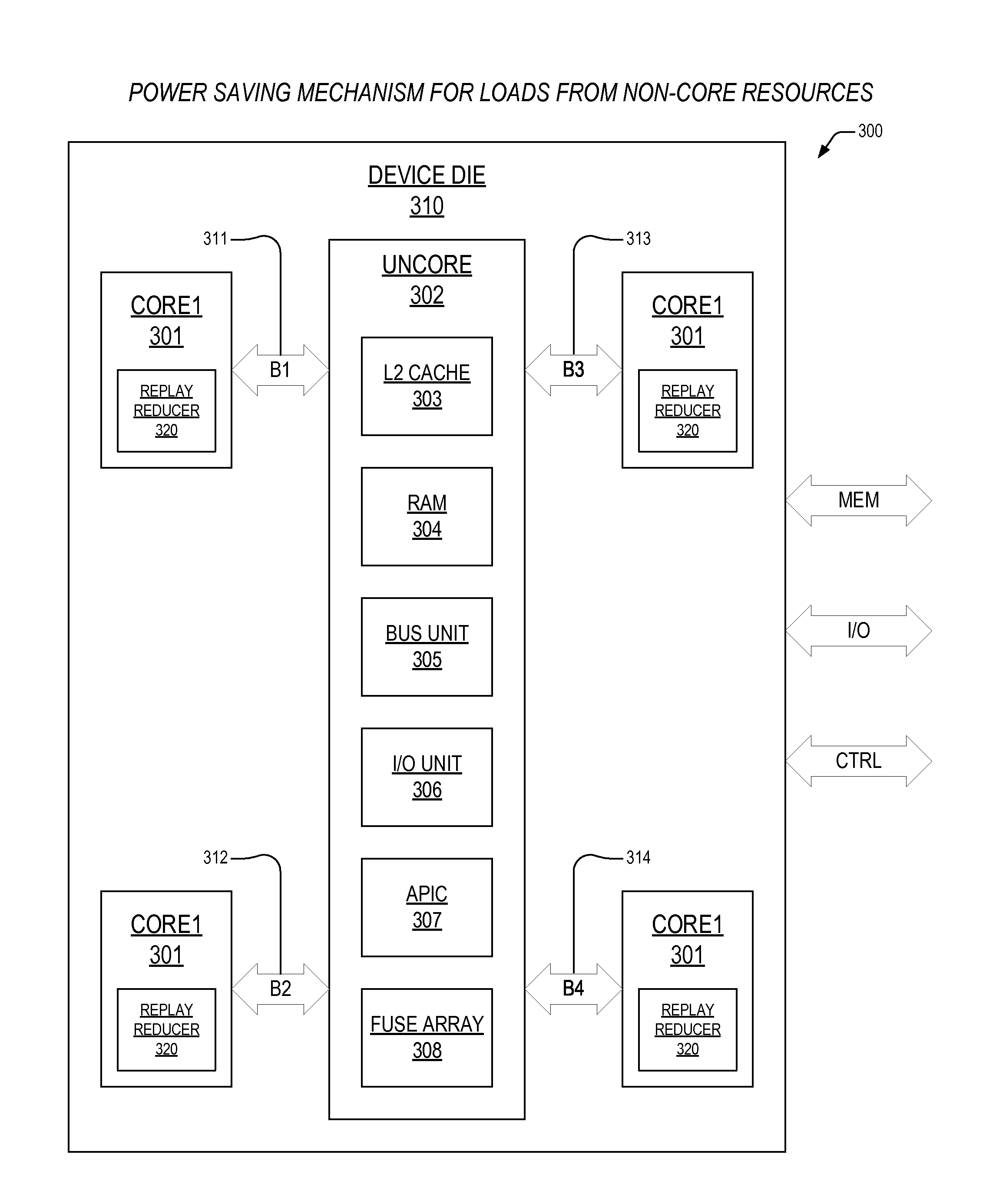

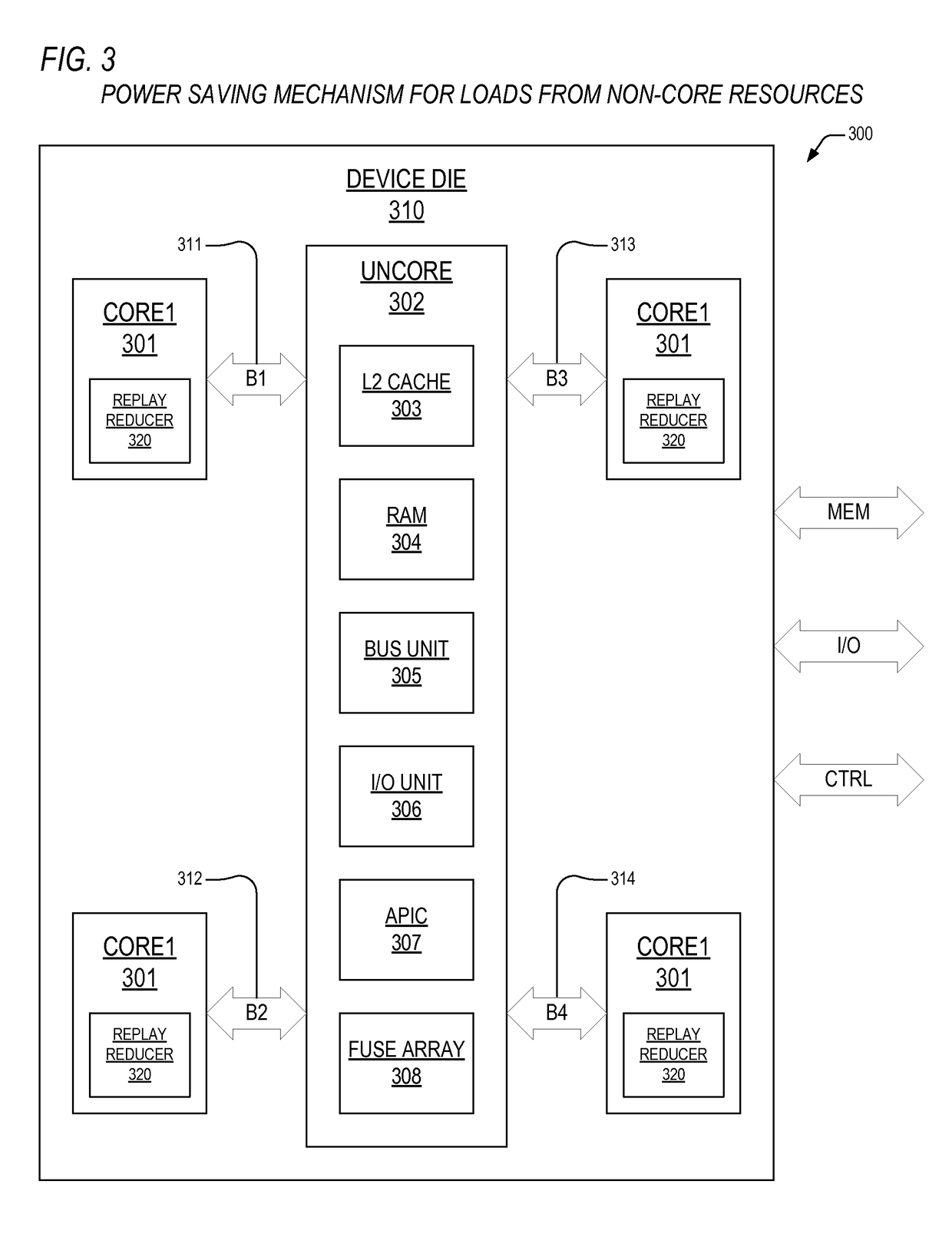

Power saving mechanism to reduce load replays in out-of-order processor

ActiveUS20160209910A1Reducing replayConcurrent instruction executionPower supply for data processingReservation stationOperand

An apparatus includes a first reservation station and a second reservation station. The first reservation station dispatches a first load micro instruction, and detects and indicates on a hold bus if the first load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the first load micro instruction for execution after a first number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the first load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the first load micro instruction has retrieved the operand.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method to preclude load replays dependent on write combining memory space access in an out-of-order processor

ActiveUS20160350122A1Reduce replayReducing replayConcurrent instruction executionSpecified loadReservation station

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of prescribed resources includes system memory, coupled to the out-of-order processor via a memory bus, where the specified load micro instruction is known to resolve to write combining memory space in the system memory.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method for programmable load replay preclusion

ActiveUS10209996B2Reducing replayResource allocationConcurrent instruction executionReservation stationRandom access memory

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes a random access memory, programmed via a Joint Test Action Group interface with the plurality of specified load instructions corresponding to the out-of-order processor which, upon initialization, accesses the random access memory to determine said plurality of specified load instructions.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method to preclude X86 special bus cycle load replays in an out-of-order processor

ActiveUS9804845B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationLoad instruction

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude shared ram-dependent load replays in an out-of-order processor

ActiveUS10108421B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationRandom access memory

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes a random access memory, configured to store microcode patches corresponding to the out-of-order processor which, upon initialization, accesses said random access memory to retrieve said microcode patches.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on page walks in an out-of-order processor

ActiveUS9645827B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationMemory bus

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include a system memory that is accessed via a memory bus, the system memory comprising one or more page tables, configured to store one or more mappings between virtual addresses and physical addresses.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on fuse array access in an out-of-order processor

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include a fuse array that stores configuration data.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude I/O-dependent load replays in an out-of-order processor

ActiveUS10088881B2Reducing replayVolume/mass flow measurementConcurrent instruction executionReservation stationOperand

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include an input / output (I / O) unit, configured to perform I / O operations via an I / O bus coupling an out-of-order processor to I / O resources.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on long load cycles in an out-of-order processor

ActiveUS10108420B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationLoad instruction

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory, where the specified load instruction requires more than a first number of clock cycles to retrieve the operand. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method to preclude x86 special bus cycle load replays in an out-of-order processor

ActiveUS20160170762A1Reducing replayDigital computer detailsPower supply for data processingLoad instructionReservation station

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory, where the specified load instruction comprises a load instruction resulting from execution of an x86 special bus cycle. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude shared RAM-dependent load replays in an out-of-order processor

ActiveUS10108429B2Reducing replayConcurrent instruction executionRedundant operation error correctionReservation stationRandom access memory

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes a random access memory, configured to store microcode patches corresponding to the out-of-order processor which, upon initialization, accesses said random access memory to retrieve said microcode patches.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude uncacheable-dependent load replays in out-of-order processor

ActiveUS10127046B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationMemory bus

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on page walks in an out-of-order processor

ActiveUS20160170755A1Reducing replayDigital computer detailsPower supply for data processingSpecified loadPage table

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include a system memory that is accessed via a memory bus, the system memory comprising one or more page tables, configured to store one or more mappings between virtual addresses and physical addresses.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on off-die control element access in an out-of-order processor

ActiveUS10108430B2Reducing replayConcurrent instruction executionSingle machine energy consumption reductionReservation stationOperand

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on off-die control element access in an out-of-order processor

ActiveUS10120689B2Reducing replayConcurrent instruction executionPower supply for data processingReservation stationOperand

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The plurality of non-core resources includes a control element, coupled to the out-of order processor via a control bus.

Owner:VIA ALLIANCE SEMICON CO LTD

Load replay precluding mechanism

ActiveUS10146546B2Reducing replayConcurrent instruction executionEnergy efficient computingReservation stationProgrammable Interrupt Controller

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include an advanced programmable interrupt controller (APIC), configured to perform interrupt operations.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on long load cycles in an out-of-order processor

ActiveUS10108428B2Reducing replayResource allocationConcurrent instruction executionLoad instructionReservation station

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory, where the specified load instruction requires more than a first number of clock cycles to retrieve the operand. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand.

Owner:VIA ALLIANCE SEMICON CO LTD

Apparatus and method to preclude non-core cache-dependent load replays in an out-of-order processor

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude load replays dependent on fuse array access in an out-of-order processor

ActiveUS10089112B2Reducing replayVolume/mass flow measurementConcurrent instruction executionReservation stationOperand

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include a fuse array that stores configuration data.

Owner:VIA ALLIANCE SEMICON CO LTD

Mechanism to preclude uncacheable-dependent load replays in out-of-order processor

ActiveUS20160170753A1Reducing replayVolume/mass flow measurementDigital computer detailsReservation stationMemory bus

An apparatus including first and second reservation stations. The first reservation station dispatches a load micro instruction, and indicates on a hold bus if the load micro instruction is a specified load micro instruction directed to retrieve an operand from a prescribed resource other than on-core cache memory. The second reservation station is coupled to the hold bus, and dispatches one or more younger micro instructions therein that depend on the load micro instruction for execution after a number of clock cycles following dispatch of the first load micro instruction, and if it is indicated on the hold bus that the load micro instruction is the specified load micro instruction, the second reservation station is configured to stall dispatch of the one or more younger micro instructions until the load micro instruction has retrieved the operand. The resources include system memory, coupled an out-of-order processor via a memory bus.

Owner:VIA ALLIANCE SEMICON CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com