Sram cell fabrication with interlevel Dielectric planarization

a technology of dielectric planarization and sram cell, which is applied in the direction of electrical equipment, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of high-temperature data loss of cells and excess static power consumption, and achieve accurate poly resistor patterning, reduce topography, and improve the degree of planarization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019]The numerous innovative teachings of the present application will be described with particular reference to the presently preferred embodiment. However, it should be understood that this class of embodiments provides only a few examples of the many advantageous uses of the innovative teachings herein. In general, statements made in the specification of the present application do not necessarily delimit any of the various claimed inventions. Moreover, some statements may apply to some inventive features but not to others.

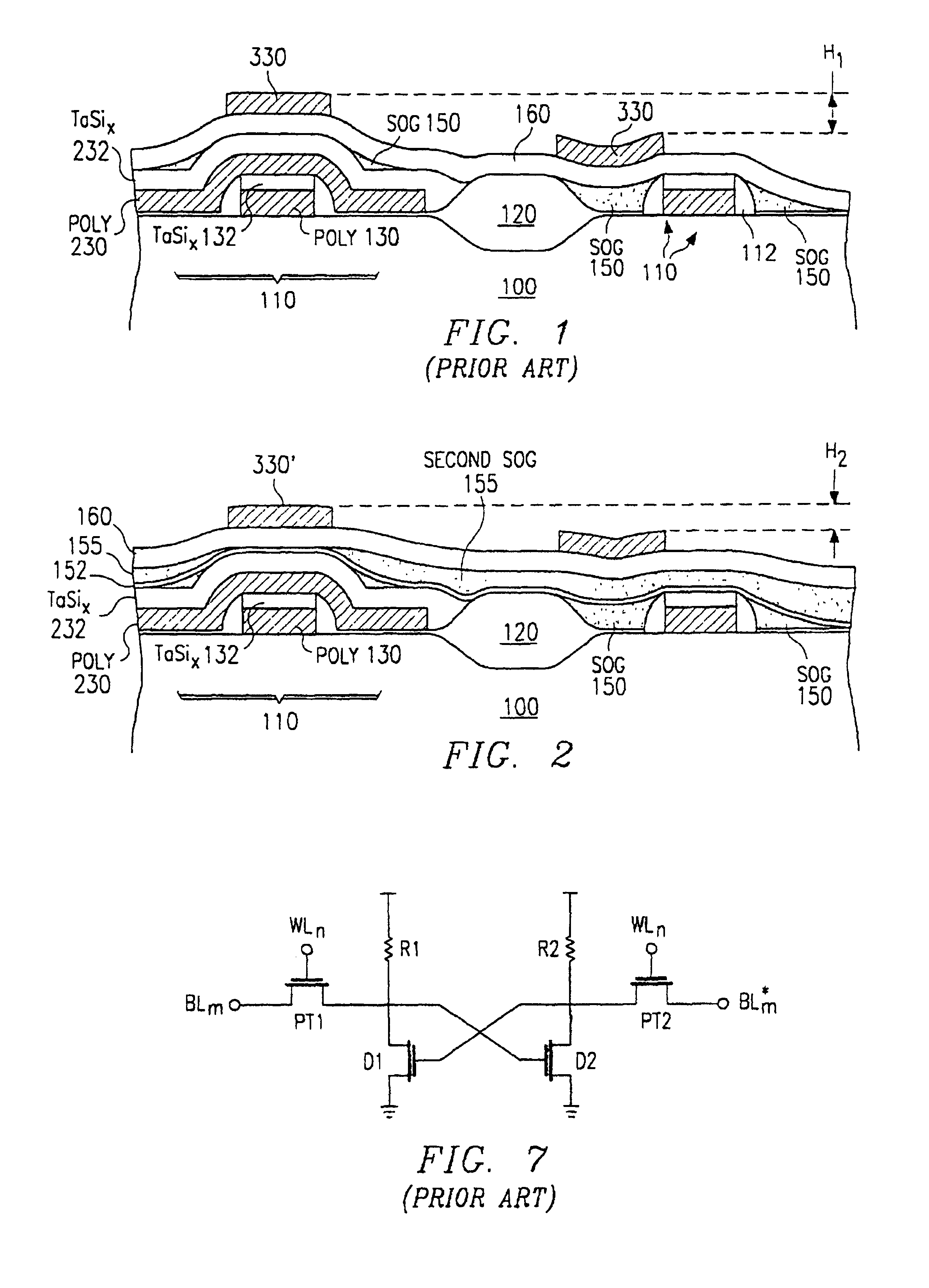

[0020]After completion of CMOS transistor formation (and local interconnect formation in the poly-2 layer, if desired), a standard process flow (as shown in FIG. 1) would deposit e.g. 1KÅ of undoped oxide, spin on e.g. 1.5KÅ of SOG, deposit e.g. 1KÅ of undoped oxide, deposit and etch a second polysilicon layer to form polysilicon resistors, and then proceed with contact and metal formation.

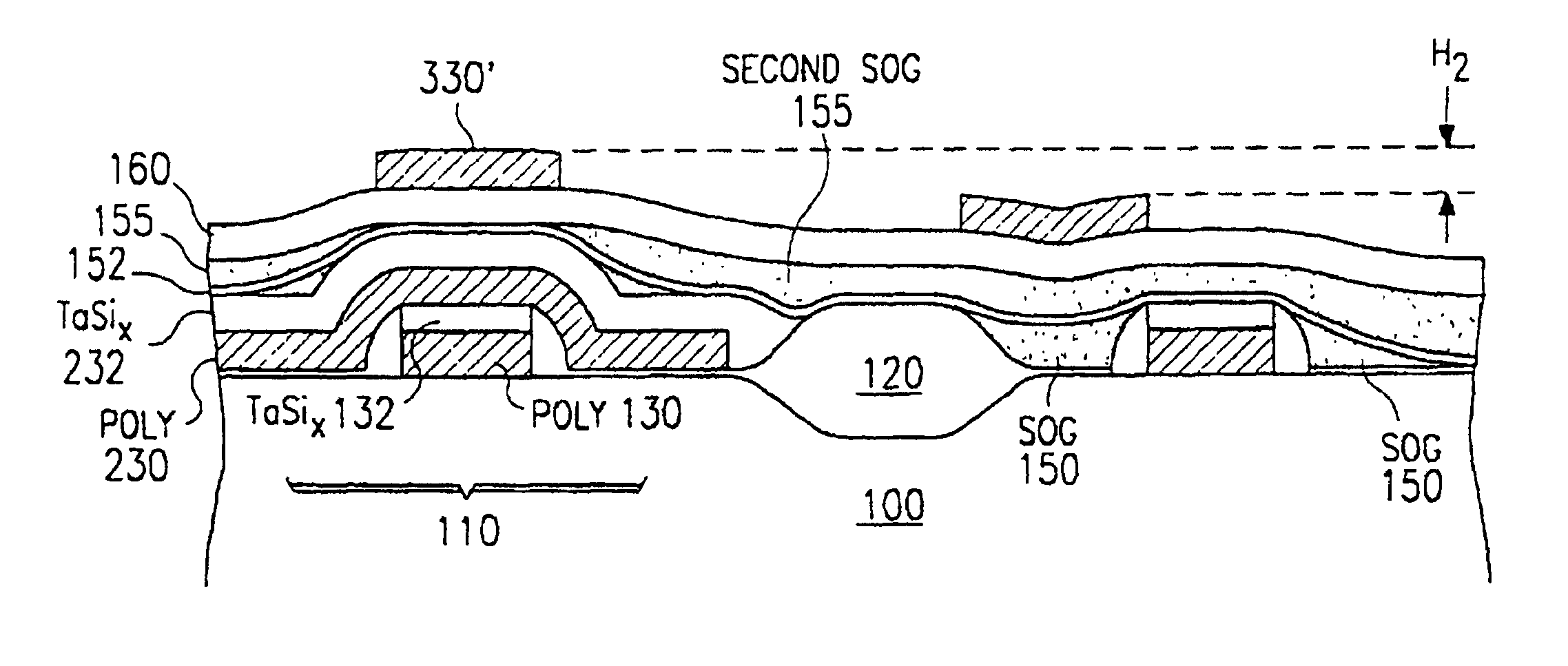

[0021]In the innovative process embodiments described, fabrication of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com