Printability verification by progressive modeling accuracy

a printing accuracy and progressive modeling technology, applied in the field of optical lithography, can solve the problems of complex opc methodologies, ever increasing cost of mask manufacturing and inspection, and ever increasing complexity of opc and ret, and achieve the effect of efficient computation of printability verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

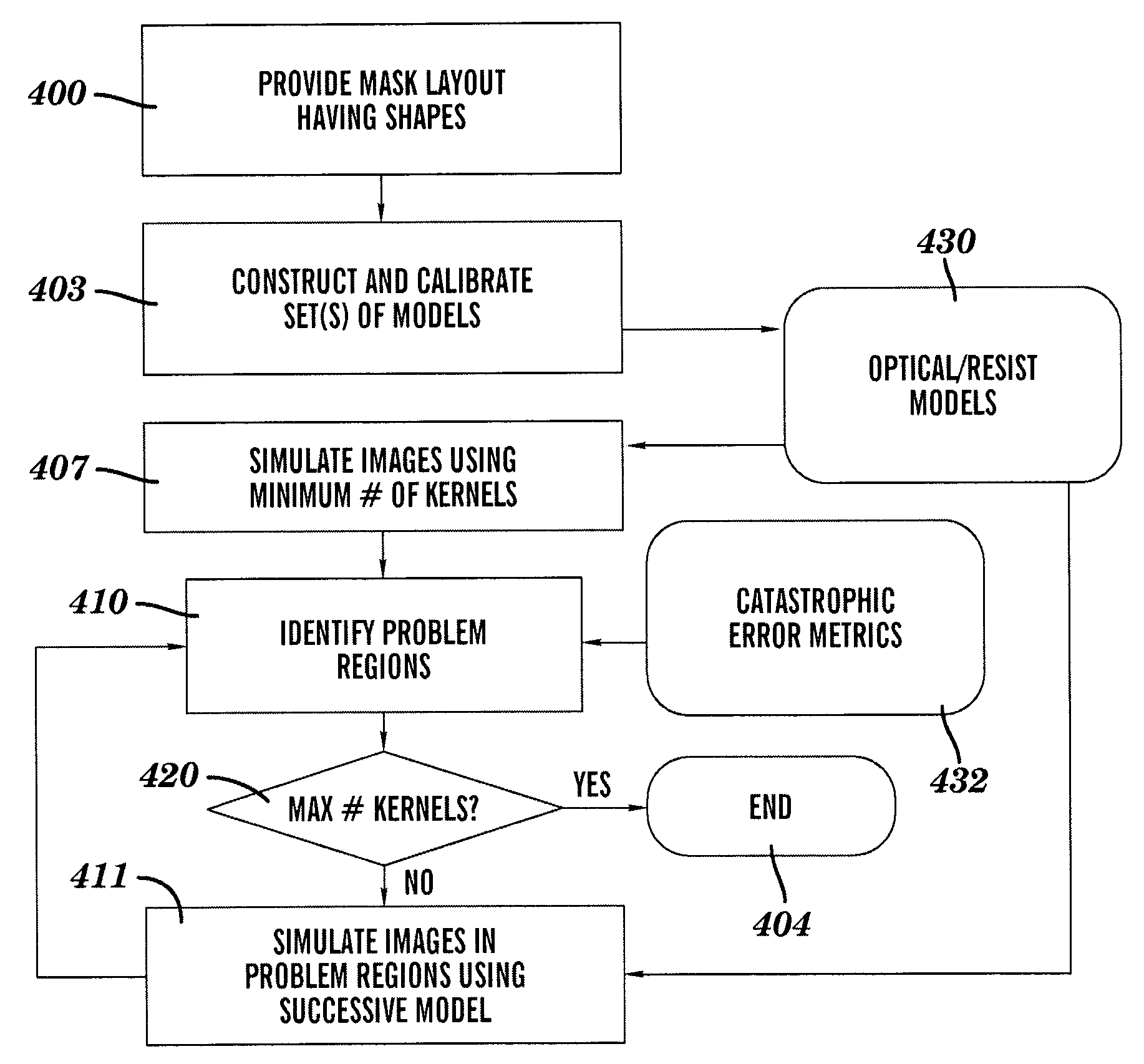

[0045]In describing the preferred embodiment of the present invention, reference will be made herein to FIGS. 1-16 in which like numerals refer to like features of the invention. The figures are not necessarily drawn to scale.

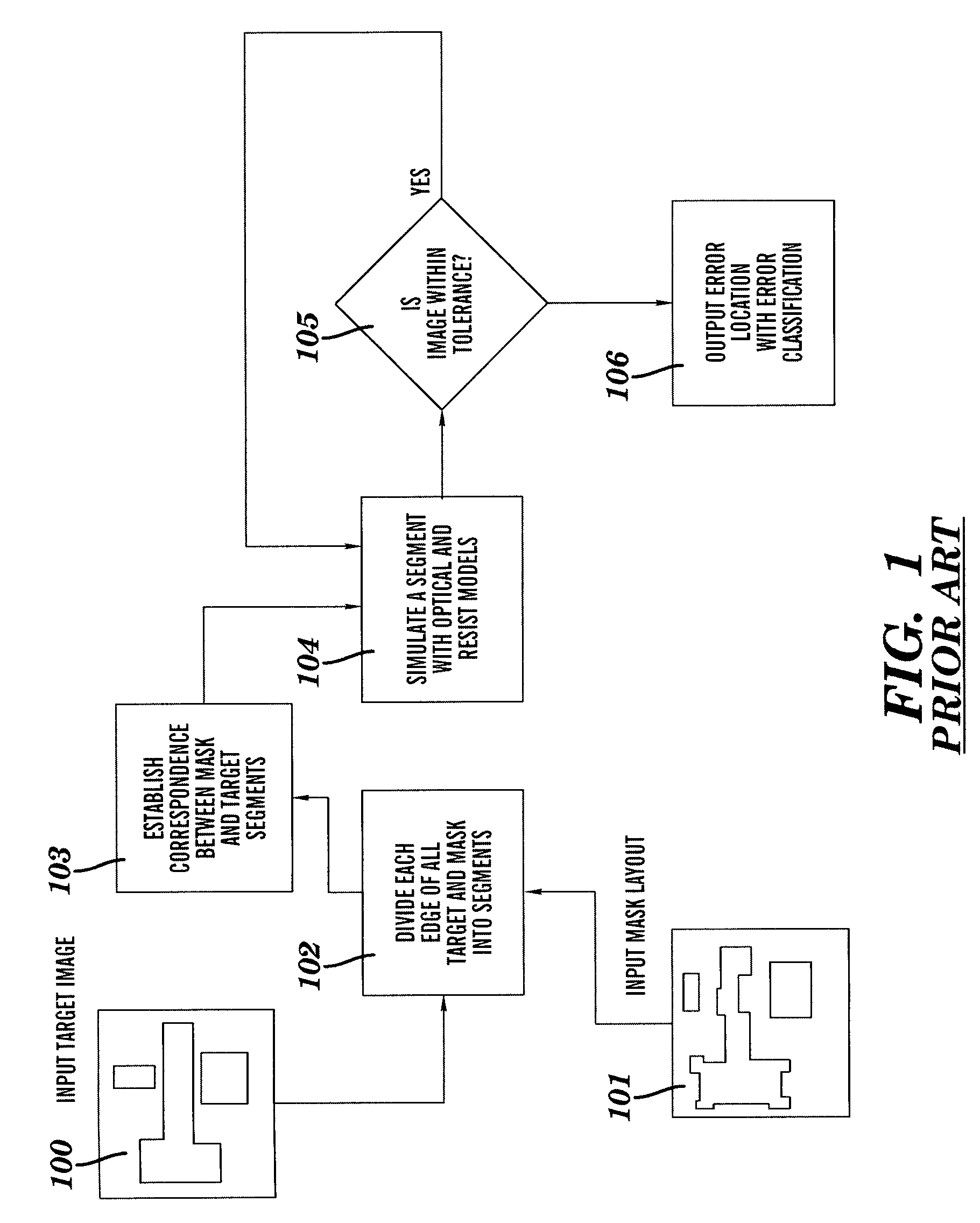

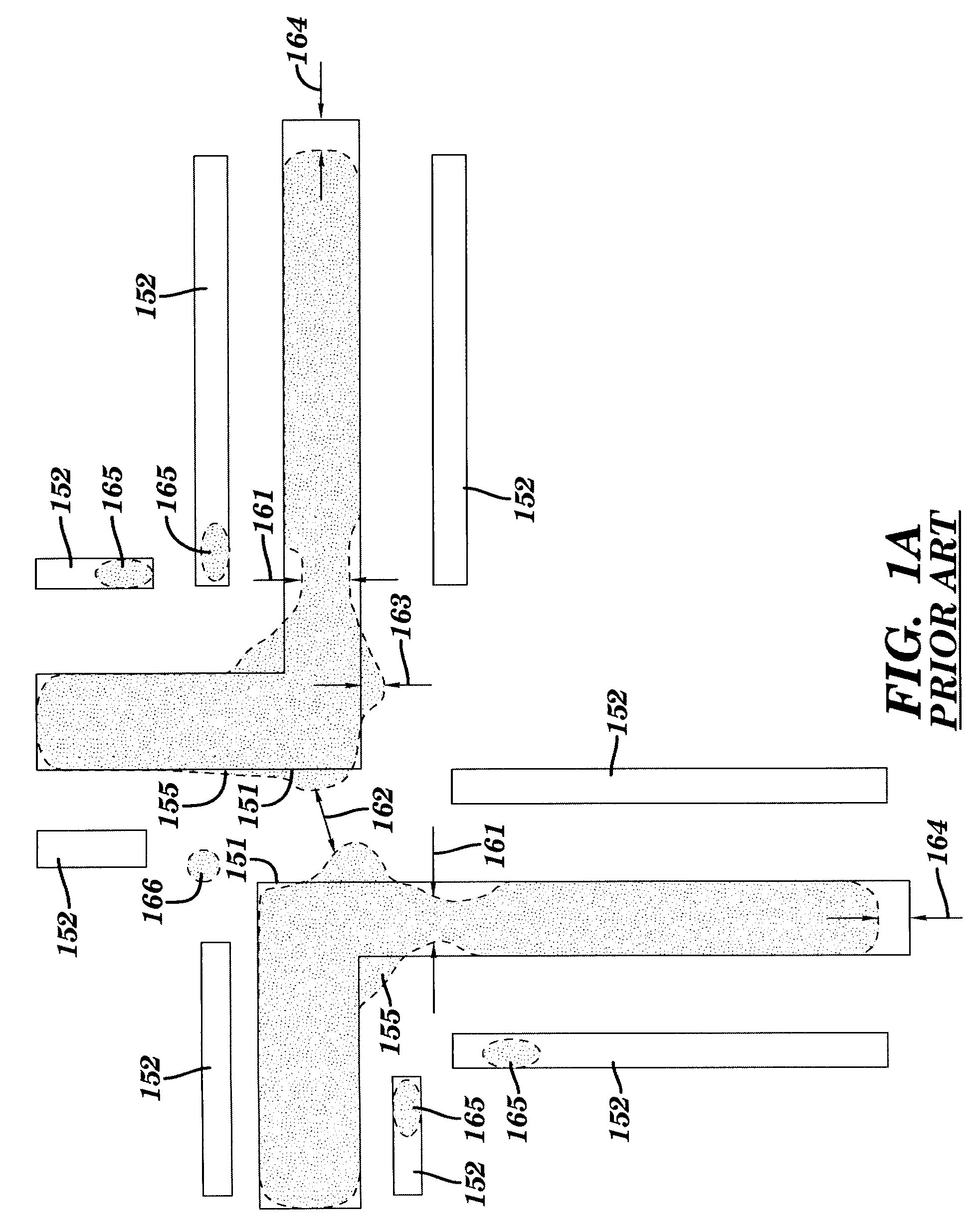

[0046]Catastrophic Print Errors

[0047]A typical printability verification methodology is illustrated in FIG. 1. The input to a conventional printability verification procedure includes one or more input mask layouts 101 typically resulting after application of RET and / or OPC to the initial mask layout. A target wafer image 100 is also provided as an input. In the next step (Block 102) all the target and mask shapes are typically divided into edge segments, and then (Block 103), a correspondence is established between each mask and target shape segments. In the next step (Block 104), the formation of the wafer image segment corresponding to each mask segment is simulated using a calibrated resist and optical model. The simulated wafer segment is then compared aga...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com