Address generators for mapping arrays in bit reversed order

a technology of address generator and array, applied in the field of address generator for mapping array in bit reversed order, can solve the problems of inefficiency of conventional ipbr method, inability to justify additional data memory requirements of oopbr, hidden cycle penalties of fft using oopbr, etc., and achieve the effect of reducing oopbr cycles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

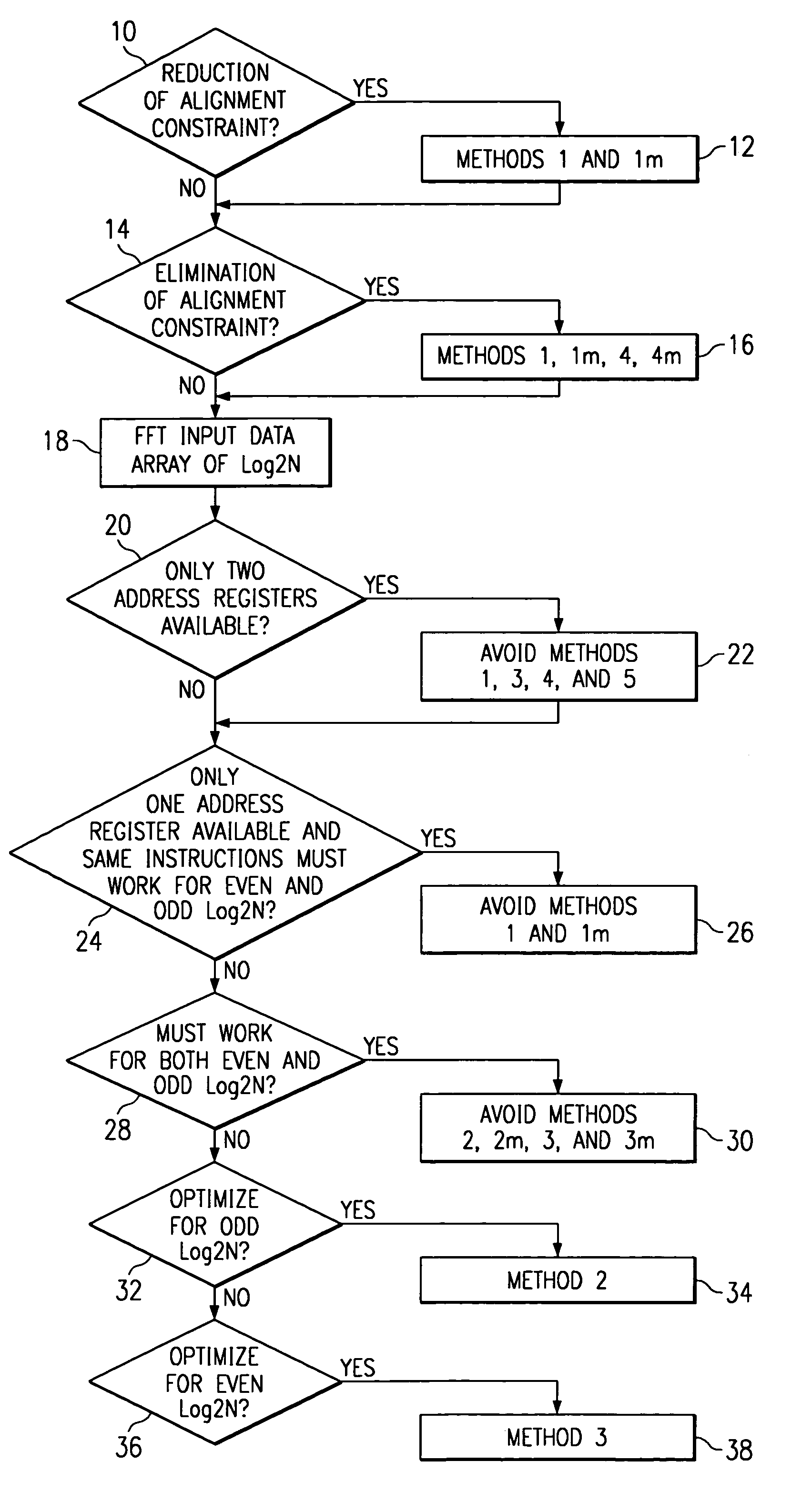

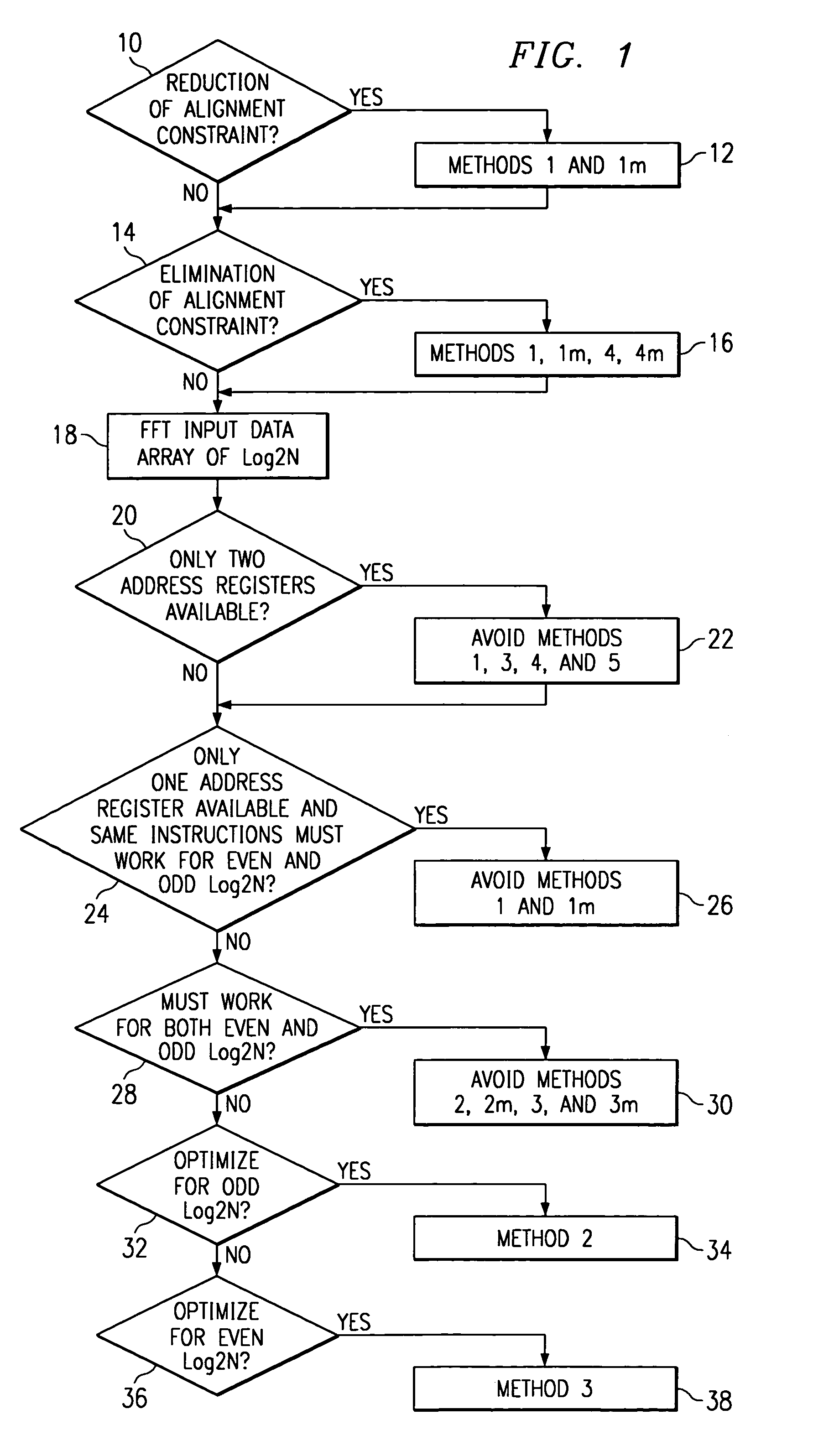

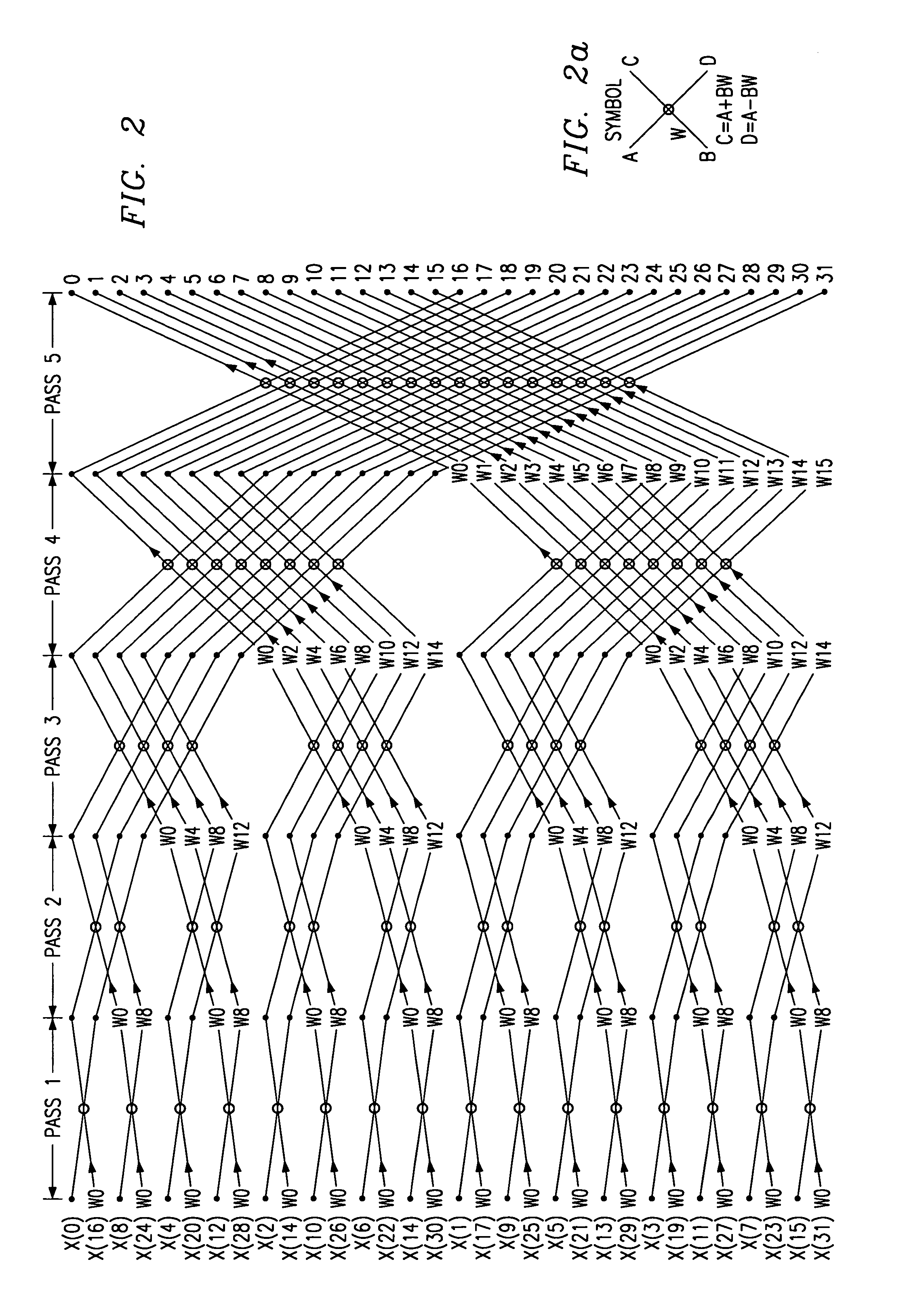

[0045]The preferred and alternative exemplary embodiments of the present invention include methods of in place bit reversal (IPBR) that are computationally efficient patterns to generate sequential address pairs for computing fast Fourier transforms in a processor. To decide which of the methods of the present invention is most efficient for a specific application, reference is made to the decisional flowchart of FIG. 1. Assume an input array 10 is stored in 2^(log 2N+M) contiguous words of memory, beginning at start address S_in. The array has 2^ log 2N elements and each element is stored in 2^M contiguous words of data memory. For example, four words of contiguous memory would accommodate two words of precision for both the real and imaginary part of complex input data elements.

[0046]In the present invention, five new IPBR address generators for mapping arrays in bit reversed order are disclosed. Methods 1m, 2m, 3m, 4m are modifications of the respective method. Many of the method...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com