Input and output driver

a technology of input and output, applied in the direction of logic circuits, pulse techniques, digital storage, etc., can solve the problems of difficulty in satisfying the requirements of input capacitance cin, and achieve the effect of reducing the input capacitance cin of a ddr-iii produ

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019]A disclosed input and output driver comprises: an input buffer for supplying input data from a DQ pad to a memory cell array in a writing mode; an output driver for supplying output data from the memory cell array to the DQ pad in a reading mode; and a DQ switch for electrically isolating the output driver from the DQ pad in the writing mode.

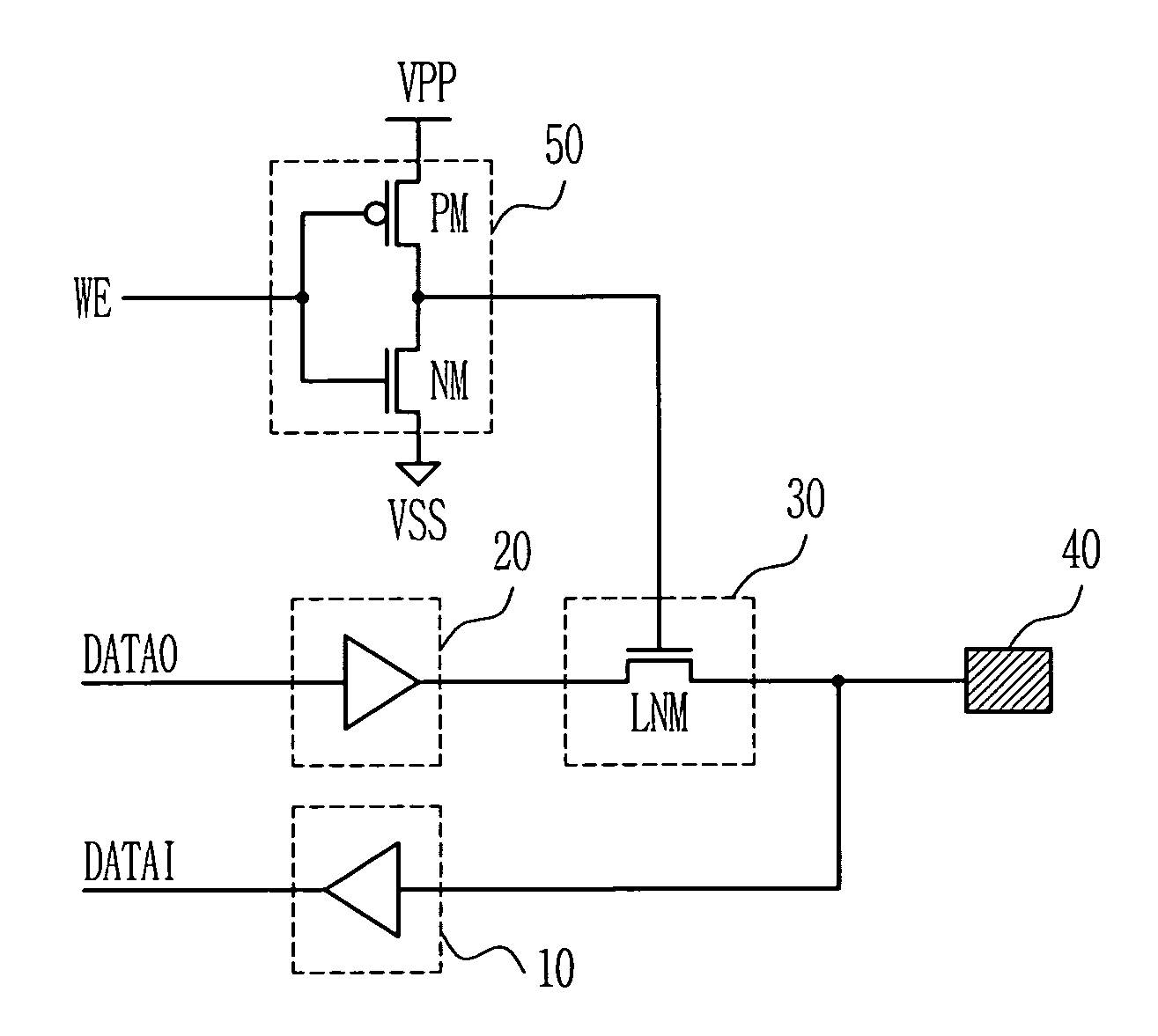

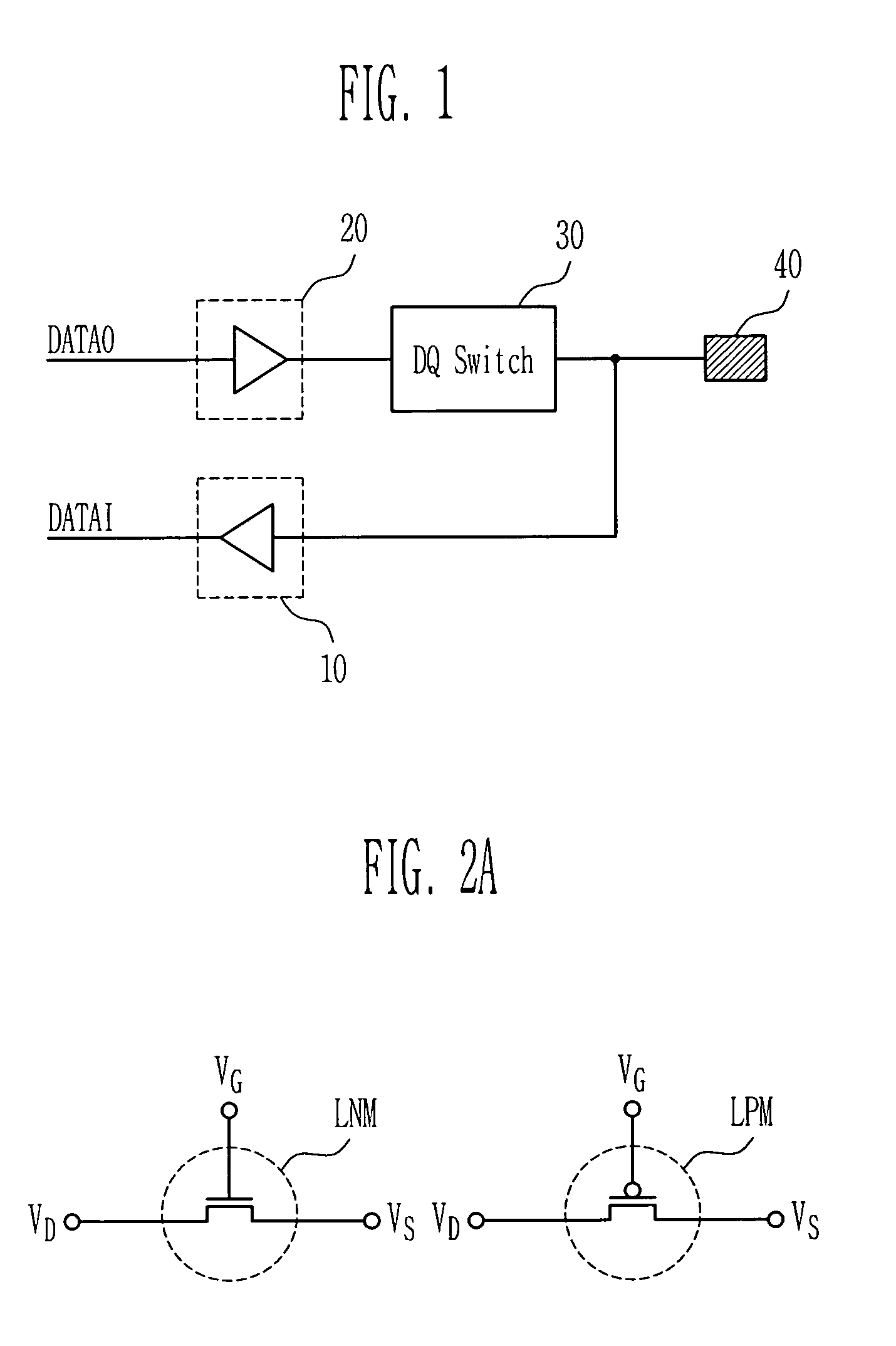

[0020]FIG. 1 is a block diagram of an input and output driver according to a preferred embodiment.

[0021]Referring to FIG. 1, an input and output driver according to a preferred embodiment comprises an input buffer 10, an output driver 20, and a DQ switch 30, and is connected to a DQ pad 40.

[0022]In a writing mode, the DQ switch 30 is turned-off to electrically isolate the output driver 20 from the DQ pad 40. On the other hand, in a reading mode, the DQ switch 30 is turned-on to electrically connect the output driver 20 to the DQ pad 40.

[0023]In the writing mode, the DQ switch 30 is tuned-off to electrically isolate the output driver 20 fro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com