Semiconductor device, refresh control method thereof and computer system

a technology of a memory controller and a memory device, applied in the field of memory controller, can solve the problems of increasing consumption current and inability to apply to a general dram, and achieve the effects of reducing consumption current, rapid refresh operation, and improving memory access efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

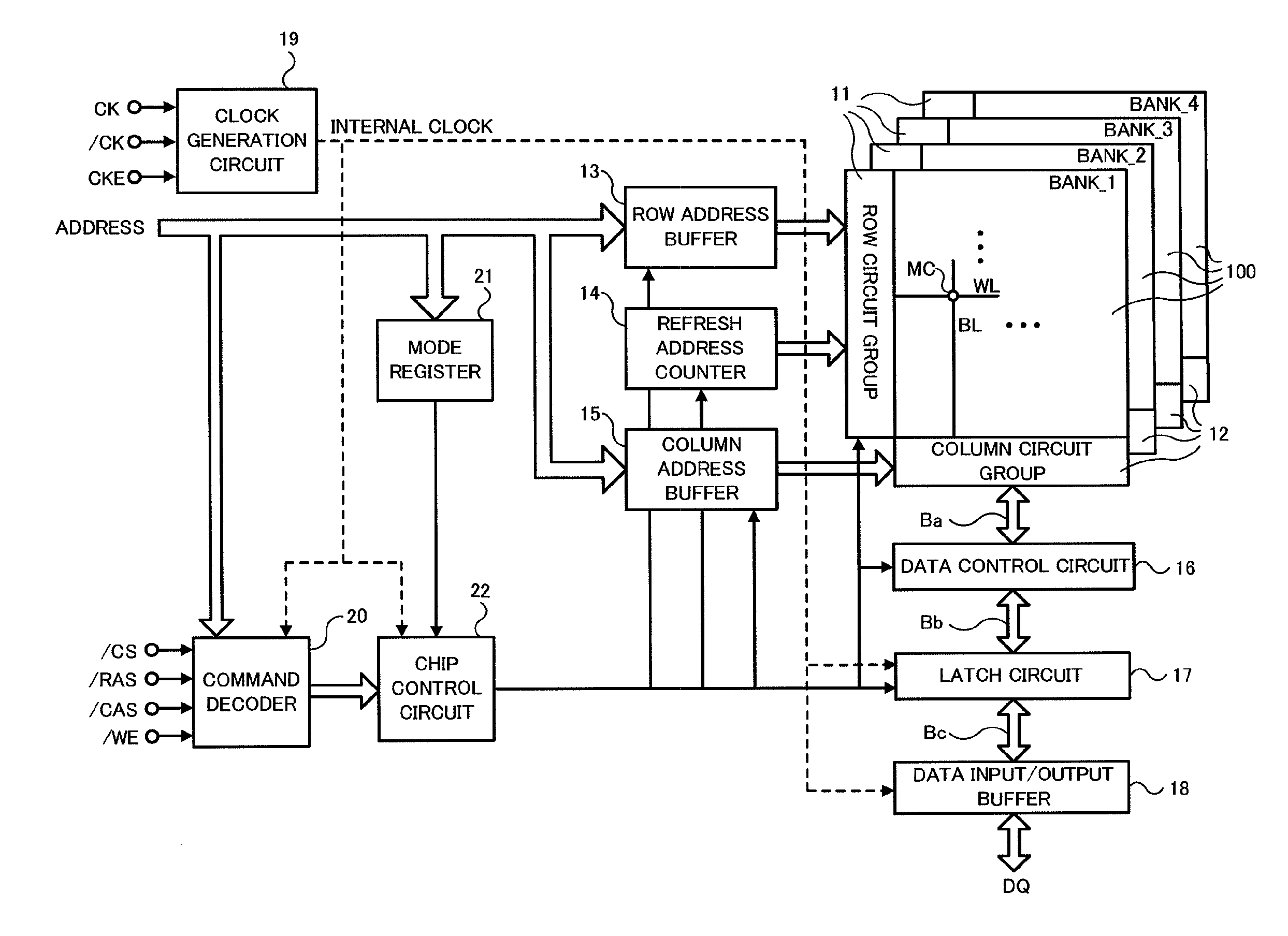

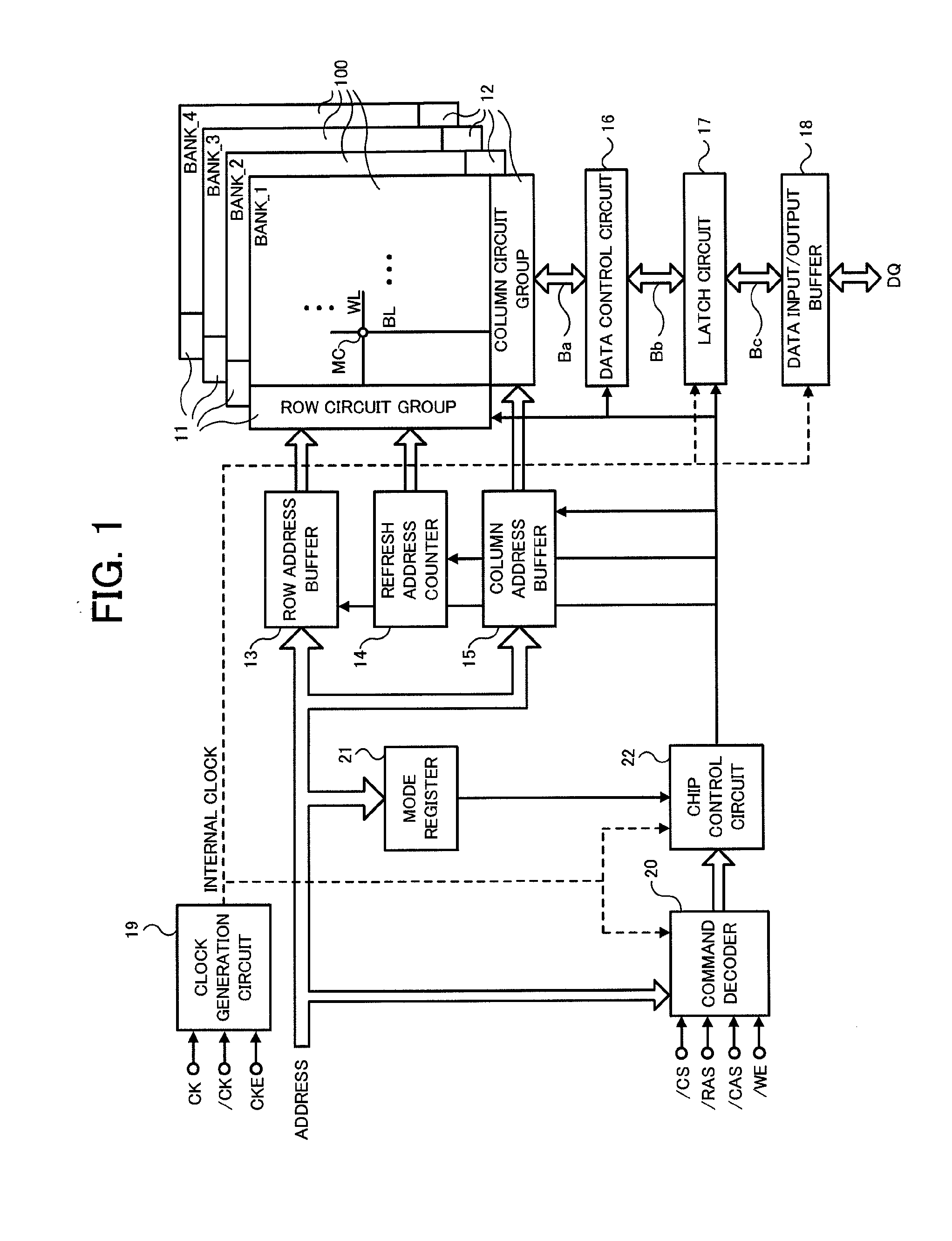

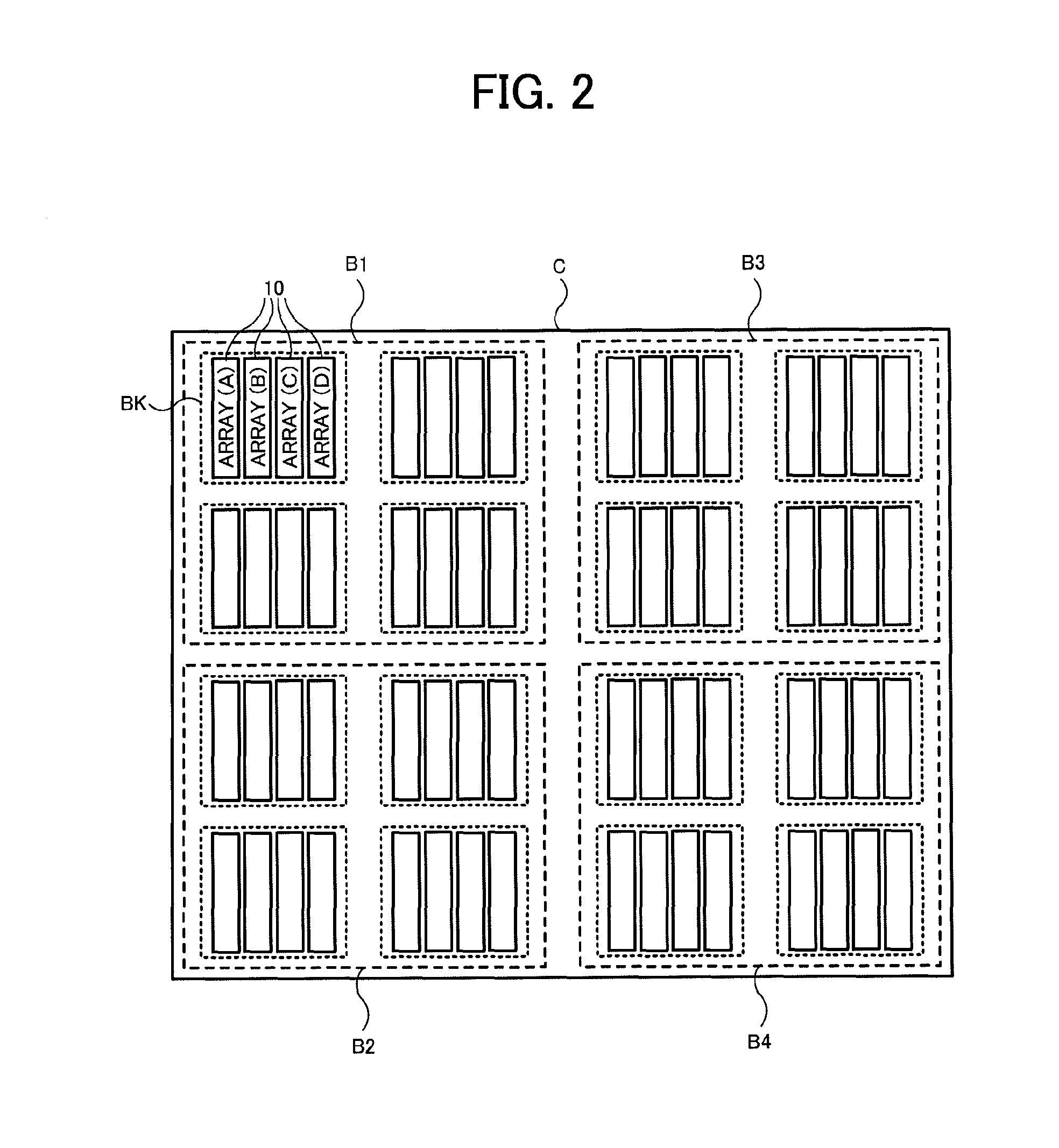

[0045]FIG. 1 shows a block diagram of an entire configuration of the DRAM of the first embodiment to which the present invention is applied. The DRAM shown in FIG. 1 is implemented on a memory chip C (FIG. 2), and is provided with a memory cell array region 100 divided into a plurality of banks (BANK), a row circuit group 11 and a column circuit group 12 that are attached to each bank. Although there are provided four banks (BANK) in the example of FIG. 1, the number of banks is not restricted. In the memory cell array region 100, a plurality of memory cells MC are formed at intersections of a plurality of word lines WL and a plurality of bit lines BL. The row circuit group 11 includes circuits such as a large number of row decoders (not shown) and the like that are provided corresponding to the plurality of word lines WL. The column circuit group 12 includes circuits such as later-described sense amplifier rows that are provided corresponding to the plurality of bit lines.

[0046]A r...

second embodiment

[0069]In the DRAM of the second embodiment, a relief circuit that replaces a defective word line with a redundancy word line is added to the DRAM of the first embodiment. The configurations and operations of FIGS. 1 to 5 and 8 to 10 in the first embodiment are common in the second embodiment and thus description thereof will be omitted. FIG. 11 is a flow chart showing a flow of the refresh control performed in the DRAM of the second embodiment. In FIG. 11, Step S20 is performed in the same manner as Step S10 in the first embodiment.

[0070]Subsequently, if the open page does not exist in the block BK (Step S20: NO) in accordance with determination result of Step S20, it is determined whether or not the refresh address matches a relief originating address (Step S21). The relief originating address means a row address at which a defective word line has existed and relieved. If the determination result of Step S21 indicates that the refresh address does not match the relief originating a...

third embodiment

[0073]Although the refresh control corresponding to the existence of the open page is performed for each block BK in the DRAM of the first and second embodiments, the DRAM of the third embodiment is modified so that the same refresh control is performed for each memory cell array 10. FIG. 13 shows a first setting example of an array register AR (refer to FIG. 20) in the DRAM of the third embodiment. The array register AR is provided in the control data registers 40 of the array control circuit 32, and stores information required for performing the refresh control of the third embodiment. Specifically, when stored data in the memory cell MC corresponding to the open page is sensed and amplified by a predetermined sense amplifier SA, array address information identifying all memory cell arrays 10 to which word lines WL sharing the predetermined sense amplifier SA belong is stored in the array register AR.

[0074]Four memory cell arrays 10(A), 10(B), 10(C) and 10(D) are shown in the uppe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com