Method of fabricating a semiconductor device

a semiconductor and device technology, applied in semiconductor devices, capacitors, electrical devices, etc., can solve the problems of unavoidable decrease in yield, increase in cost relative to basic process cost, and complicated device structure, and achieve high density structure and sufficient capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Hereinafter, an exemplary embodiment of the present invention will be described.

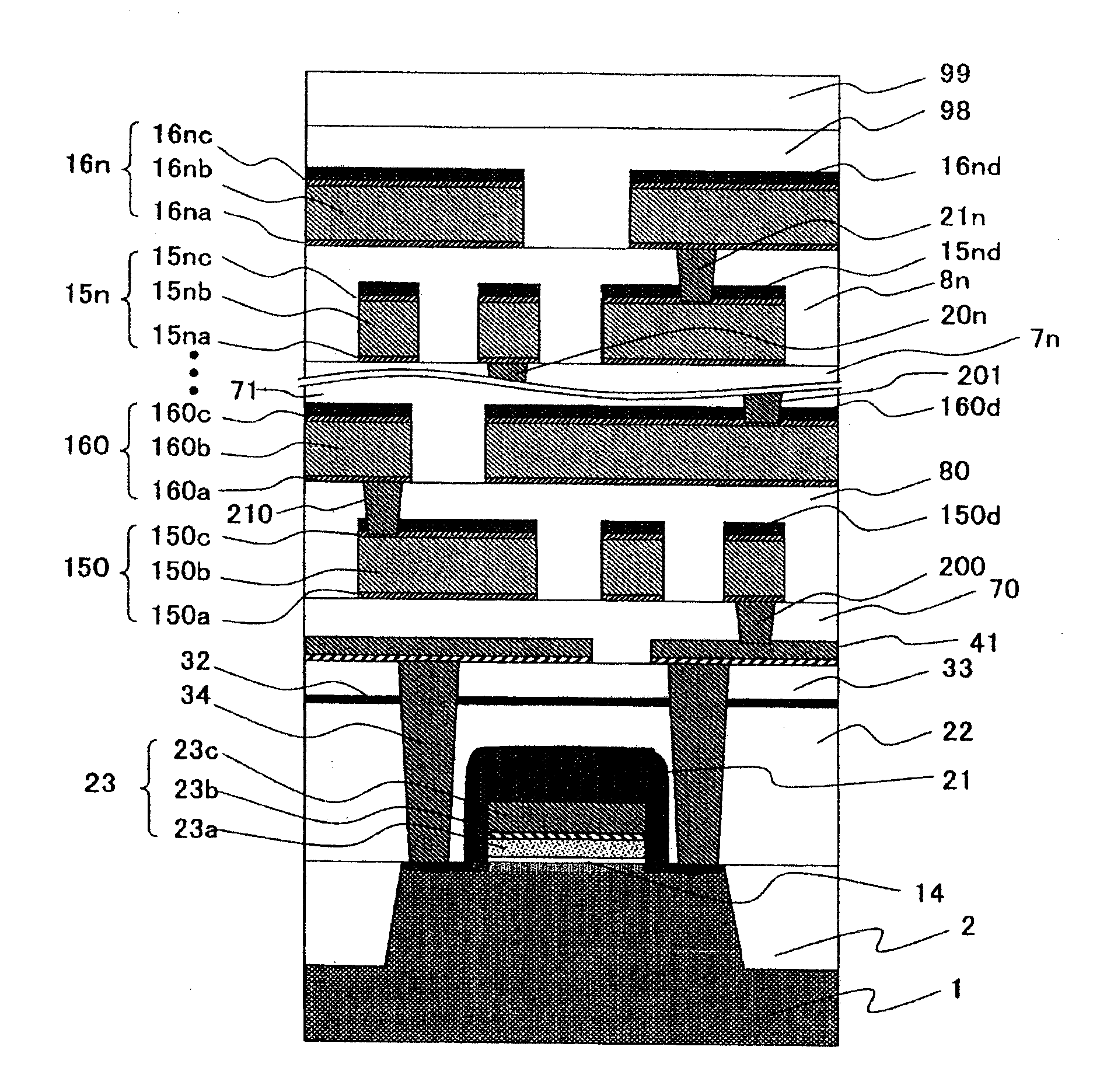

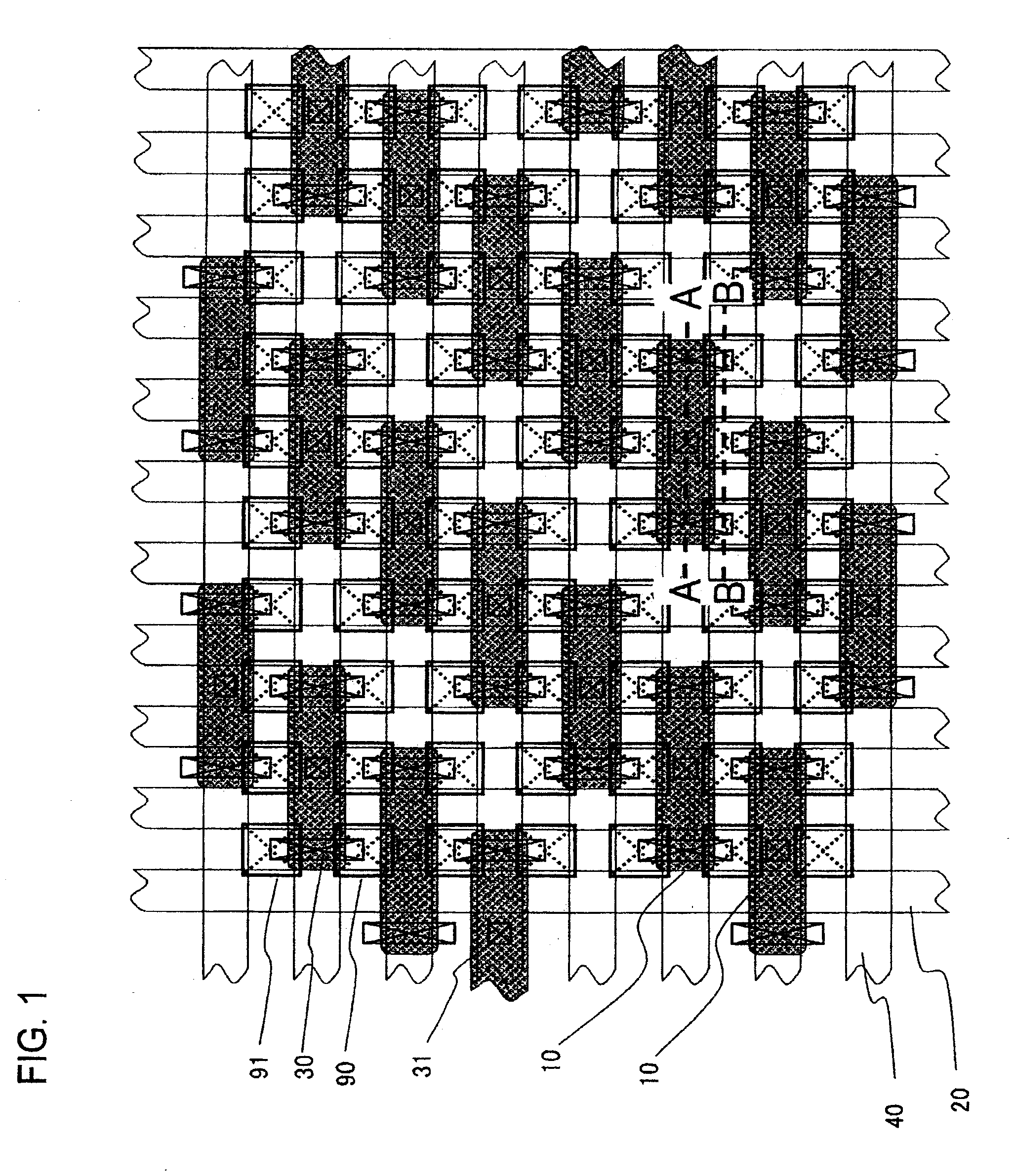

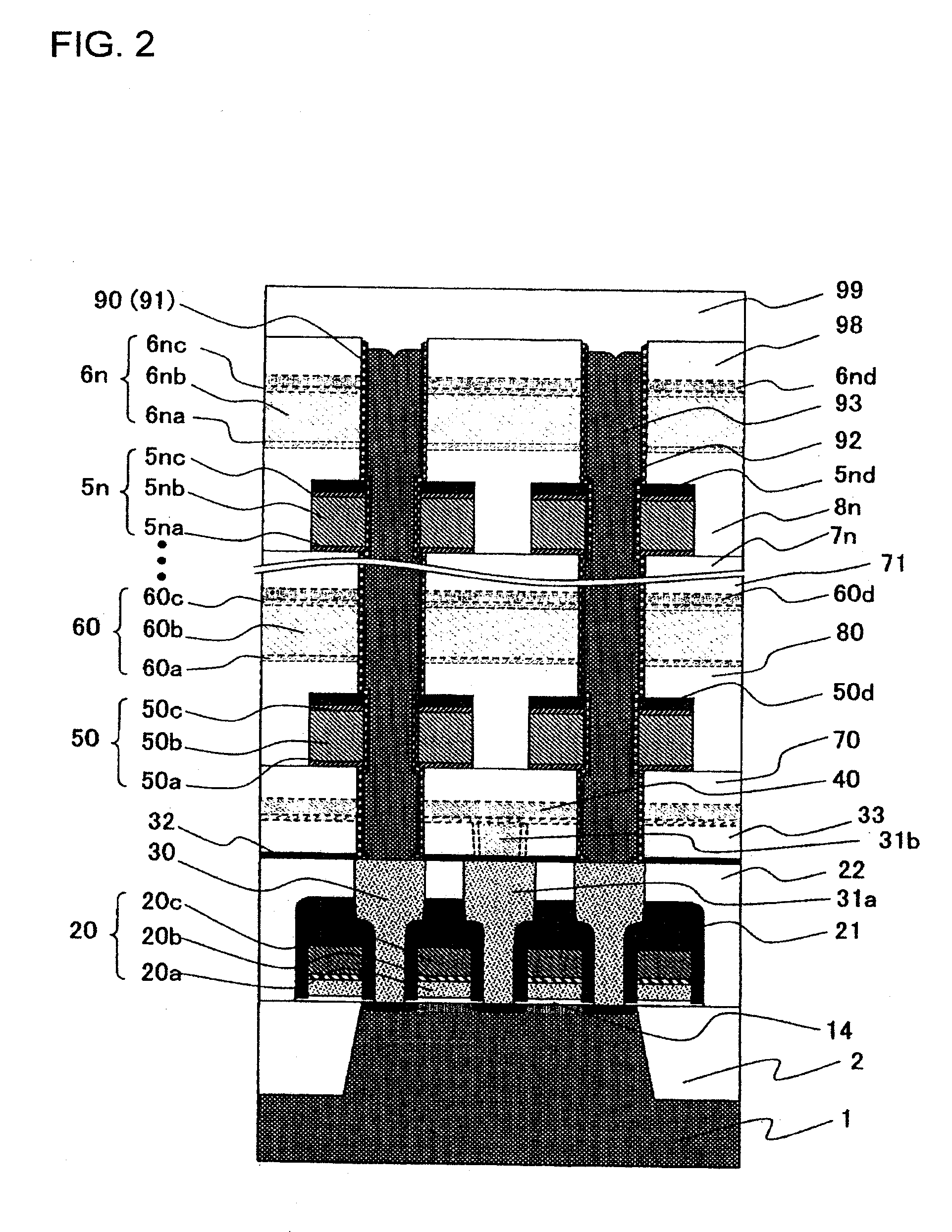

A semiconductor device in accordance with the present embodiment has a structure that includes a layered region in which a capacitor element is formed (i.e., capacitor region), and in the capacitor region, an interconnection layer is formed such that the interconnection layer is utilized as a counter electrode of the capacitor element. The semiconductor device can accordingly ensure a sufficient storage capacitance and an increased density compatibly.

In a DRAM capacitor of the device in accordance with the present embodiment, an exclusive electrode common to all the cells is not used as a counter electrode, which is opposed to a storage electrode, but an interconnection wire extending through the capacitor region is used as the counter electrode. Accordingly, this interconnection wire can be utilized as an interconnection wire in a peripheral circuit region as well. For this reason, a necessary interconn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com