Semiconductor device and method for manufacturing the same

a technology of semiconductors and semiconductors, applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problem of difficult to achieve the optimal amount of signal b>5/b>vth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

first embodiment

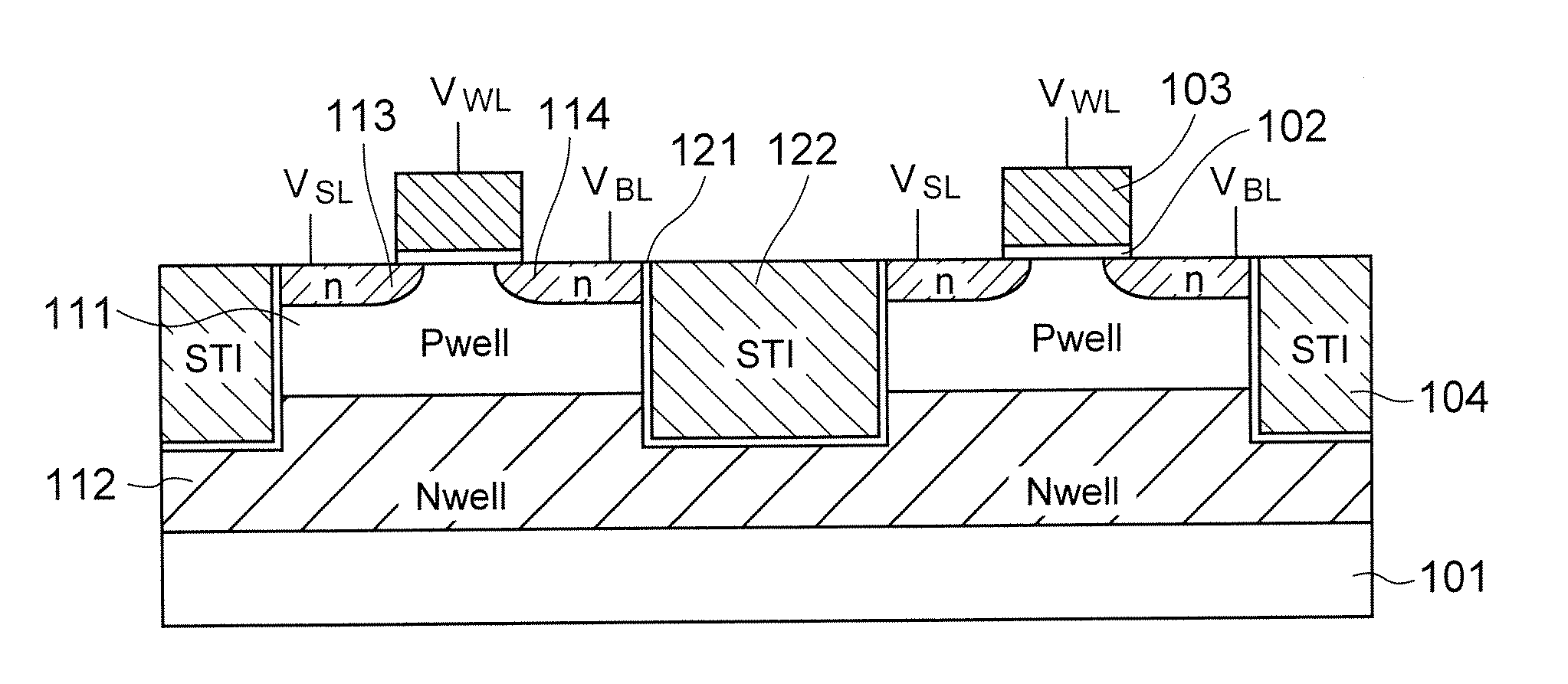

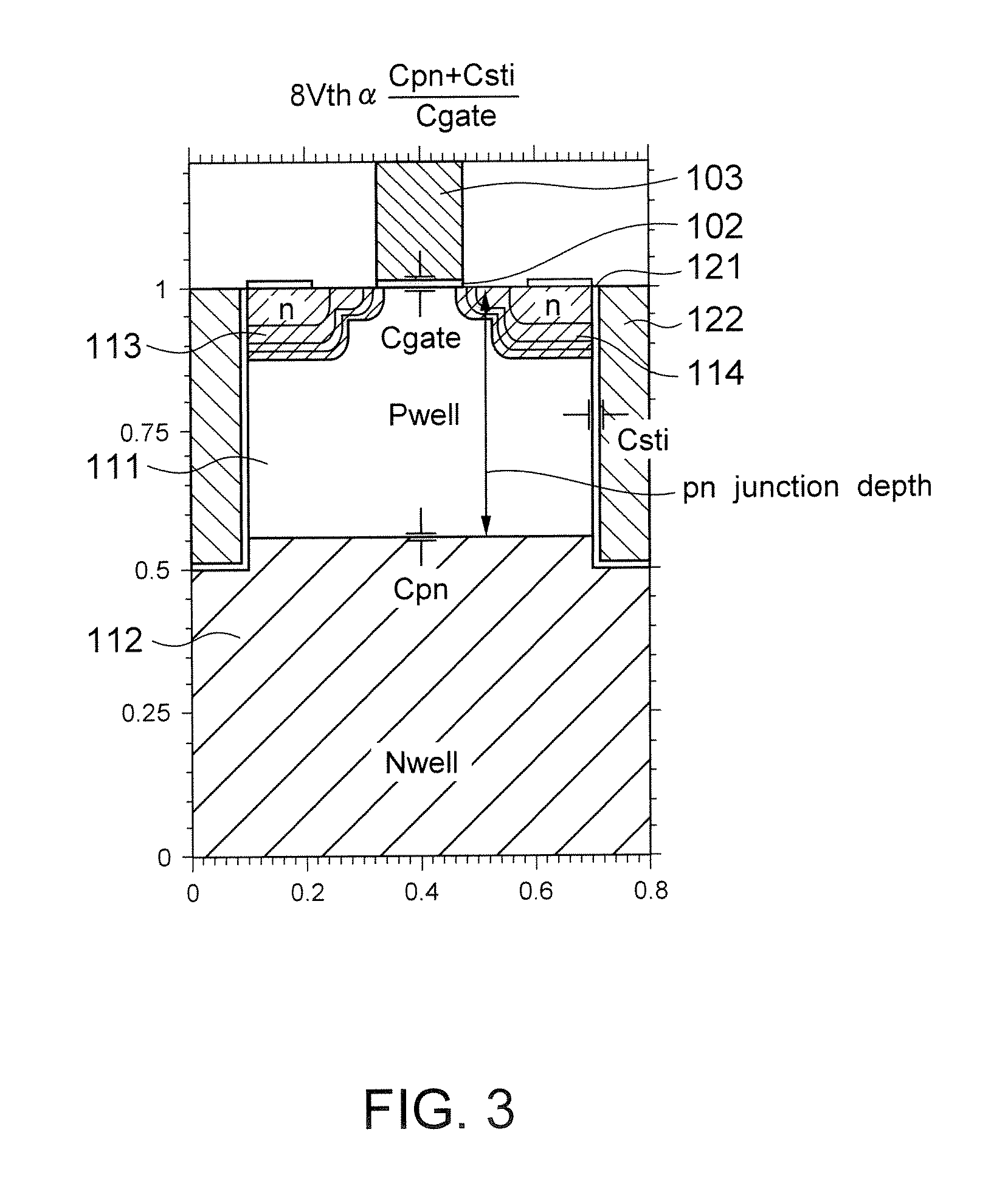

[0025]FIG. 1 is a side cross-sectional view of a semiconductor memory device according to a first embodiment. The semiconductor memory device shown in FIG. 1 includes capacitorless DRAM memory cells. A transistor constituting the DRAM memory cell shown in FIG. 1 is an FET (here, a MOSFET).

[0026]The semiconductor memory device shown in FIG. 1 includes a substrate 101, a gate oxide film 102 constituting the MOSFET, a gate electrode 103 constituting the MOSFET, a plurality of rows of STIs (Shallow Trench Isolations) 104 corresponding to a particular example of isolation layers for isolating MOSFET from one another. The gate oxide film 102 is a particular example of a gate insulator film of the transistor, and the gate electrode 103 is a particular example of a gate electrode of the transistor.

[0027]The substrate 101 is a bulk substrate (here, a bulk silicon substrate). The substrate 101 includes a p-type well (Pwell) 111 for storing signal charges corresponding to a particular example ...

second embodiment

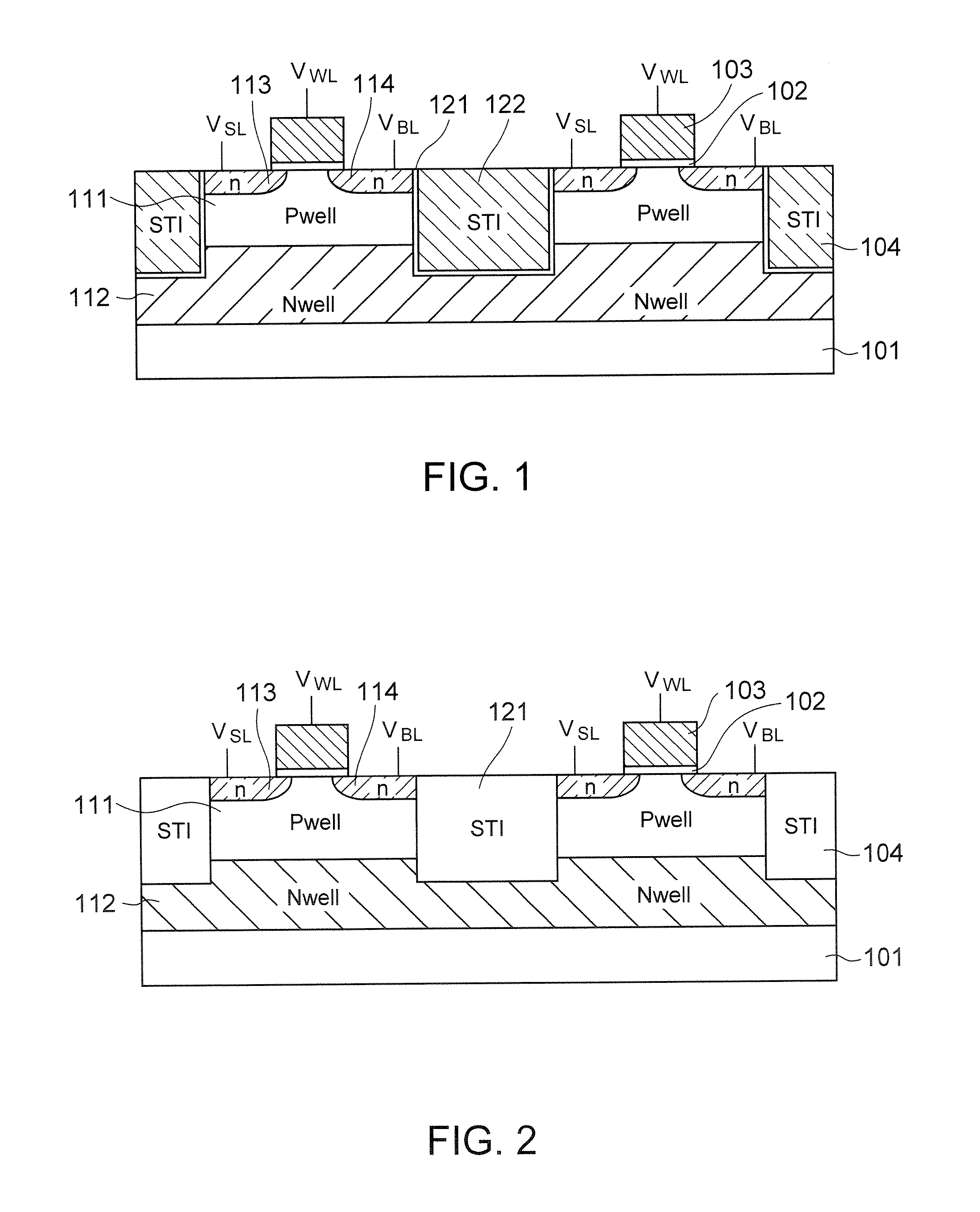

[0043]FIG. 8 is a side cross-sectional view of a semiconductor memory device of a second embodiment. Now, difference between the semiconductor memory device of the first embodiment in FIG. 1 and that of the second embodiment in FIG. 8 will be described.

[0044]In both the semiconductor memory devices in FIG. 1 and 8, each STI 104 has an insulating film 121 and a conductive layer 122. However, in the semiconductor memory device in FIG. 1, each STI 104 has the bottom surface and the side surfaces formed by the insulating film 121, and on the contrary, in the semiconductor memory device in FIG. 8, each STI 104 has the side surfaces formed by the insulating film 121 and the bottom surface formed by the conductive layer 122. Therefore, in the semiconductor memory device in FIG. 1, the conductive layer 122 of each STI 104 is electrically insulated from the substrate 101, while in the semiconductor memory device in FIG. 8, the conductive layer 122 of each STI 104 is electrically connected to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com