Memory device with improved writing capabilities

a memory device and writing capability technology, applied in the field of memory devices, can solve the problems of inefficiency in recovering manufacturing errors, write failure and read failure, instability, etc., and achieve the effects of reducing the vdd supply of the column, reducing the drive of the pmos pull-up of the memory cell, and facilitating the force of access transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

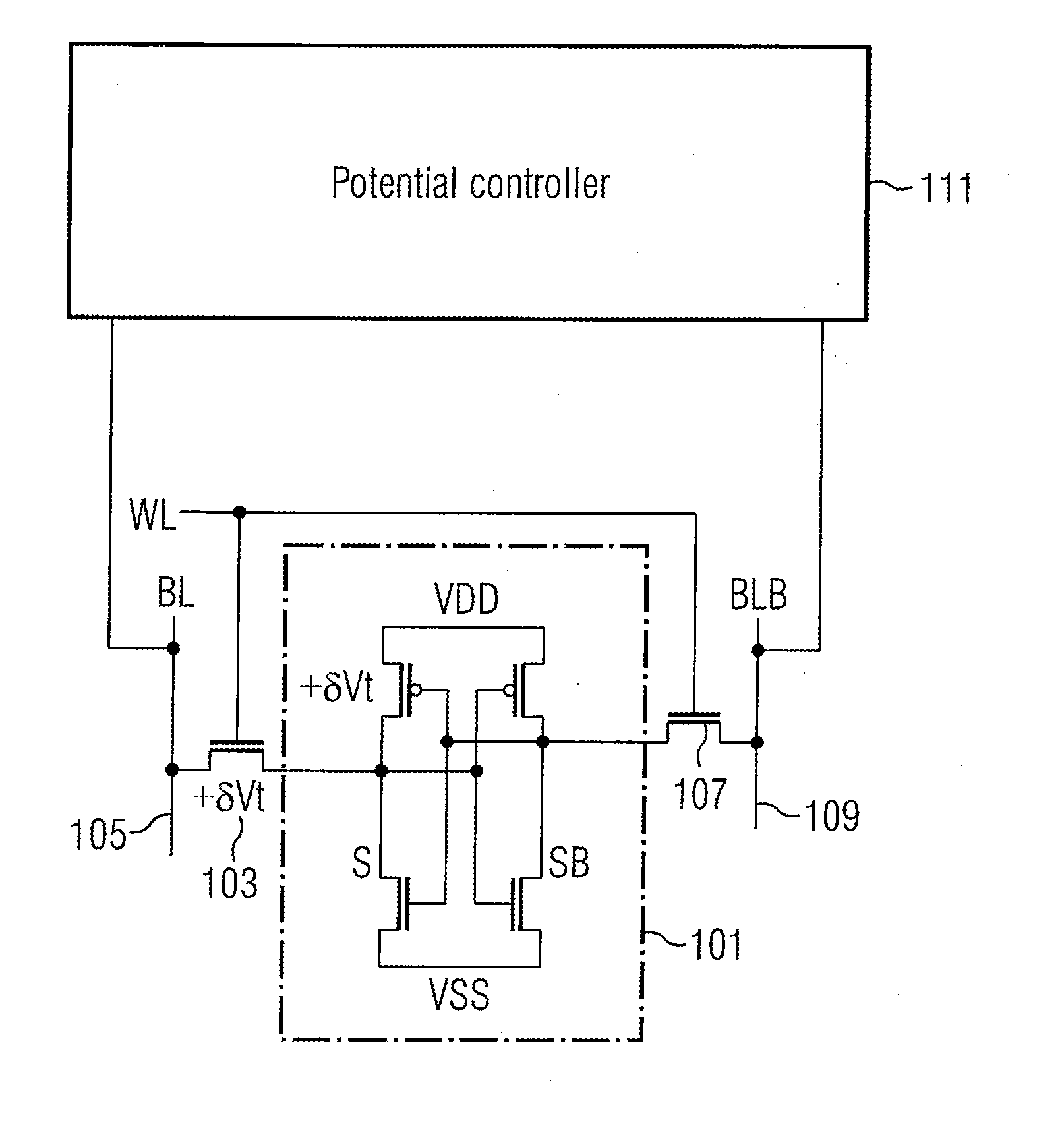

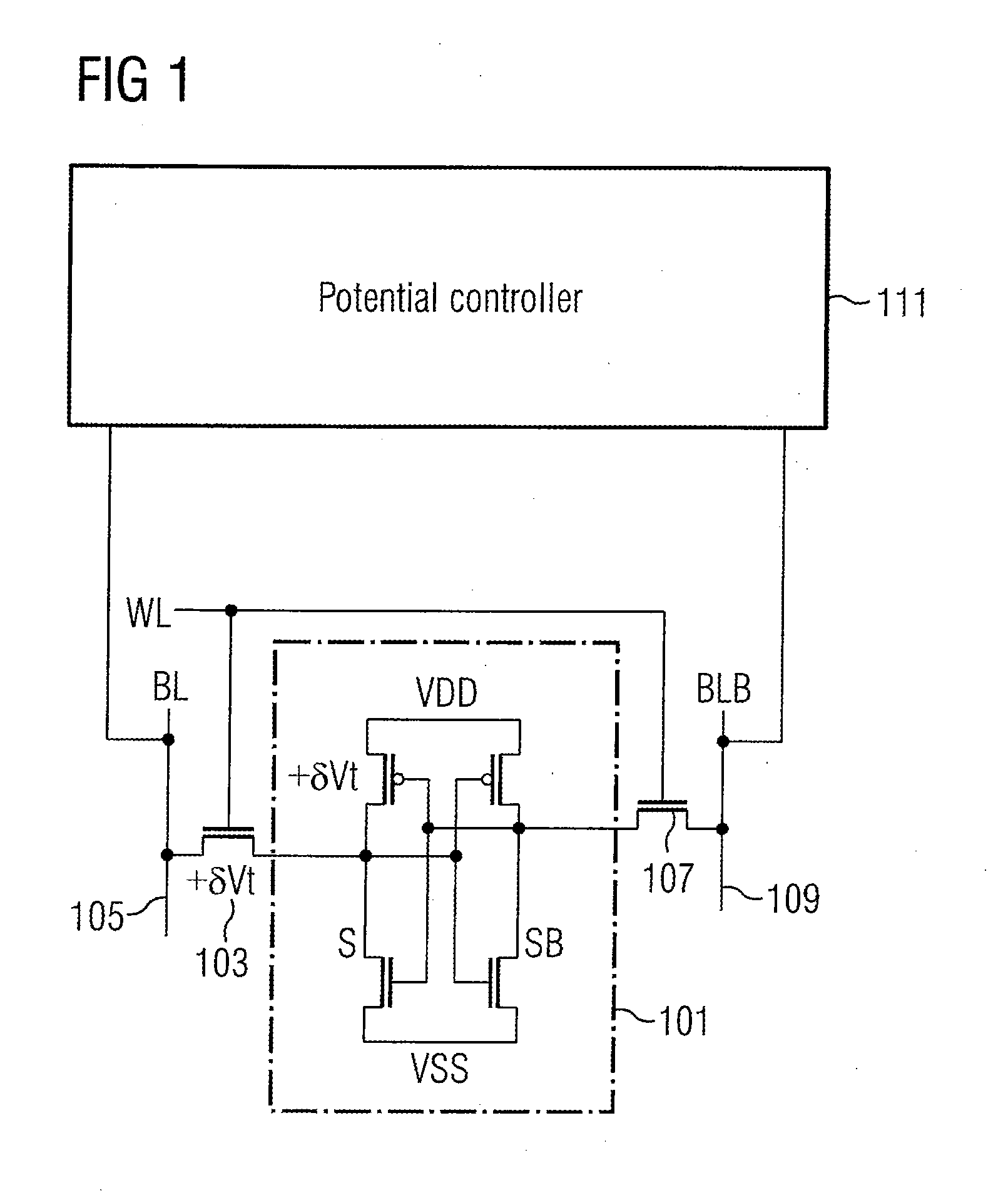

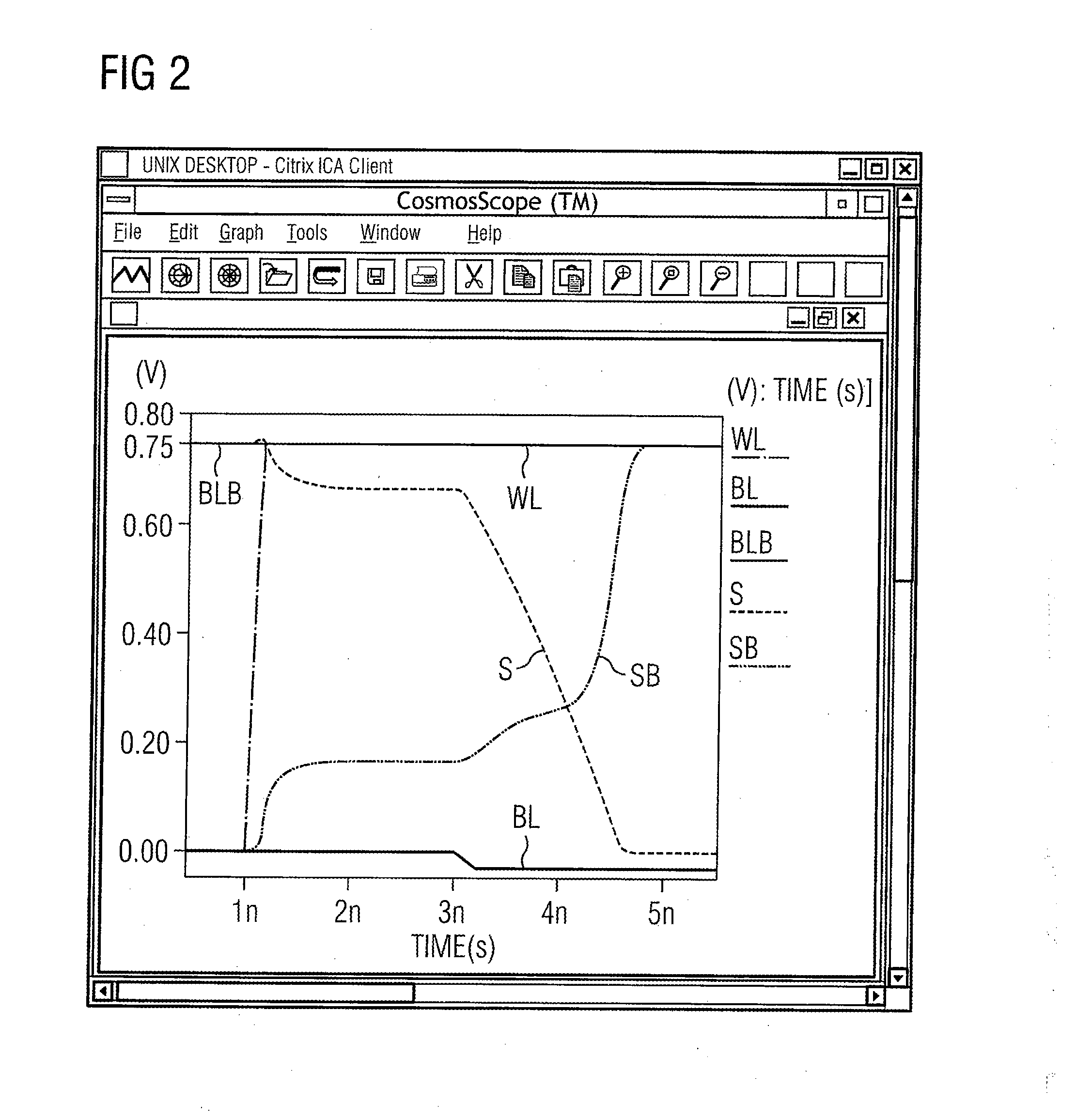

[0038] The memory device shown in FIG. 1 comprises a memory element 101 coupled via a transistor 103 to a bit line 105. The memory element 101 is further coupled by a further switch 107 to a further bit line 109.

[0039] The switches 103 and 107 are formed by transistors having control gates coupled to a wordline WL. The memory device further comprises a potential controller 111 having a first terminal coupled to the bit line 105 (BL) and a second terminal coupled to the further bit line 109 (BLB).

[0040] As depicted in FIG. 1, across the transistor 103 a threshold voltage variation +δVt may be present, which may increase the absolute threshold voltage Vt when writing a “0” from the bit line 105 to the memory cell by e.g. a weak N access device. Correspondingly, the varying voltage across the transistor 103 may contribute to a reduction of the absolute voltage Vt when e.g. writing a “0” via the bit line 105 for the case of a strong P load.

[0041] The memory element 101 is accessed to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com