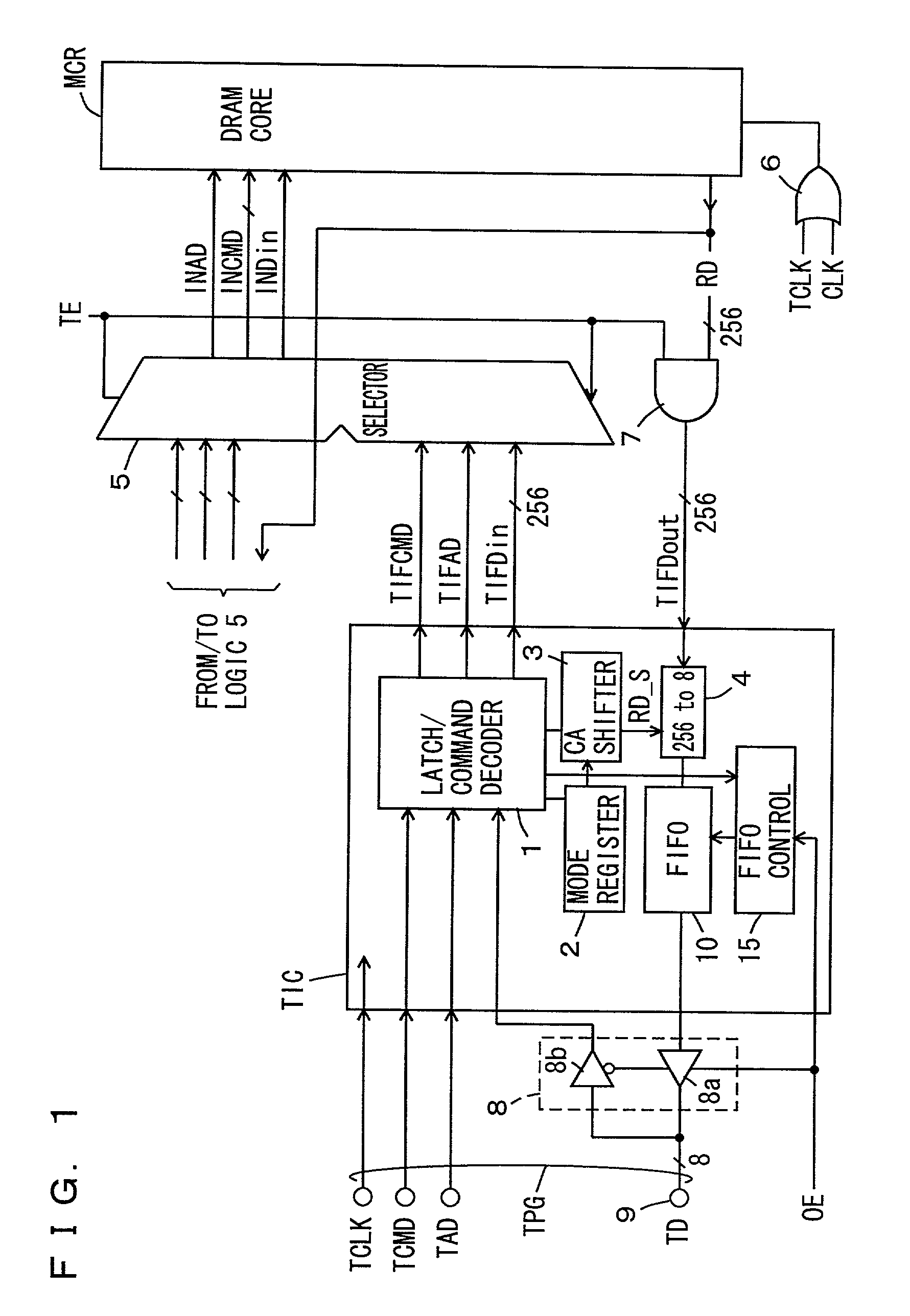

Test interface circuit and semiconductor integrated circuit device including the same

a technology of integrated circuits and test interfaces, which is applied in the direction of measurement devices, digital storage, instruments, etc., can solve the problems of large load, inability to accurately perform test of dram operation timing margins, and difficulty in ensuring the reliability of drams

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

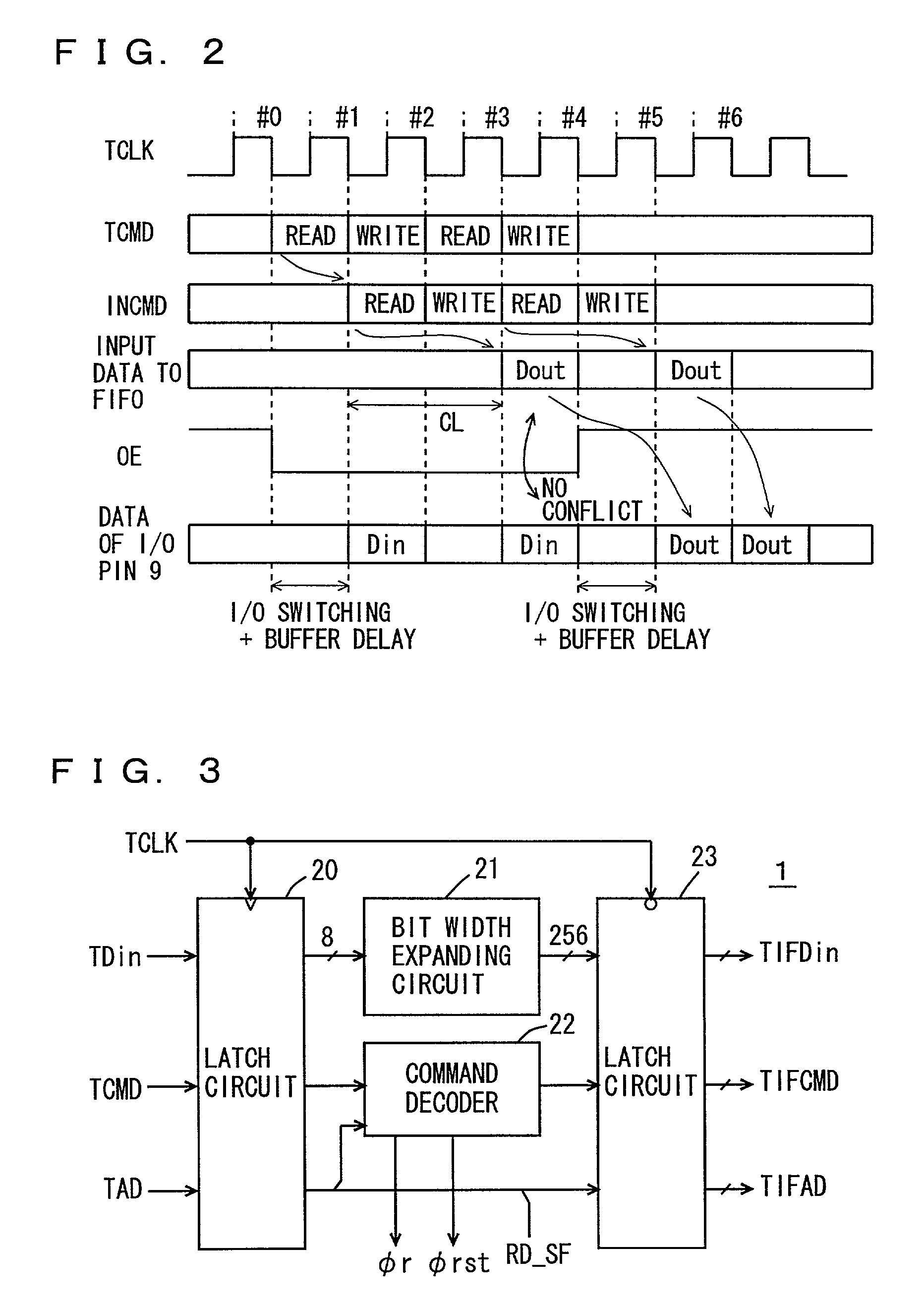

[0128] One page in the embedded DRAM may have a size other than 2048 bits. The input / output data of the DRAM core may have a bit width m of, e.g., 128 bits or 512 bits other than the foregoing value.

[0129] Column latency CL may take a value other than 2. If delay of the input data in the bidirectional I / O circuit cannot be neglected, the data write timing of the first-in first-out circuit is adjusted considering this delay.

[0130] The memory is not restricted to the DRAM, and may be another kind of memory such as a burst SRAM (Static Random Access Memory) or a flash memory, which operates in synchronization with the clock signal. The invention can be applied to any memory, provided that the memory is integrated with a logic on the same semiconductor substrate.

[0131] As described above, the invention can provide the test interface circuit, which allows a sufficient test on a mixed (embedded) memory without constraints on the test patterns due to the test data input / output switching ti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com