Production of semiconductor component and method for adjusting component channel area lattice distance

A manufacturing method and a technology for adjusting components, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., to achieve the effects of improving charge mobility, improving component performance, and increasing process costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

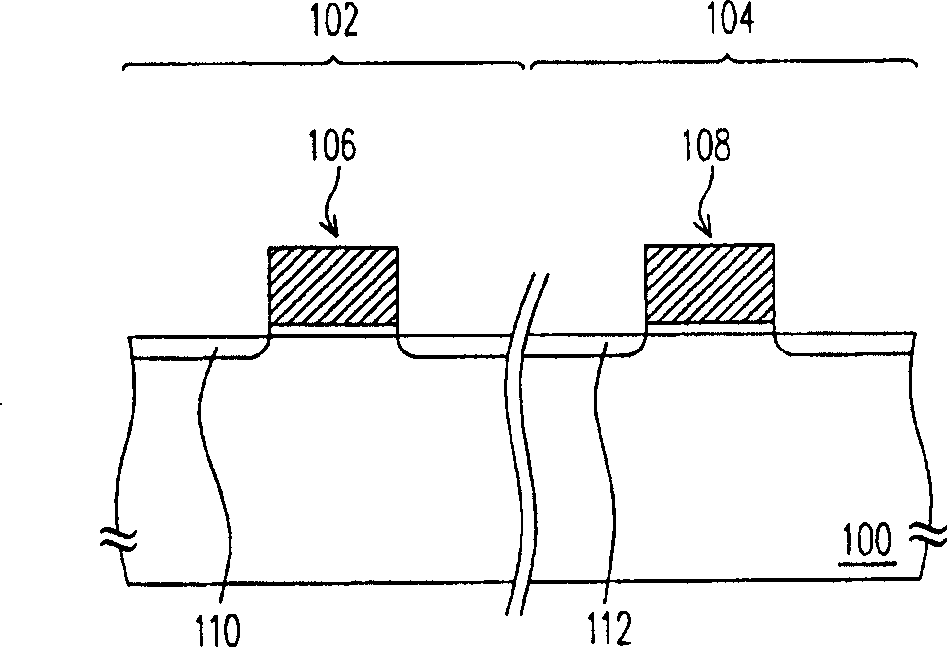

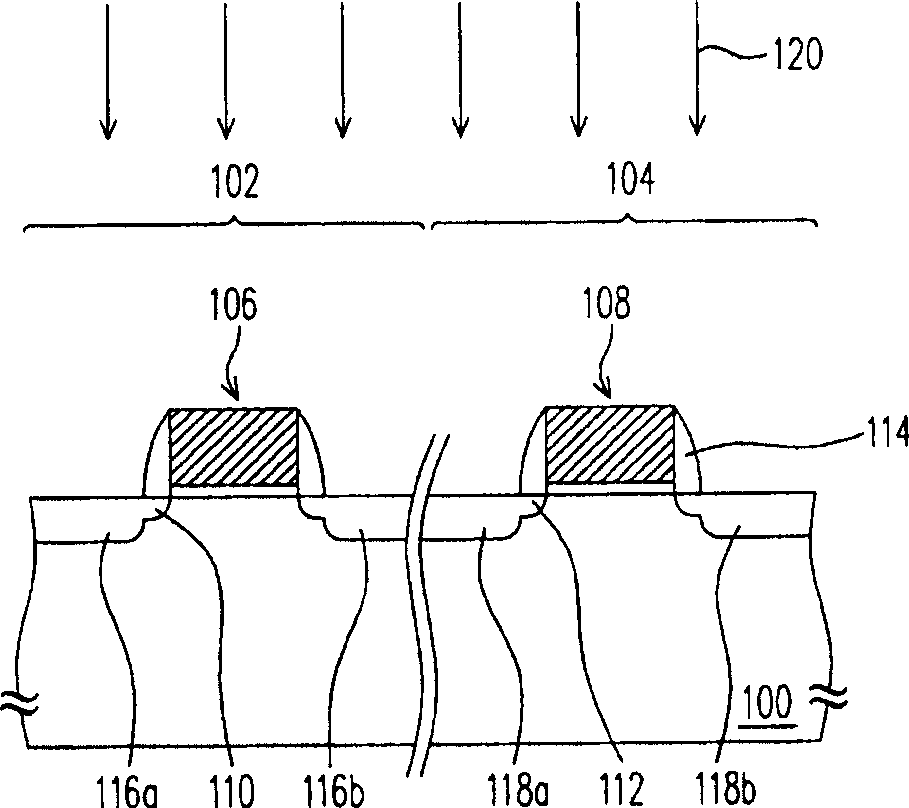

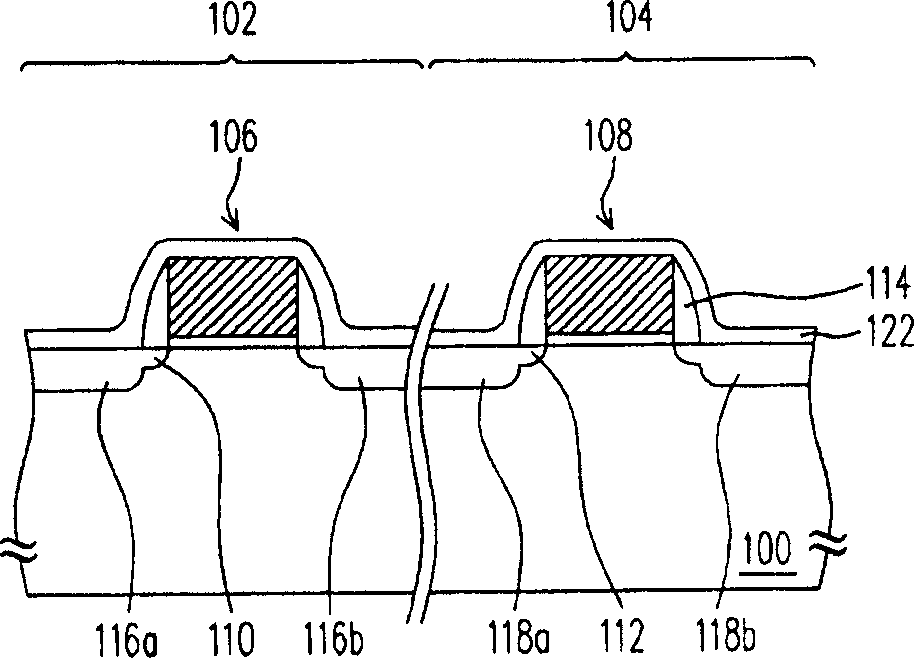

[0041] Figure 2A to Figure 2F is a schematic cross-sectional view illustrating a manufacturing process of a semiconductor device according to a preferred embodiment of the present invention. Please refer to Figure 2A , providing a substrate 200 , for example, the substrate 200 has a main device area 202 and a peripheral circuit area 204 . Then, gate structures 206 and 208 are formed on the substrate 200 in the main device area 202 and the peripheral circuit area 204 respectively. Wherein, the gate structure 206 is, for example, a part of a memory element or an ESD protection circuit, which is composed of a gate dielectric layer 206a located on the lower layer and a gate layer 206b located on the upper layer. In addition, the gate structure 208 is, for example, a part of a logic device, which is composed of a gate dielectric layer 208a located on the lower layer and a gate layer 208b located on the upper layer. In addition, the material of the gate dielectric layers 206 a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com