Static discharge protecting method for full chip

An electrostatic discharge protection, full-chip technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of ESD protection ability slipping, electrostatic discharge withstand ability decline, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Relevant detailed content and technical description of the present invention, now in conjunction with accompanying drawing, explain as follows:

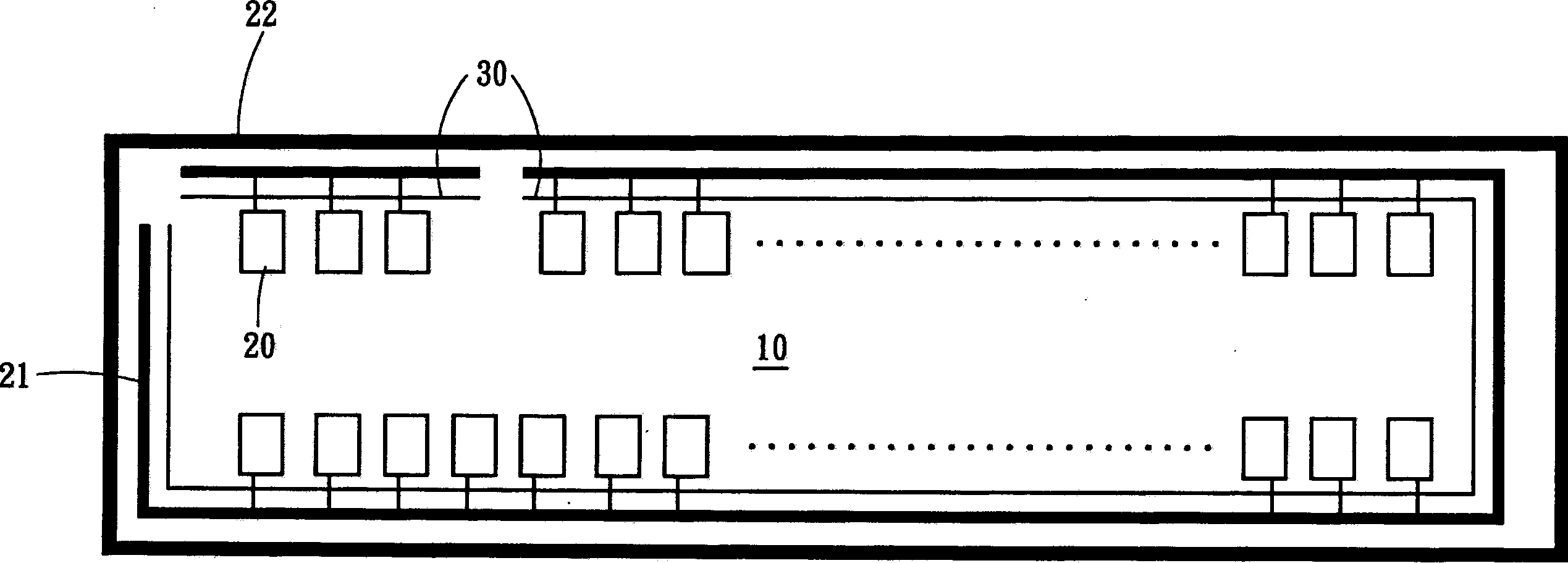

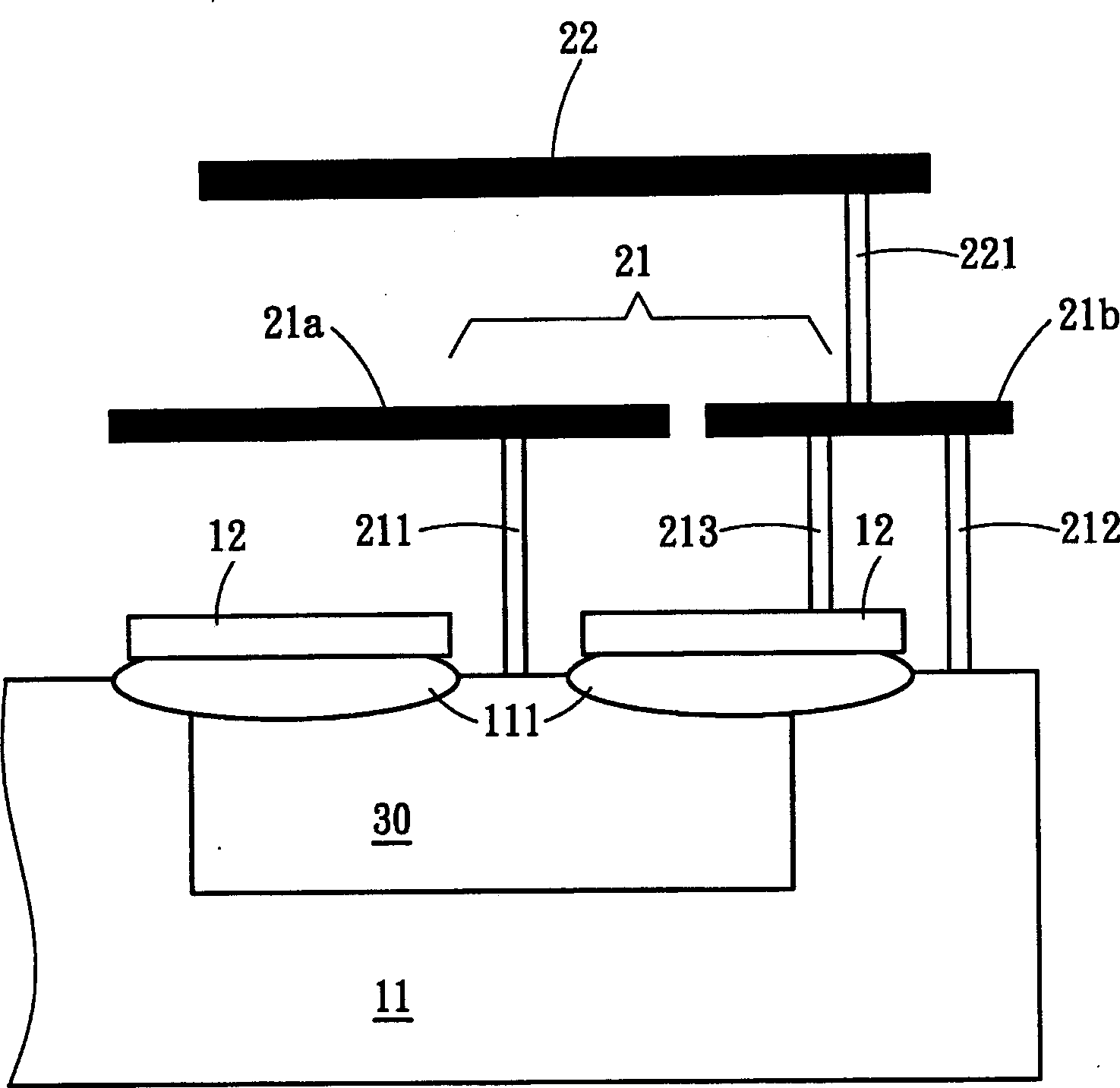

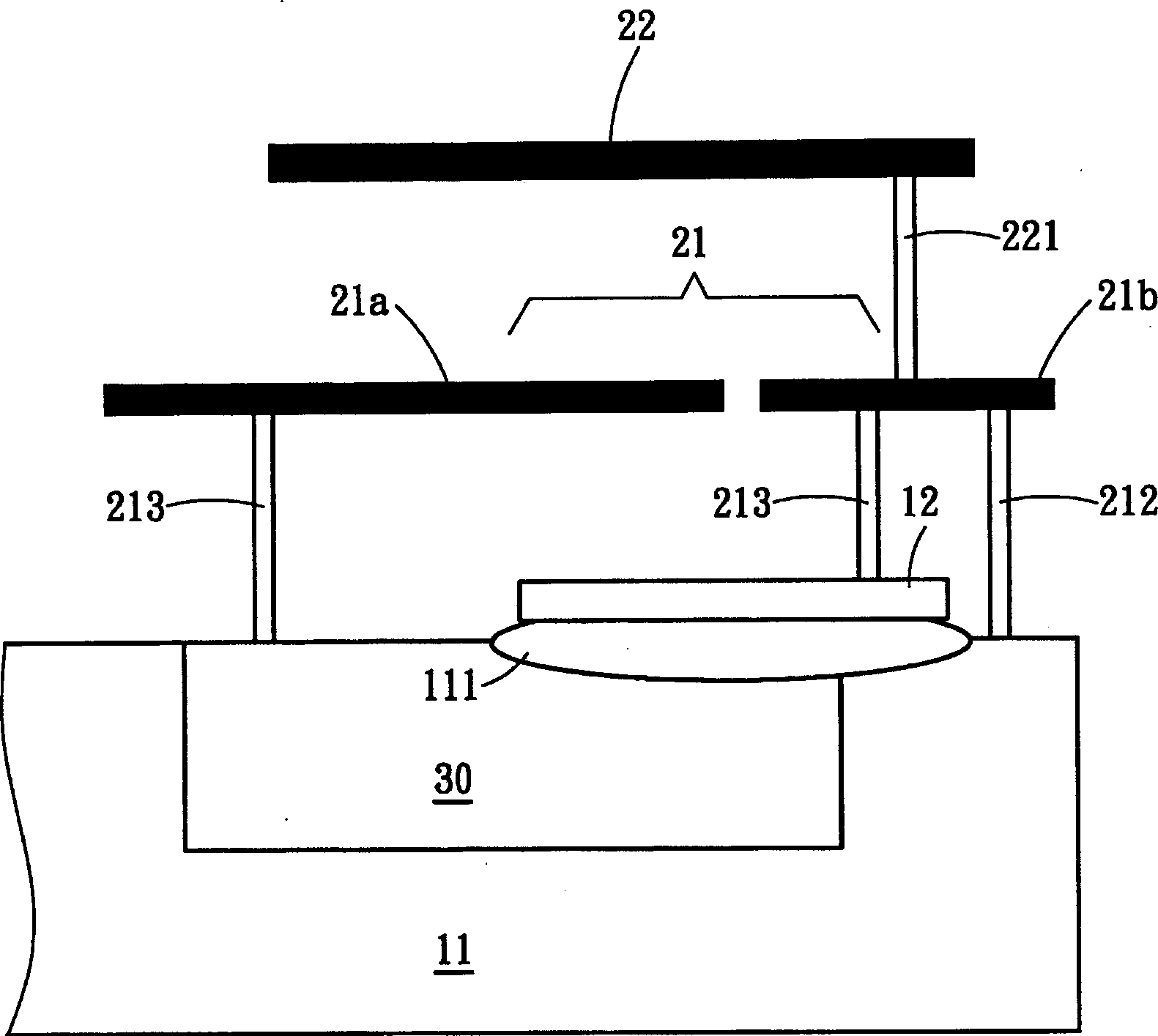

[0015] Please also see figure 1 , 2 , 3, respectively, the layout of the present invention and a schematic cross-sectional view of an embodiment. As shown in the figure, the chip 10 of the present invention includes a first metal layer 21 surrounding the high voltage (VDD) and a second metal layer above the first metal layer 21 connected to the ground (GND) at a suitable distance near its outer periphery. 22, and the welding pad 20 coupled with the first metal layer 21, wherein the first metal layer 21 of the present invention is divided into adjacent first metal layer one 21a and first metal layer two 21b (such as figure 2 , 3 shown), and form a second conductor type well 30 (for example: N well) opposite to the first conductor type substrate 11 (for example: P substrate) of the chip 10 under the first metal layer one 21a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com