Synchronus scanning enable-condition prechargig CMOS trigger

A synchronous scanning and flip-flop technology, applied in electrical components, pulse generation, electrical pulse generation, etc., can solve the problem of extremely asymmetrical rising edge delay and falling edge delay at the output end of the flip-flop circuit, increase in area and power consumption, Large transistor size, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

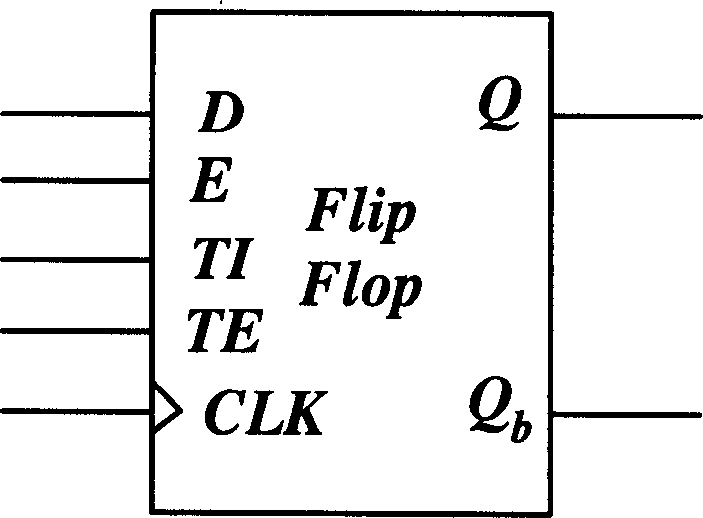

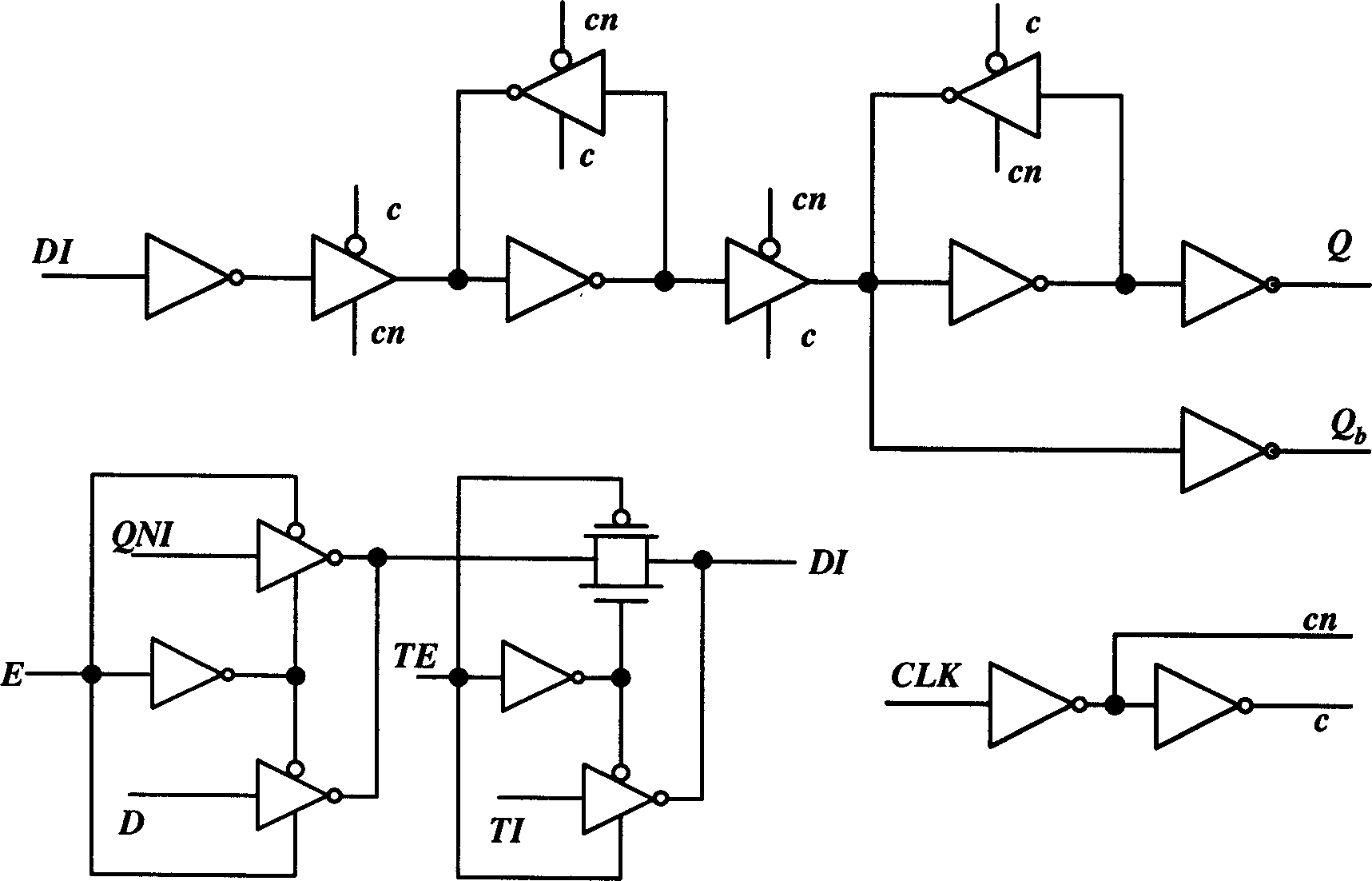

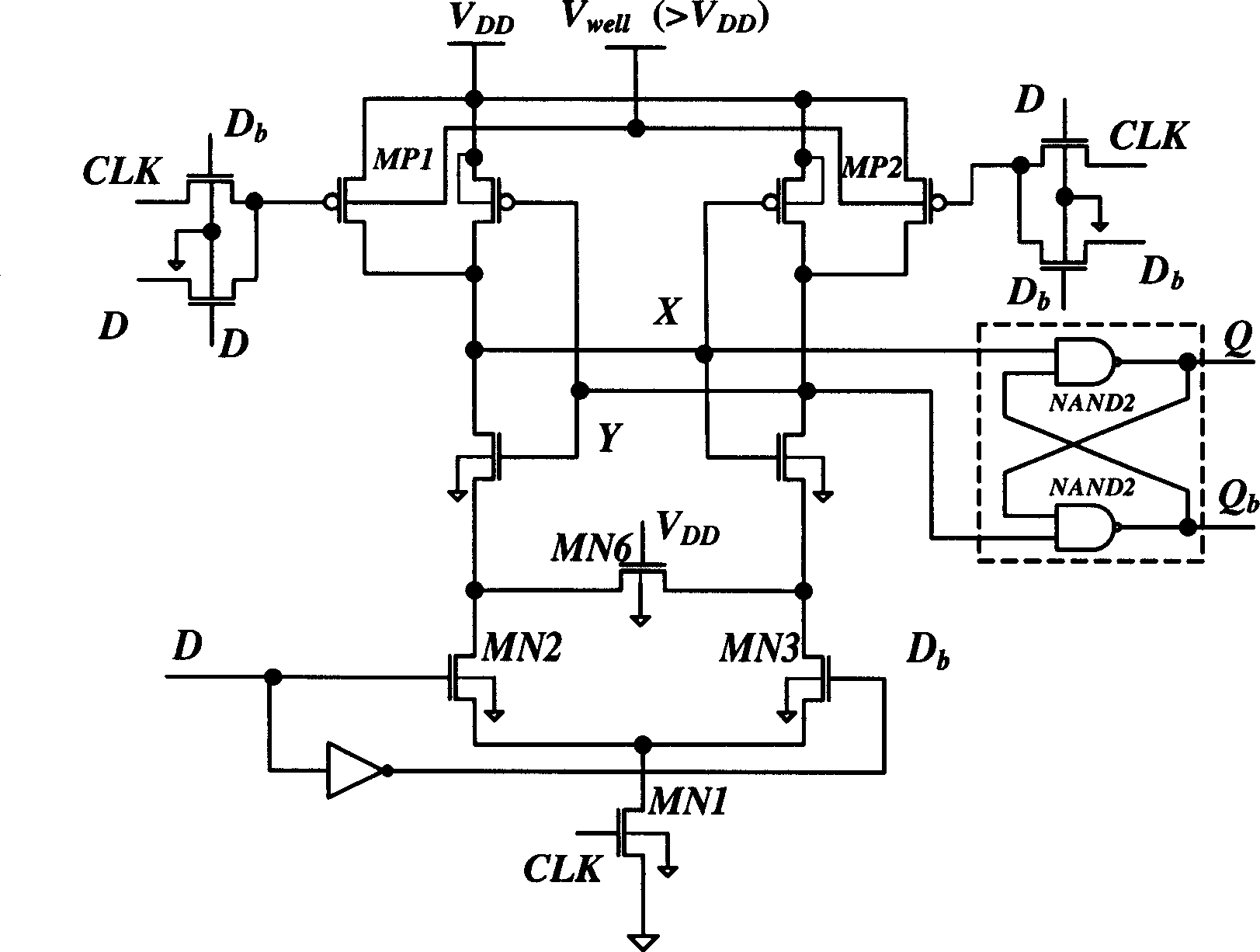

[0096] The technical scheme that the present invention solves its technical problem is: the synchronous scan that the present invention proposes enables the conditional precharge flip-flop FFSEDHD1X_SCB_FCS, as Figure 6 shown. The FFSEDHD1X_SCB_FCS flip-flop has the function of testing and enabling. It adopts the conditional precharge technology to reduce the power consumption of the flip-flop circuit itself, and because the complementary output terminals of the first-stage latch are respectively connected to two independent and have the same circuit parameters On the single clock phase latch of the FFSEDHD1X_SCB_FCS flip-flop, the complementary outputs Q and Q can be guaranteed b Both can realize symmetrical rising edge delay and falling edge delay. Compared with the SAFF_CP flip-flop circuit, the NMOS transistor MN6 is removed from the FFSEDHD1X_SCB_FCS flip-flop, which can greatly improve the settling time characteristics of the circuit. At the same time, the circuit stru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com