Zero greeve controller with universal series bus interface

A universal serial bus and zero-slot controller technology, applied in the field of zero-slot controllers, can solve the problems of low interface circuit performance and restricted VXI bus performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

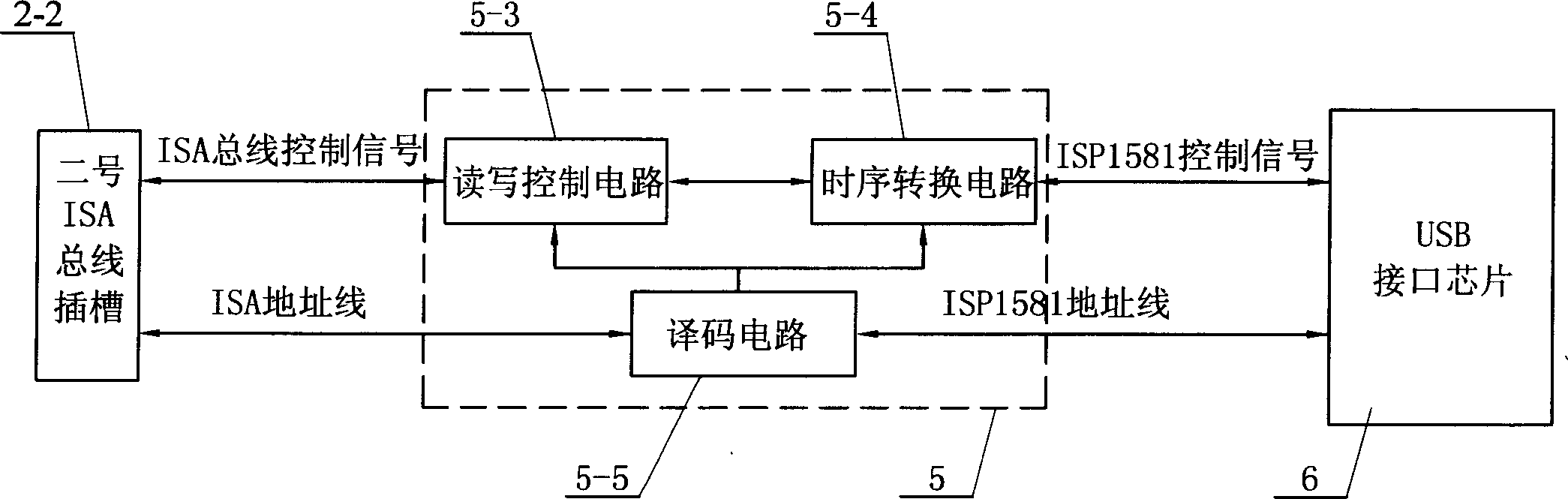

[0005] Specific implementation mode one: the following combination figure 1 This embodiment will be specifically described. It consists of a zero-slot CPU circuit 1, a zero-slot base plate 2, an ISA / USB control signal conversion circuit 5 and a USB interface chip 6, and the zero-slot CPU circuit 1 is connected to the No. 1 ISA bus slot 2-1 on the zero-slot base plate 2 In order to realize the signal communication with the zero-slot base plate 2, the signal exchange follows the ISA bus protocol, and a communication terminal of the ISA / USB control signal conversion circuit 5 is connected to the No. 2 ISA bus slot 2-2 on the zero-slot base plate 2 Realize the exchange of bidirectional signals with the zero slot base plate 2, the other communication end of the ISA / USB control signal conversion circuit 5 is connected on a communication end of the USB interface chip 6 to realize the conversion of the address signal and the control signal, and the other communication end of the USB i...

specific Embodiment approach 2

[0006] Specific embodiment two: below in conjunction with Fig. 2 and image 3 This embodiment will be specifically described. The difference between this embodiment and Embodiment 1 is: the USB interface chip 6 selects the chip ISP1581, and the pin 5 and pin 6 of the USB interface chip 6 respectively receive the data and signals transmitted by the external controller through the USB cable and send data to the outside and signal. The ISA / USB control signal conversion circuit 5 is made up of a programmable logic chip 5-1 and a dial switch 5-2. The model of the programmable logic chip 5-1 is EPM7128STC100-10, which is manufactured by Altera Corporation. The dial switch 5- 2 consists of eight-position resistor row SWR and eight-position switch SW1, pin 1 of eight-position resistor row SWR is connected to power supply VCC, pin 2 of eight-position resistor row SWR is connected to pin 9 of eight-position switch SW1 and programmable logic chip 5-1 The pin 60 of the eight-bit resisto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com