Method for manufacturing a semiconductor device

A semiconductor and device technology, which is applied in the field of manufacturing semiconductor devices, can solve the problems of shorter channel length, lower threshold voltage, and inability to effectively reduce junction leakage current, so as to achieve the effect of reducing junction leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

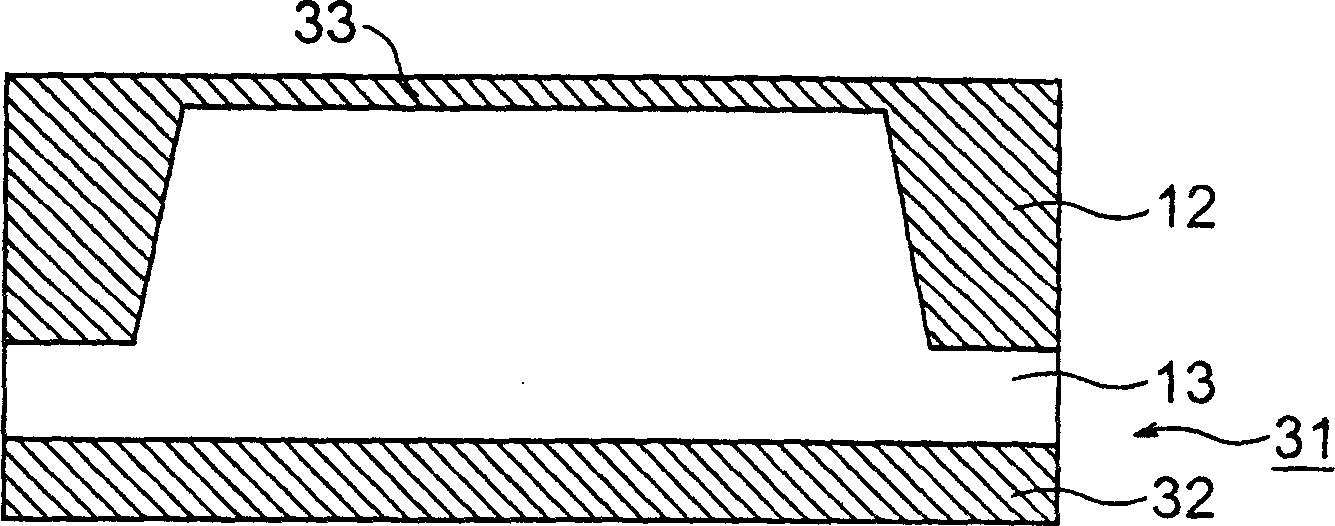

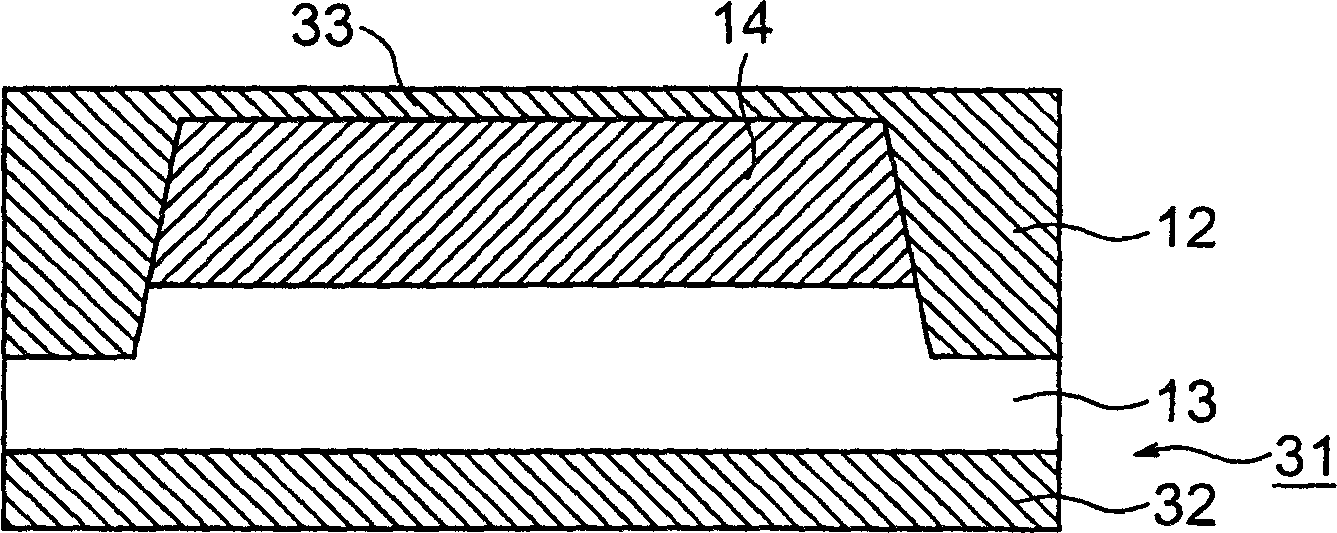

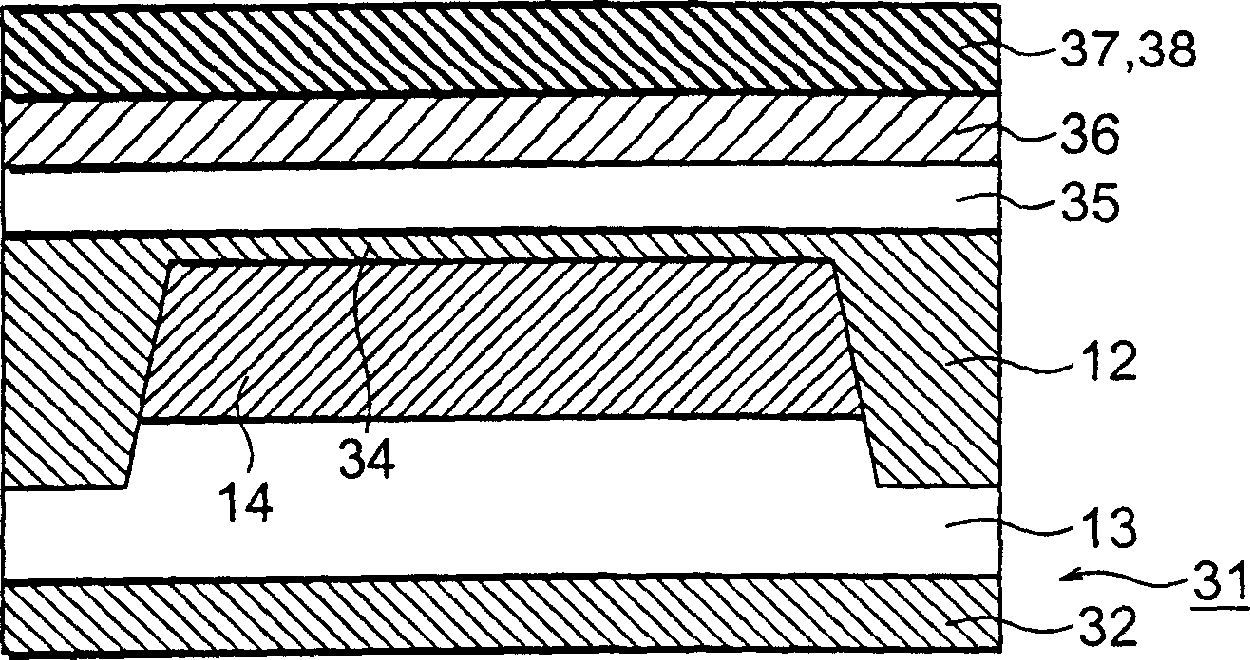

[0028]The present inventors conducted the following first and second experiments prior to the present invention. In the first experiment, a predetermined dose of dopant was implanted into the semiconductor substrate, and thereafter, heat treatment for redistributing the dopant was performed. By obtaining the relationship between the number of remaining defects and the amount of heat treatment, research was conducted on the number of crystal defects remaining after heat treatment. The term "amount of heat treatment" used herein means an amount approximated by the product of the time interval for performing the heat treatment and the temperature. A first experiment was performed while varying the dose of implanted dopants. It was thus found that the dependence of the number of defects remaining after heat treatment on the amount of heat treatment varies depending on the dose. Figure 8 shows the relationship between the normalized number of remaining defects and the normalized...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com