High matching low power consumption low noise CDS cirecuit structure

A technology with circuit structure and low power consumption, which can be used in improving amplifiers to reduce noise impact, TV, color TV, etc. It can solve the problems of system chip battery life reduction, increase of image sensor chip area, difficulty in obtaining readout rate, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

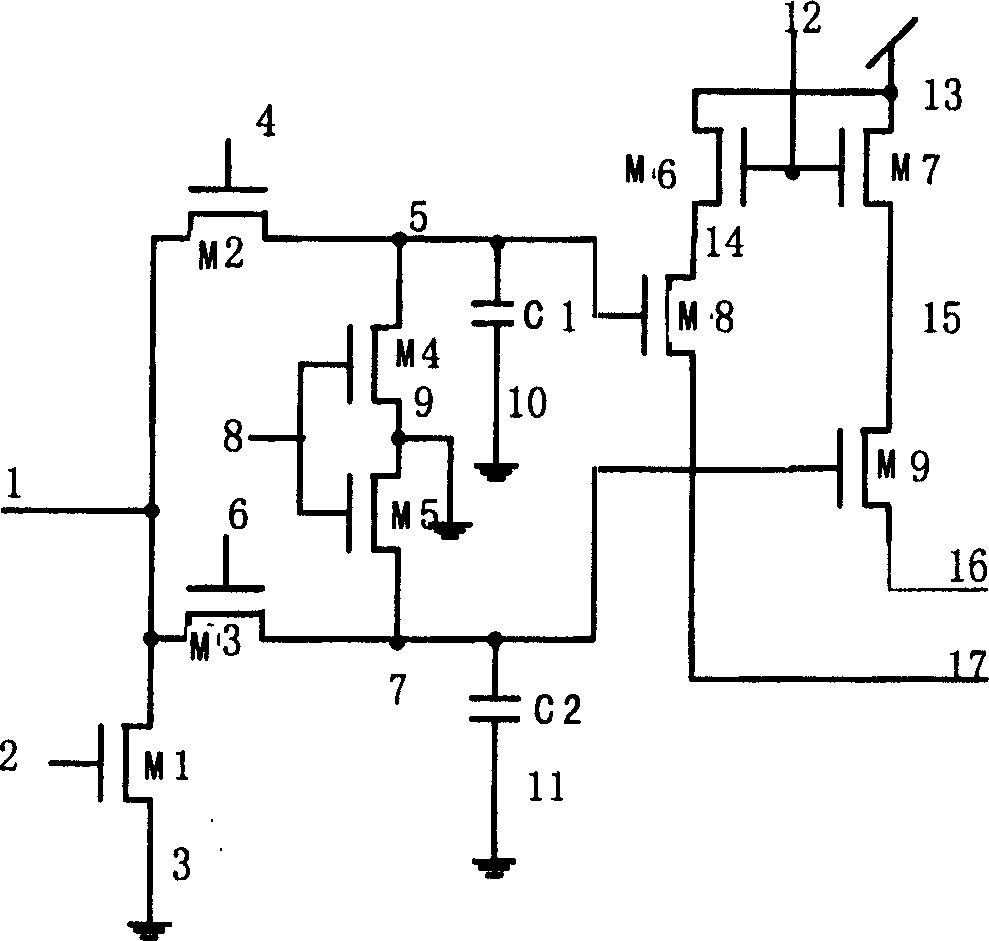

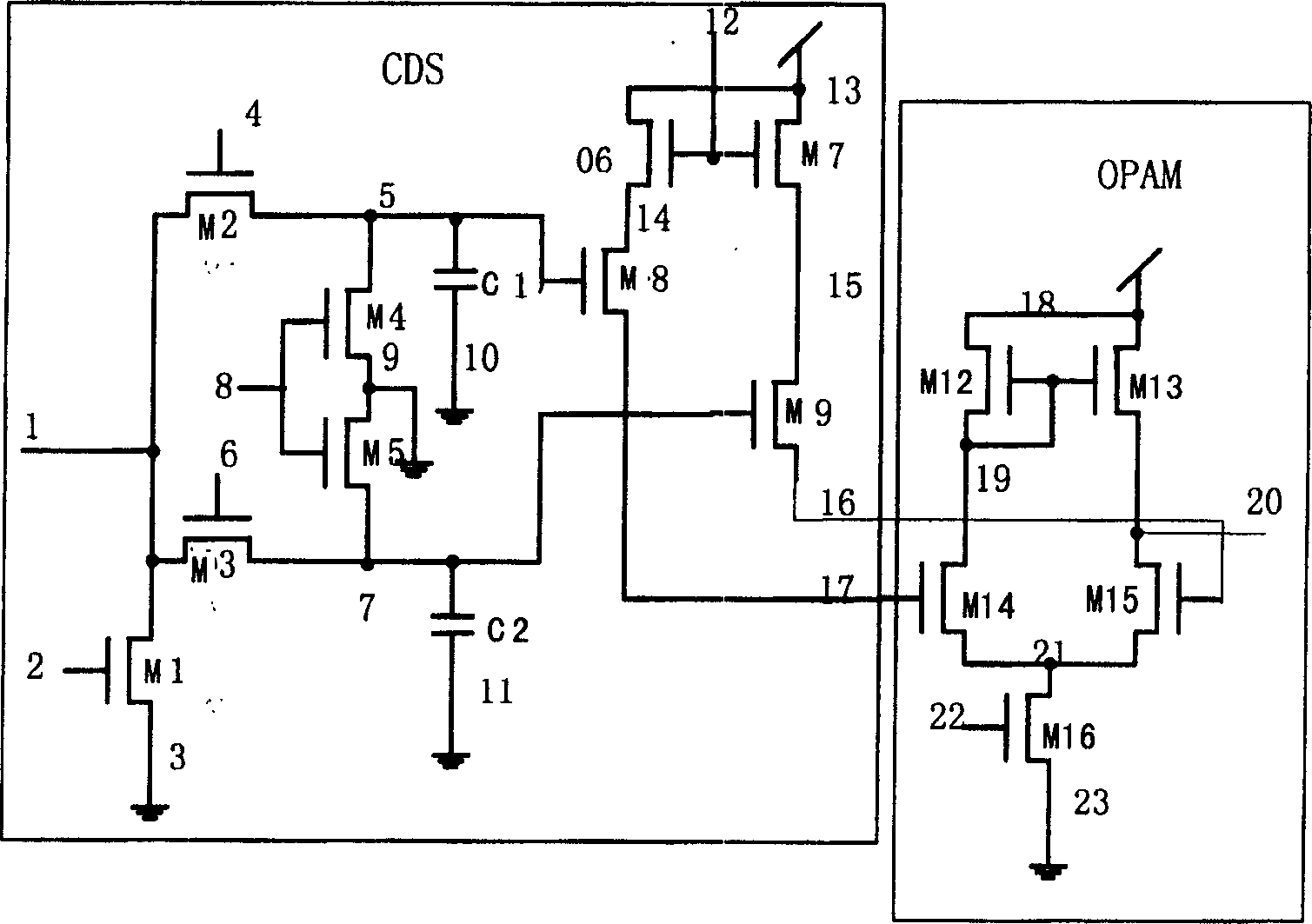

[0019] refer to figure 1 , figure 1 It is a schematic diagram of the circuit structure of the present invention. The present invention is a low-power correlated double-sampling circuit structure. This structure has the advantages of good matching, low power consumption, and low noise, including:

[0020] The proposed correlated double sampling circuit is composed of bias transistor M1, sampling switching transistors M2 and M3, sampling capacitors C1 and C2, snap transistors M4 and M5, column selection transistors M6 and M7, source follower transistors M8 and M9, two of them Sampling switch transistors M2 and M3 and column selection transistors M6 and M7 use P-type MOS transistors, and the rest use N-type MOS transistors. The source of the bias transistor M1 is grounded 3, the gate is connected to the bias voltage terminal 2, and the drain is connected to the input terminal 1; the drains of the two sampling switching transistors M2 and M3 are connected to the signal input term...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com