Quasi-dual-gate field effect transistor

A field-effect transistor and gate-behind technology, applied in the field of microelectronic semiconductors, can solve the problems of large parasitic series resistance of FinFET, affecting large-scale integration of devices, serious hot electron effect, etc. The effect of the restriction on the width of the isolation area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

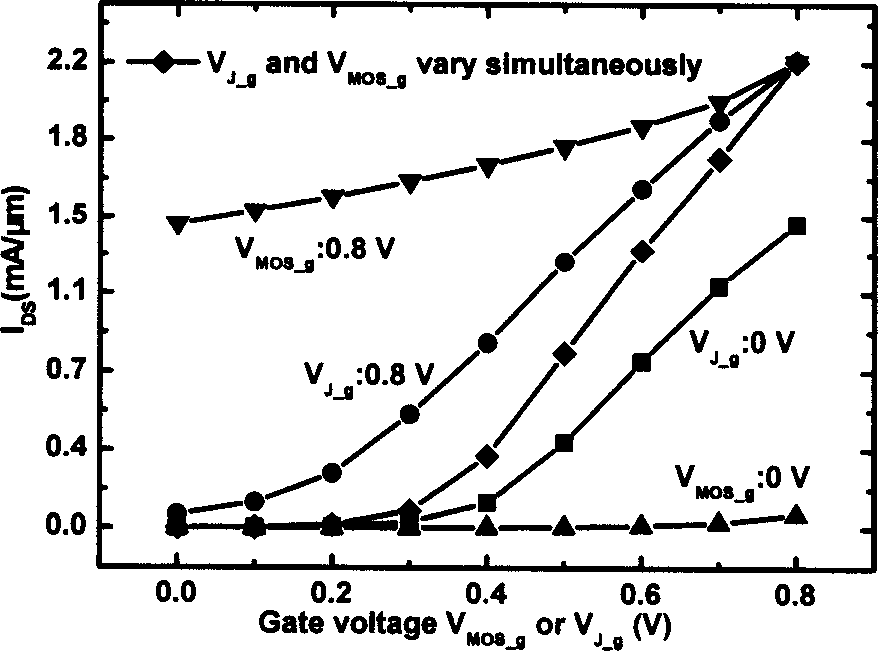

Image

Examples

Embodiment Construction

[0019] Specific implementation examples

[0020] reference figure 2 , The quasi-dual gate field effect transistor of the present invention includes a source region 3, a drain region 3, an isolation region 6, a body 4, a front gate 1 and a rear gate 5, and an isolation region 6 is provided between the source and drain regions 3 and the body 4. The front gate 1 is polysilicon, a layer of gate oxide 2 is provided between the front gate 1 and the body 4, the back gate 5 is doped monocrystalline silicon, and the back gate 5 and the body 4 are directly connected to form a PN junction. Due to the connection between the rear gate and the body, the width of the body can be controlled within the range of 3 / 5 to 1 of the length of the front and rear gates, and the width of the isolation region can also be 2 to 4 times the length of the front and rear gates. The length can be controlled to be 1 to 1.5 times the length of the front and rear grids.

[0021] The design parameters of the present...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com