Low power dissipation group associated cache memory adopting improved time sequency

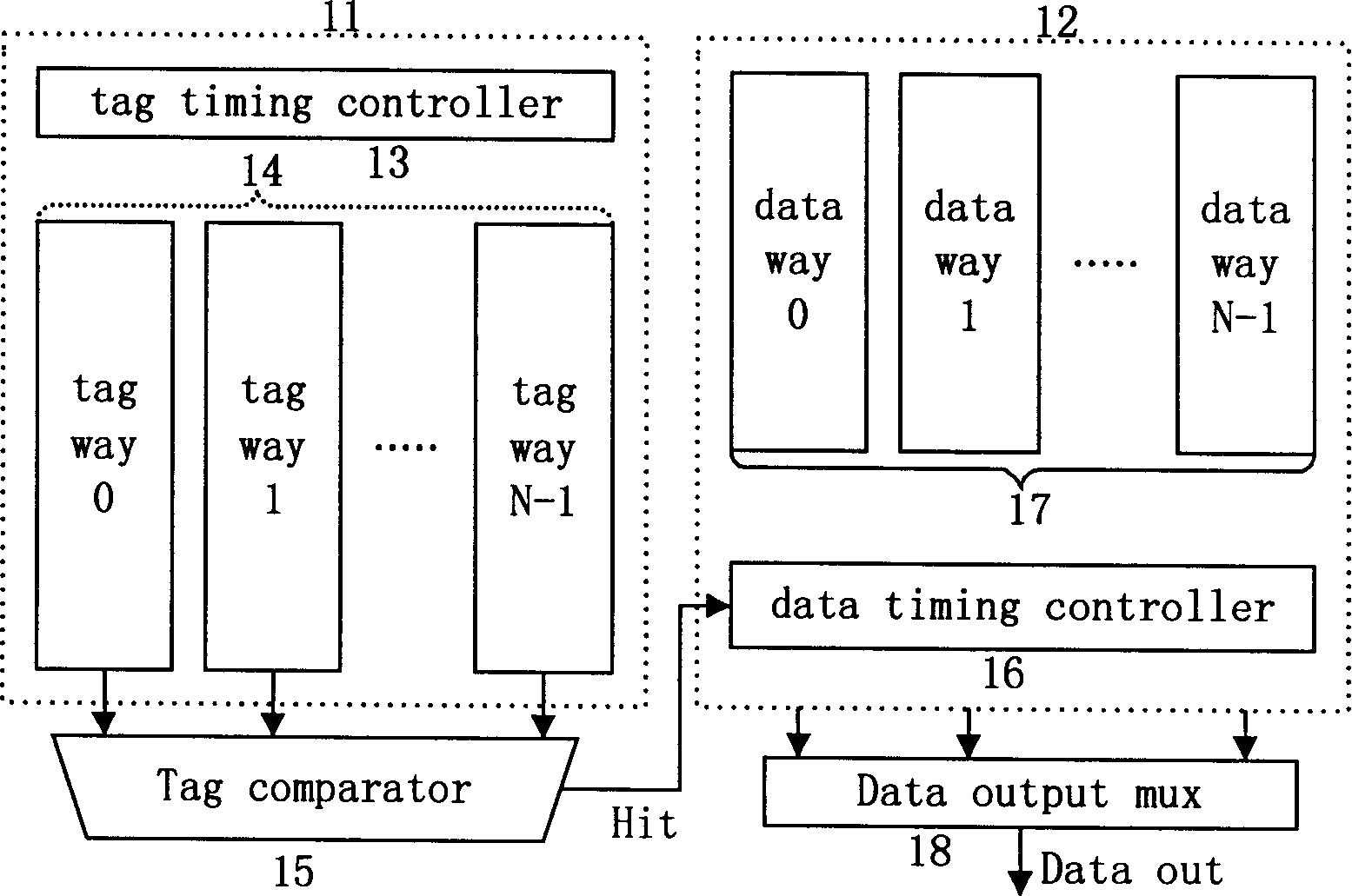

A set-associative, low-power technology, applied in the field of multi-way set-associative high-speed cache memory, can solve the problems of adding look-up tables, increasing hardware circuit complexity, wasting datasram read power consumption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be described in further detail below in conjunction with the accompanying drawings.

[0025] Figure 4 Shown are the load operation timing diagrams of three different sets of associative caches, where, Figure 4 (a) is the load operation sequence of the traditional parallel read set associative cache, Figure 4 (b) is the load operation timing of PSACache, Figure 4 (c) is the load operation sequence of the set associative cache of the present invention.

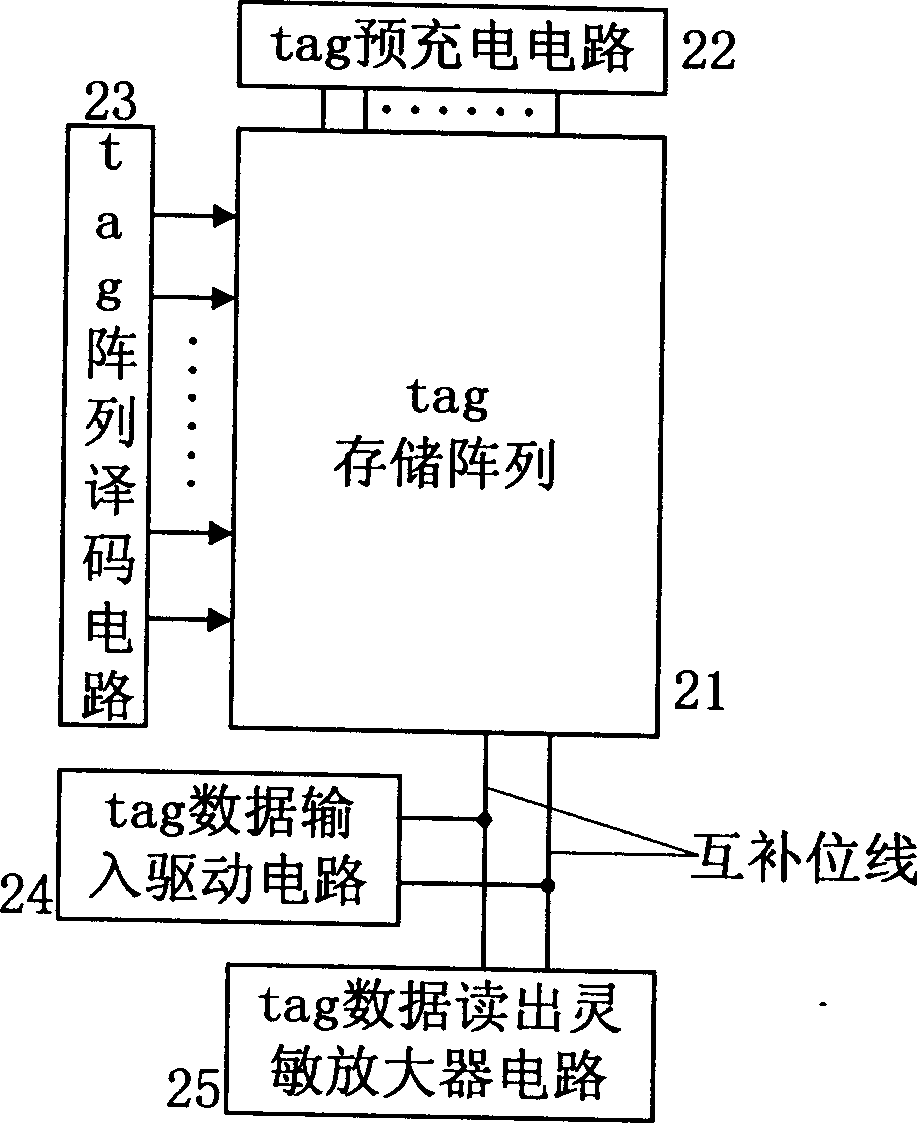

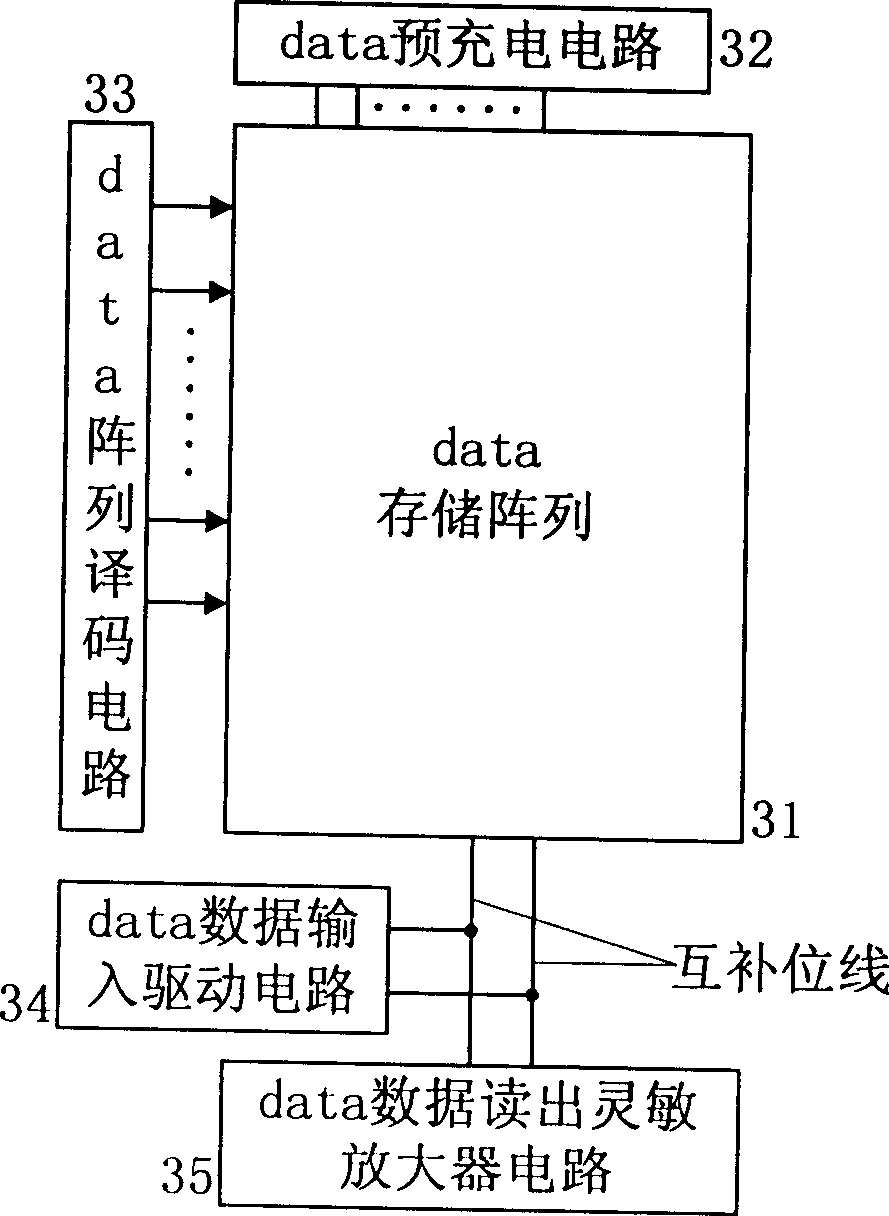

[0026] The critical path circuit of load operation of the present invention sees Figure 6 Shown, timing control signal diagram see Figure 7 shown. In the following descriptions, it is assumed that the high level is the active level for the control signal. After a load cycle starts, the global address signal addr of the cache becomes the address to be read and written in this cycle, Figure 7 The middle load signal becomes high, indicating that the load operation of the cache is perf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com