Monolithic heterogeneous integrated structure and preparation method thereof

A heterogeneous, monolithic technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of Si-based wafer fabrication of devices and circuits, and achieve improved anti-signal crosstalk and anti-radiation. Capability, high-density integrated circuit design, the effect of realizing integrated circuit design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

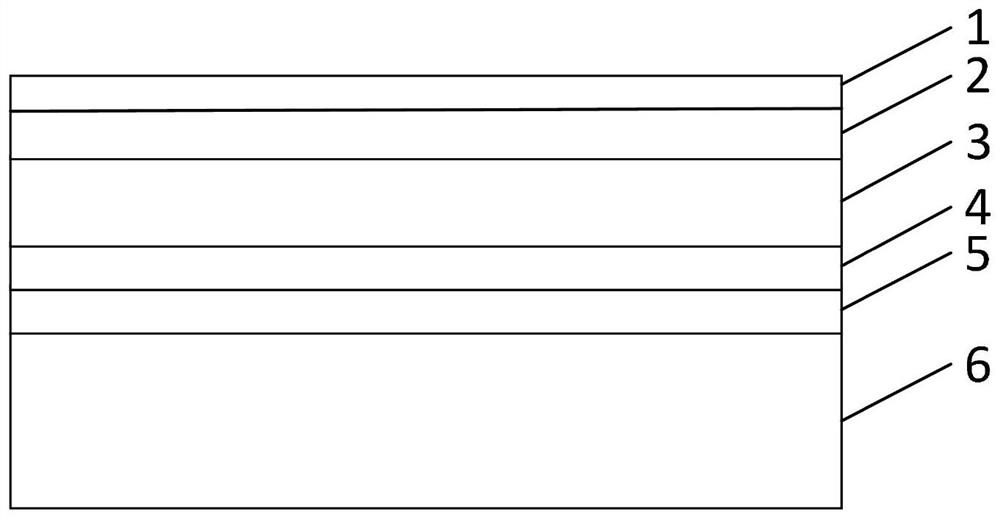

[0055] In this embodiment, a monolithic heterogeneous integrated structure is provided, such as figure 1 shown, including:

[0056] The substrate 6, the nucleation layer 5, the buffer layer 4, the compound semiconductor layer 3, the oxide layer 2 and the silicon layer 1 are sequentially arranged from bottom to top;

[0057] The silicon layer 1 is silicon with a lattice of 100 faces, so that devices and circuits can be fabricated on the silicon layer.

[0058] In an alternative embodiment, the nucleation layer includes at least one of GaN, AlGaN, and AlN, and the buffer layer is GaN, so as to grow the compound semiconductor layer. The compound semiconductor layer is GaN, which has properties such as wide direct band gap, strong atomic bond, high thermal conductivity, good chemical stability, and strong anti-irradiation ability, and can prepare optoelectronic devices, high-temperature and high-power devices and high frequency microwave devices. Of course, the compound semicon...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com