Wafer-level system packaging structure and packaging method

A system packaging and wafer-level technology, applied in the direction of manufacturing microstructure devices, processing microstructure devices, TV system components, etc., can solve the problems of low packaging efficiency, improve packaging efficiency, simplify the process flow, and prevent horizontal spillover effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

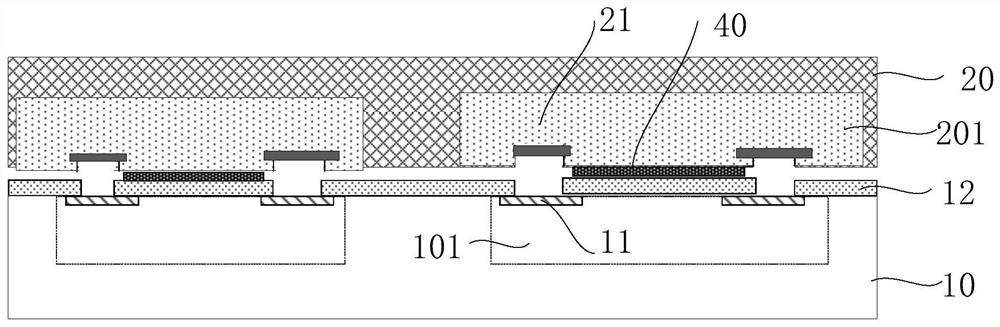

[0035] This embodiment provides a wafer-level system packaging method, including the following steps:

[0036]S01: Provide a first device wafer, a plurality of first device modules are formed inside the first device wafer, the first device wafer has a front surface and a back surface, the front surface is exposed to electrically connect the first device a plurality of first pads of the module and recessed on the front surface;

[0037] S02: Provide a second device wafer, a plurality of second device modules are formed inside the second device wafer, the second device wafer includes opposite upper and lower surfaces, and the upper surface exposes electrical connections the second device module and a plurality of second pads recessed on the upper surface;

[0038] S03: bonding the first device wafer and the second device wafer, so that the first pad and the second pad are relatively surrounded by a gap;

[0039] S04: Use an electroplating process to form conductive bumps in th...

Embodiment 2

[0066] refer to Figure 5 The difference between this embodiment and Embodiment 1 is that the back of the first device module 201 has a first electrical connection structure 22, and before or after cutting the first device wafer 20, a first chip 50 or a third device wafer is provided, The first chip 50 or the third device wafer is electrically connected to the first electrical connection structure 22 .

[0067] In this embodiment, the first electrical connection structure 22 is formed on the back of the first device module 201 . After the first device wafer is cut, the first chip 50 is provided; then the first chip 50 is bonded to the first device module 201 . combine. The first chip 50 may be electrically connected to one first device module 201 , or may be electrically connected to two or more first device modules 201 . The figure shows a situation in which the first chip 50 is electrically connected to one first device module 201 . It should be noted that, to electricall...

Embodiment 3

[0070] refer to Image 6 The difference between this embodiment and Embodiment 2 is that the lower surface of the second device module 101 has a second electrical connection structure 13, and the method further includes: providing a second chip or a fourth device wafer 100, The second chip or the fourth device wafer 100 is electrically connected to the second electrical connection structure 13 .

[0071] The lower surface of the second device module 101 has a second electrical connection structure 13 , the fourth device wafer 100 includes a plurality of second chips 51 , and the second electrical connection structure 13 is electrically connected to the second chips 51 . First, the lower surface of the second device wafer 10 is thinned to expose the second electrical connection structure 13 , and then the fourth device wafer 100 is bonded on the second device wafer 10 , and the second chip 51 is connected to the second device wafer 10 . For the electrical connection of the sec...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Area | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com