Simulation method and simulation system of integrated circuit

A simulation method and integrated circuit technology, applied in electrical digital data processing, instruments, calculations, etc., can solve problems such as excessive file size, affecting the simulation speed and simulation accuracy of integrated circuits, and achieve the effect of improving simulation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

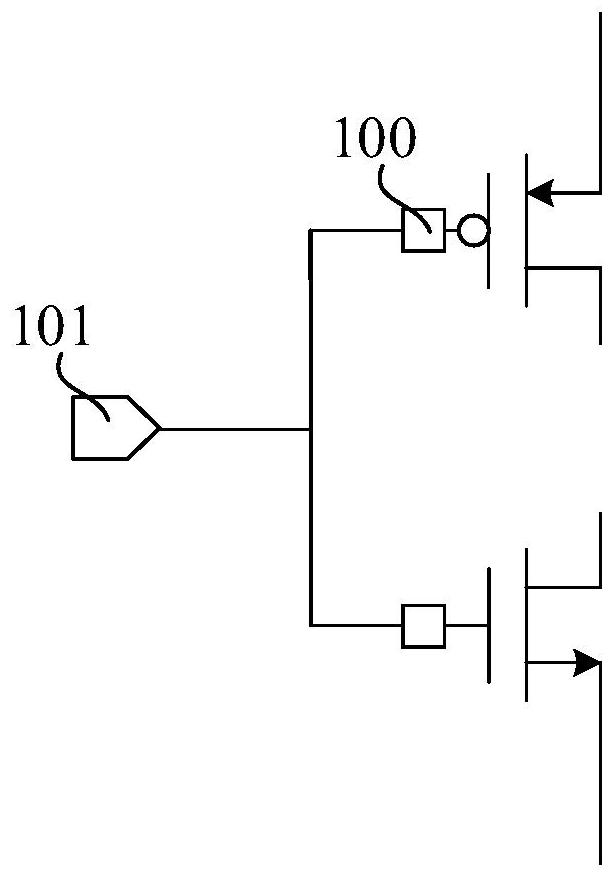

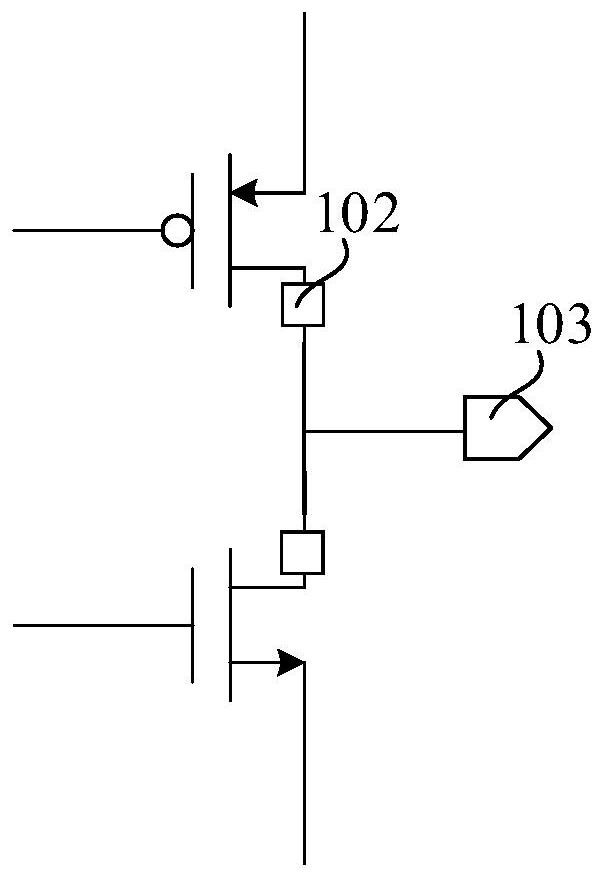

[0032] It can be known from the background art that the simulation accuracy for simulating an integrated circuit needs to be improved.

[0033] The present disclosure provides a simulation method for an integrated circuit and a simulation system thereof. In the simulation method, parasitic parameter information of at least part of the semiconductor device in the unit list is imported on the basis of the initial netlist, which is beneficial to the operation of the real simulation integrated circuit. The parasitic effect between various semiconductor devices is beneficial to improve the simulation accuracy of the simulation of the integrated circuit.

[0034] The embodiments of the present disclosure will be described in detail below with reference to the accompanying drawings. However, those of ordinary skill in the art can appreciate that, in the various embodiments of the present disclosure, many technical details are provided for the reader to better understand the embodimen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com