Manufacturing method of semiconductor structure and semiconductor structure

A manufacturing method and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve the problem of difficult diffusion of Al or La elements in the dielectric layer, affecting the access performance of DRAM devices, and increasing the interlayer resistance value, etc. problem, to optimize performance, reduce quantum tunneling effect, and reduce the effect of interlayer resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

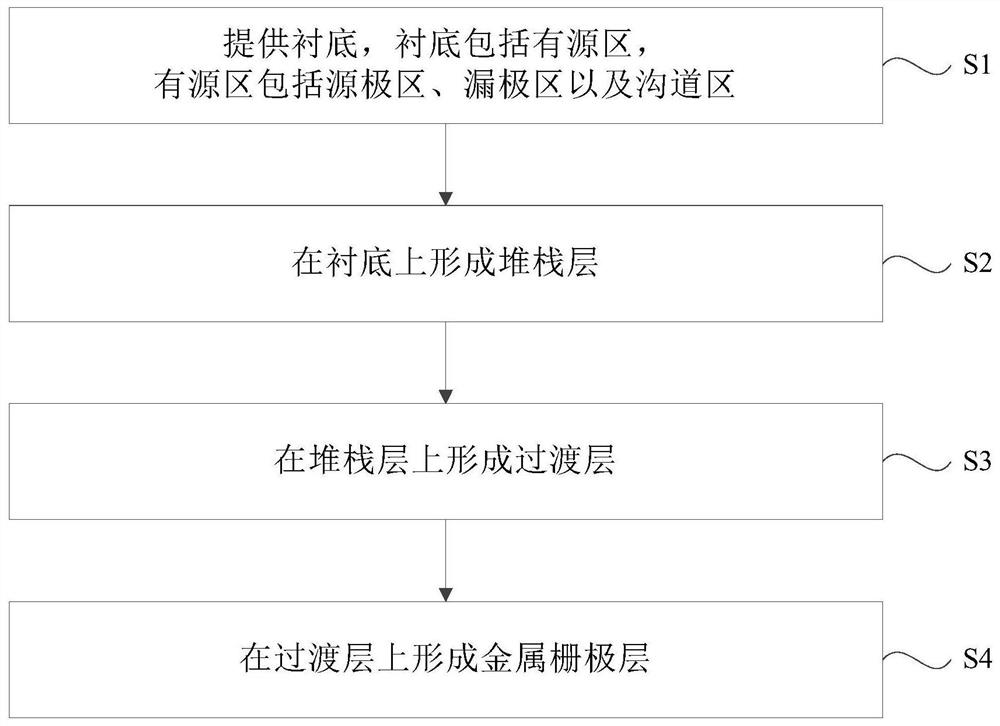

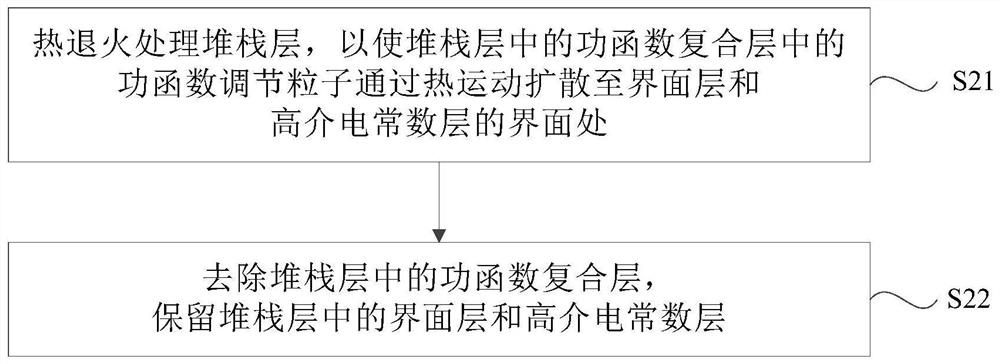

Method used

Image

Examples

Embodiment Construction

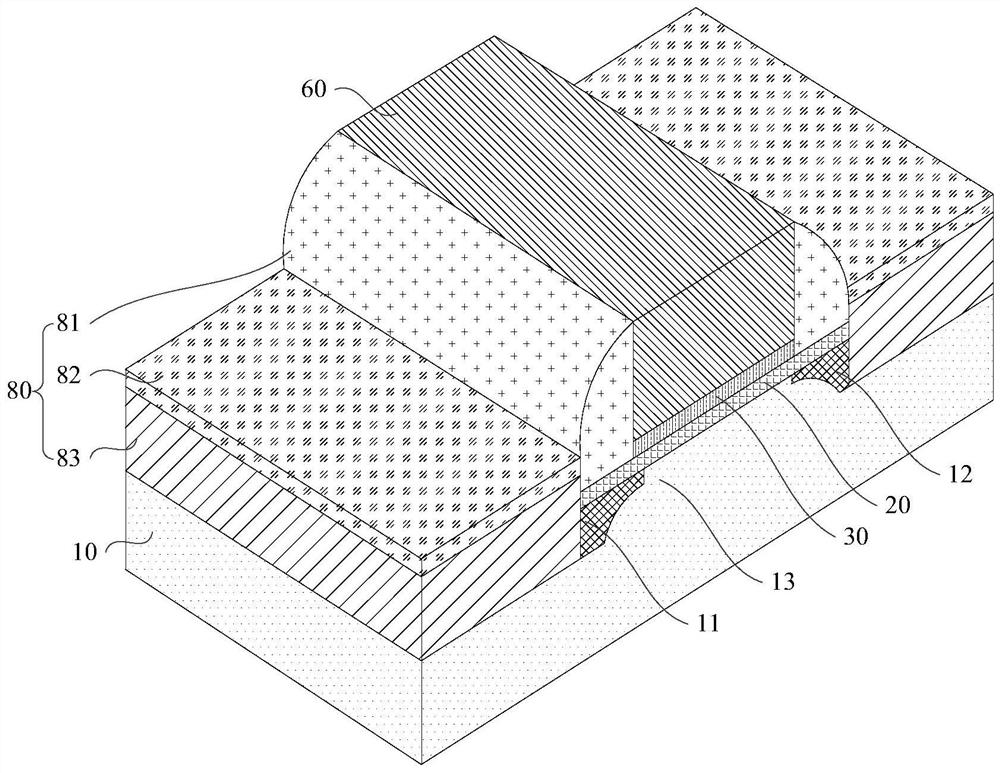

[0077] The inventor of the present application found in the actual research process that the current HKMG transistor structure includes a sequentially stacked substrate, a silicon oxide layer, a high dielectric constant dielectric layer, a work function adjustment layer and a metal gate. where the work function adjustment layer is La x O y (Al x O y ) layer and TiN layer composite layer, TiN layer is generally made by PVD method (Physical Vapor Deposition, physical vapor deposition), and LaO (AlO) layer is generally made by ALD method (Atomic layer deposition, atomic layer deposition), to Controls the thickness of the LaO(AlO) layer. However, the current PVD and ALD processes in different equipment are easy to cause, and the oxygen atoms in the LaO (AlO) prepared by ALD are easily diffused into the TiN layer, resulting in the formation of oxide TiO in the TiN layer, which makes the Al element or La Elements are more difficult to diffuse into the dielectric layer. And in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com