Vertical transistor, display pixel, vertical light-emitting transistor and display panel

A light-emitting transistor, vertical technology, applied in semiconductor devices, electrical solid state devices, semiconductor/solid state device manufacturing, etc., can solve problems such as working current adjustment, low device performance, and inability to reduce working voltage, so as to reduce working voltage and device good performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

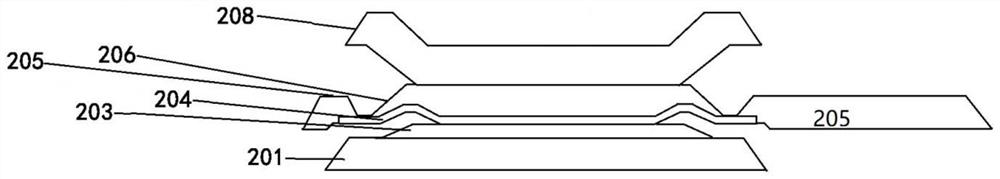

[0043] The present disclosure embodiment provides a display pixel, wherein the cross-sectional structure is illustrated as Figure 7 shown, at least includes:

[0044] Source layer 201, gate layer, drain layer 208, first active layer 203, second active layer 206; source layer, first active layer, gate layer, second active layer, drain layer in the vertical direction of stacking settings, gate layer includes the first gate structure 204 and the second gate structure 205, the first active layer, the second active layer and the first gate structure to form a Schottky contact, vertical direction is perpendicular to the direction of the substrate; the first gate structure is located in the vertical stacking connection area, There is a first active overlapping region with the source layer in the vertical direction, and there is a second active overlapping region with the gate layer in the vertical direction, the first gate structure adopts a sparse gate material or has a sparse skeleton ...

Embodiment 2

[0050] The present disclosure embodiment also provides a pixel circuit, the cross-sectional structure of which is illustrated as Figure 8 as shown, relative to Figure 7 As far as the pixel circuit shown, the basic structure of the source layer 201, gate layer, drain layer 208, the first active layer 203, the second active layer 206 remains unchanged, i.e., at least comprising:

[0051] Source layer 201, gate layer, drain layer 208, first active layer 203, second active layer 206; source layer, first active layer, gate layer, second active layer, drain layer in the vertical direction of stacking settings, gate layer includes the first gate structure 204 and the second gate structure 205, the first active layer, the second active layer and the first gate structure to form a Schottky contact, vertical direction is perpendicular to the direction of the substrate; the first gate structure is located in the vertical stacking connection area, There is a first active overlapping region wi...

Embodiment 3

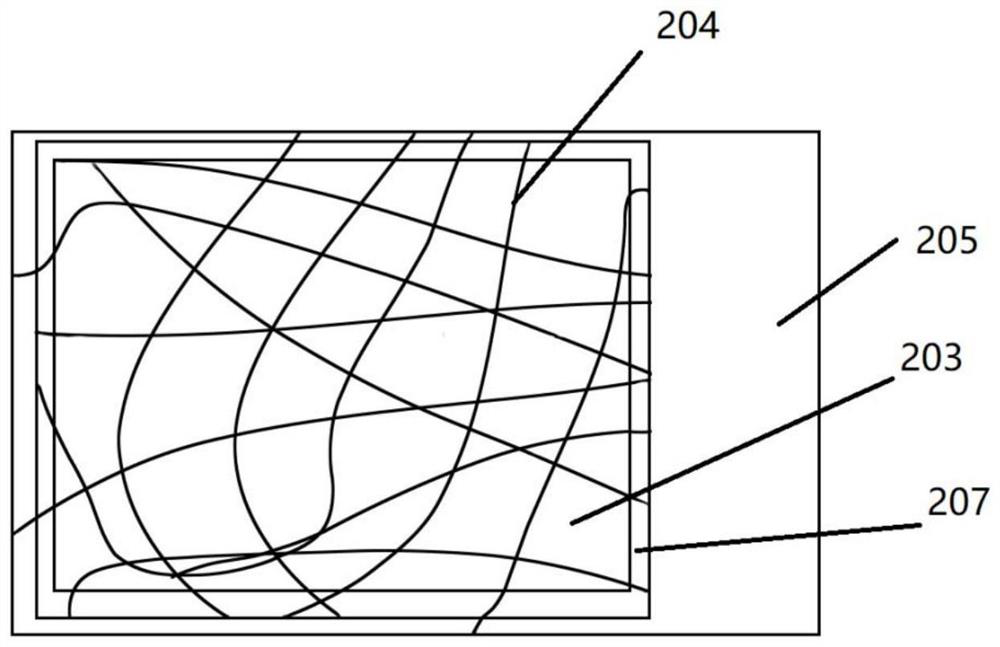

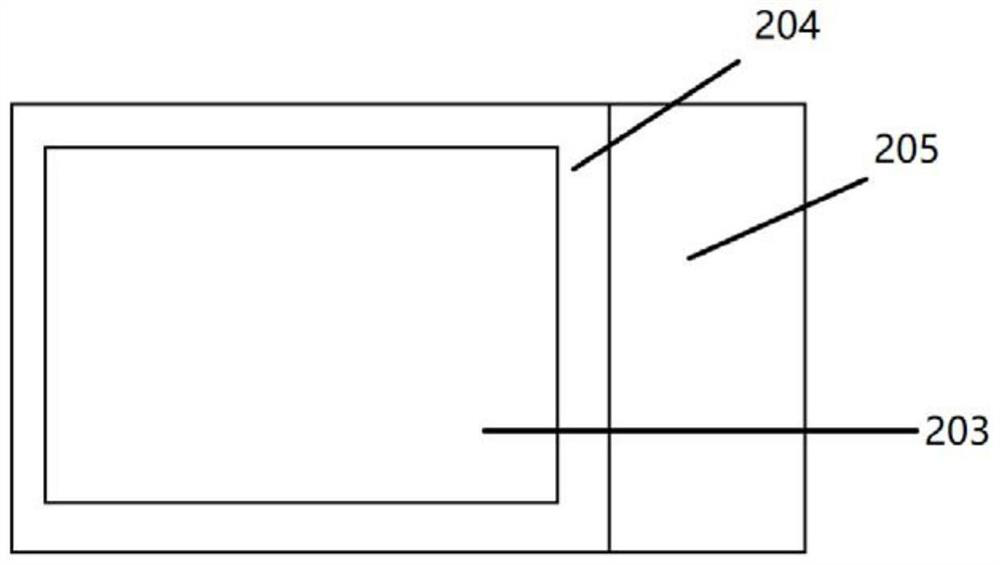

[0055] The present embodiment of the present disclosure also provides a vertical type light emitting transistor, the profile structure of which is illustrated as shown Figure 9 (emits light through the drain layer, so in the image looks equivalent to omitting the drain layer) as shown, including at least:

[0056] Source layer 201, gate layer, drain layer 208, first active layer 203, second active layer 206; source layer, first active layer, gate layer, second active layer, drain layer in the vertical direction of stacking settings, gate layer includes the first gate structure 204 and the second gate structure 205, the first active layer, the second active layer and the first gate structure to form a Schottky contact, vertical direction is perpendicular to the direction of the substrate; the first gate structure is located in the vertical stacking connection area, There is a first active overlapping region with the source layer in the vertical direction, and there is a second acti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com