Formation method of semiconductor structure

A semiconductor and graphics technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of increasing the difficulty and complexity of integrated circuits, improve the problem of serious lateral diffusion, improve the verticality of side walls and Line width accuracy, the effect of improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] At present, the electrical performance and reliability of the device still need to be improved. Combining with the formation method of a semiconductor structure, the reasons why its electrical performance and reliability still need to be improved are analyzed.

[0032] refer to Figure 1 to Figure 4 , shows a structural schematic diagram corresponding to each step in a method for forming a semiconductor structure.

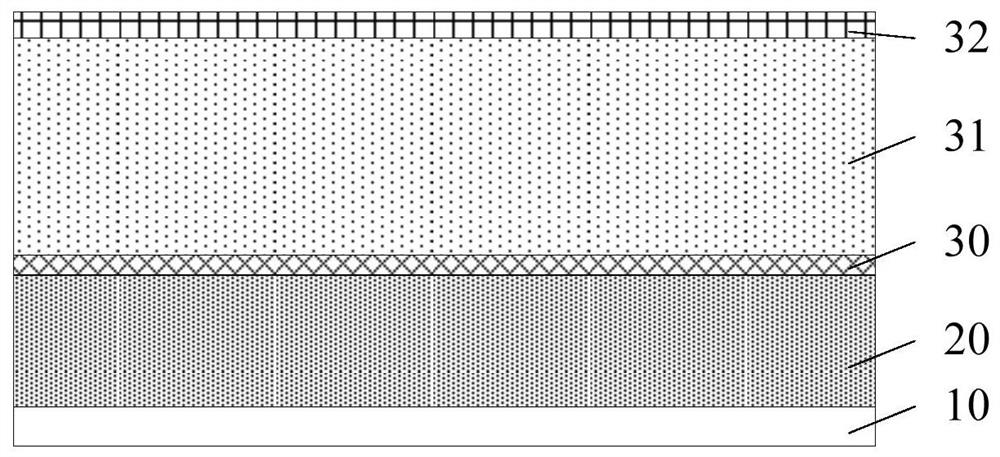

[0033] refer to figure 1 , providing a substrate 10, on which a pattern transfer material layer 20 is formed; an etch stop layer 30 is formed on the pattern transfer material layer 20; a mask layer 31 is formed on the etch stop layer 30; An anti-reflection coating 32 is formed on the mask layer 31 .

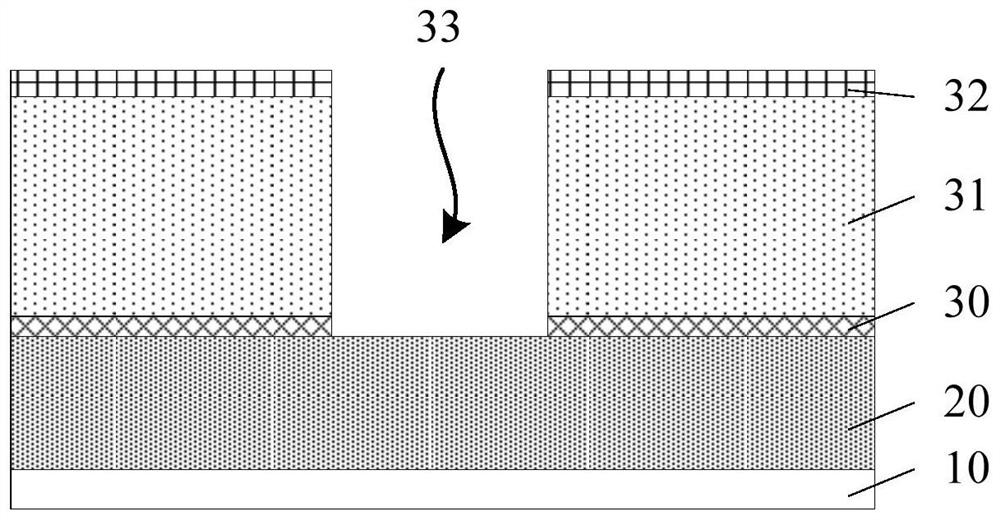

[0034] refer to figure 2 , using a patterning process to form an opening 33 in the mask layer 31 , and the opening 33 runs through the etching stop layer 30 , the mask layer 31 and the anti-reflection coating 32 .

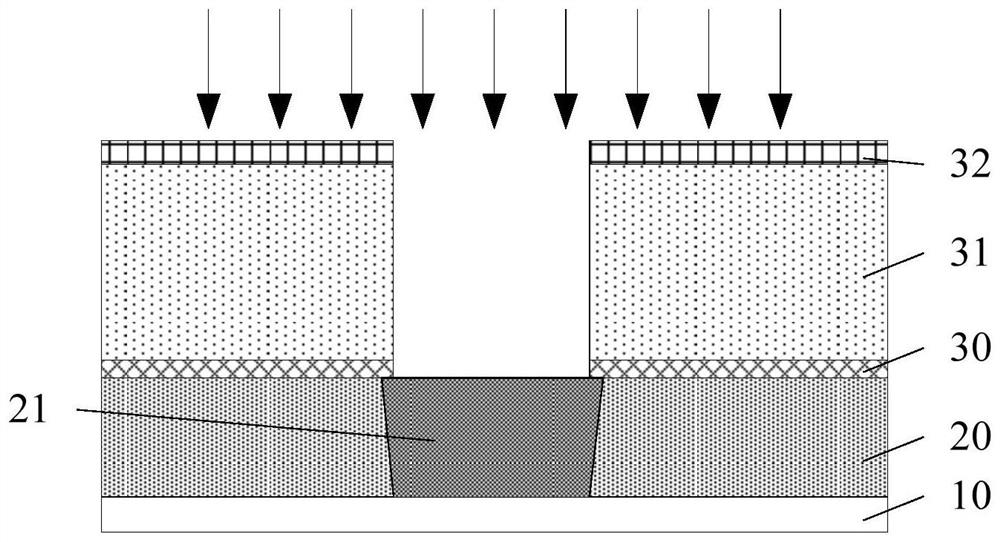

[0035] refer to image 3 , forming the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com