FPGA program upgrading method and device

A technology of program upgrade and upgrade flag, which is applied in the field of optical communication, can solve the problems affecting the gain flatness of optical fiber amplifiers and the inability to continue outputting PWM waveforms, etc., and achieve the effect of making up for the lack of driving signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

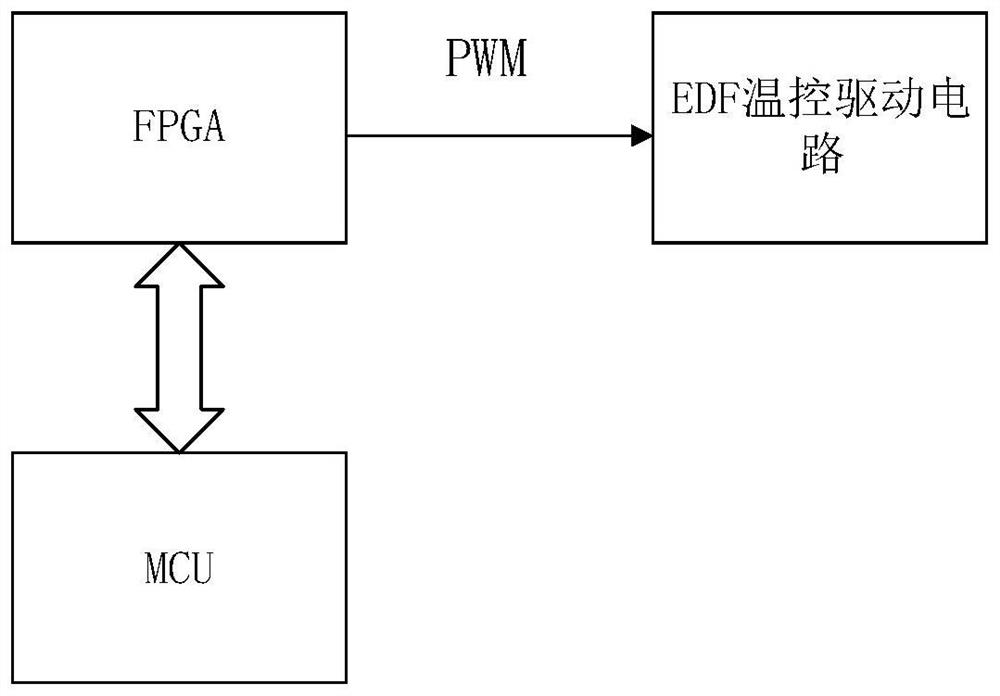

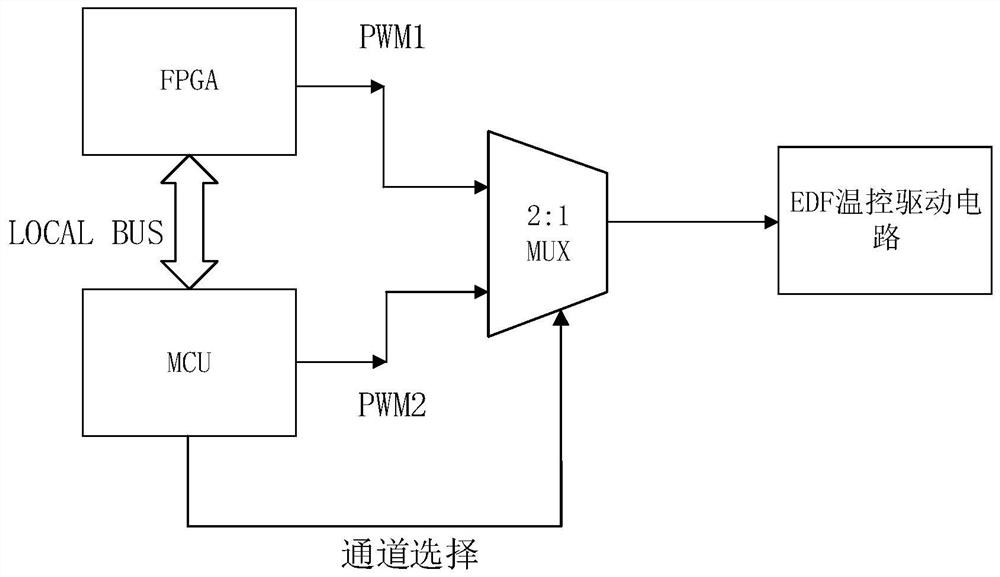

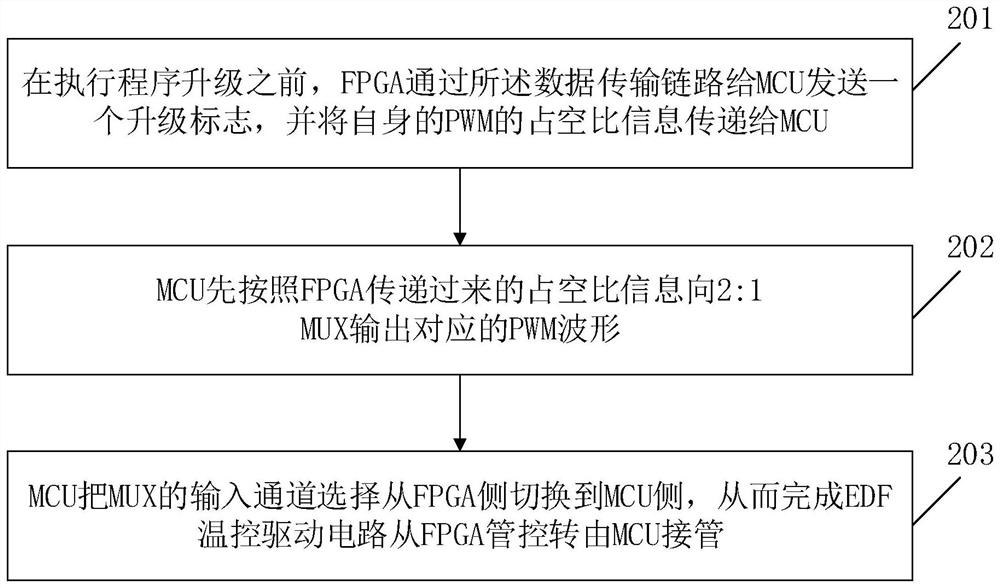

[0046] Embodiment 1 of the present invention provides a method for upgrading FPGA programs, such as figure 2 As shown, a data transmission link is established between the MCU and the FPGA. The 2:1MUX is controlled by the MCU. The two input ports of the 2:1MUX are respectively coupled to the PWM output port of the FPGA and the PWM output port of the MCU. The 2:1MUX The output port is coupled with the input end of the EDF temperature control drive circuit. During normal operation, the 2:1MUX is controlled by the MCU to select the PWM of the FPGA as the output signal of the output port of the 2:1MUX, and output to the EDFA temperature control circuit; if the FPGA program enters the upgrade state, such as image 3 As shown, the methods include:

[0047] In step 201, before executing the program upgrade, the FPGA sends an upgrade flag to the MCU through the data transmission link, and transmits the duty cycle information of its own PWM to the MCU.

[0048] The data transmission ...

Embodiment 2

[0076] Such as Image 6 As shown, it is a schematic diagram of the structure of the FPGA program upgrading device according to the embodiment of the present invention. The device for upgrading FPGA programs in this embodiment includes one or more processors 21 and memory 22 . in, Image 6 A processor 21 is taken as an example.

[0077] Processor 21 and memory 22 can be connected by bus or other means, Image 6 Take connection via bus as an example.

[0078] The memory 22, as a non-volatile computer-readable storage medium, can be used to store non-volatile software programs and non-volatile computer-executable programs, such as the FPGA program upgrade method in Embodiment 1. The processor 21 executes the FPGA program upgrade method by running the non-volatile software programs and instructions stored in the memory 22 .

[0079] The memory 22 may include a high-speed random access memory, and may also include a non-volatile memory, such as at least one magnetic disk stora...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com