Self-learning selection method for optimal parameters of chip module

A chip module and optimal parameter technology, which is applied in the detection of faulty computer hardware, function inspection, etc., can solve problems such as symptom confusion, manual configuration, and time-consuming debugging, and achieve the effect of reducing efficiency and time, and enhancing unity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The following is a detailed description of the patent of the present invention in combination with specific software and hardware operation construction as an example:

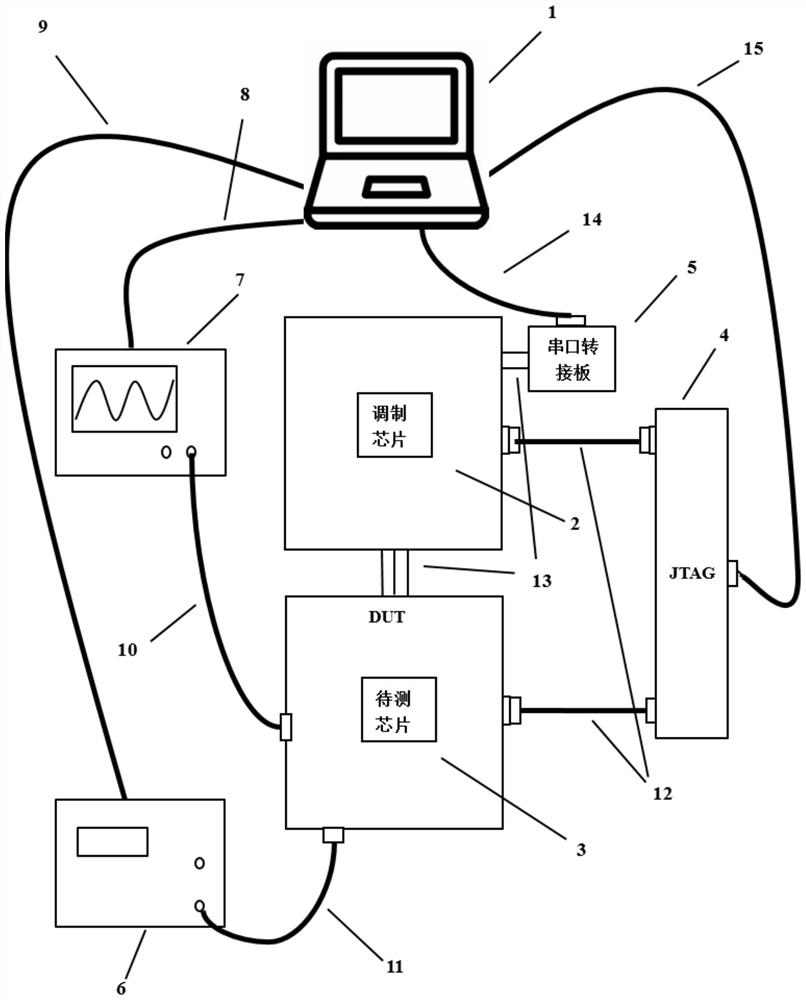

[0049] figure 1 Including 1. PC terminal, 2. On-board chip for modulation, 3. On-board chip for testing, 4. JTAG debugging channel, 5. USB to serial port adapter board, 6. Program-controlled digital power supply, 7. High-precision signal Source, 8. Instrument adapter cable (USB, COM, LAN, GPIB), 9. (same as 8), 10. Coaxial cable, 11. (same as 10), 12. Cable, 13. DuPont line, 14 .USB cable, 15. (same as 14).

[0050] The exemplary embodiments of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments:

[0051] figure 1 Shown is the overall application structure diagram of the self-learning selection method of the optimal parameter of the chip module of the present invention. The overall testing process is achieved throug...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com