Processor-oriented data transmission instruction implementation method and system

A technology of data transmission and implementation method, which is applied in the computer field, can solve the problems that Load/Store instructions cannot meet the real-time requirements, cannot exert high-speed bus performance, and cannot satisfy special-purpose processors, etc., so as to improve the operation efficiency of instructions and the speed of data processing , large addressing range, and the effect of improving operating efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be described in detail below in conjunction with specific embodiments. The following examples will help those skilled in the art to further understand the present invention, but do not limit the present invention in any form. It should be noted that those skilled in the art can make several changes and improvements without departing from the concept of the present invention. These all belong to the protection scope of the present invention.

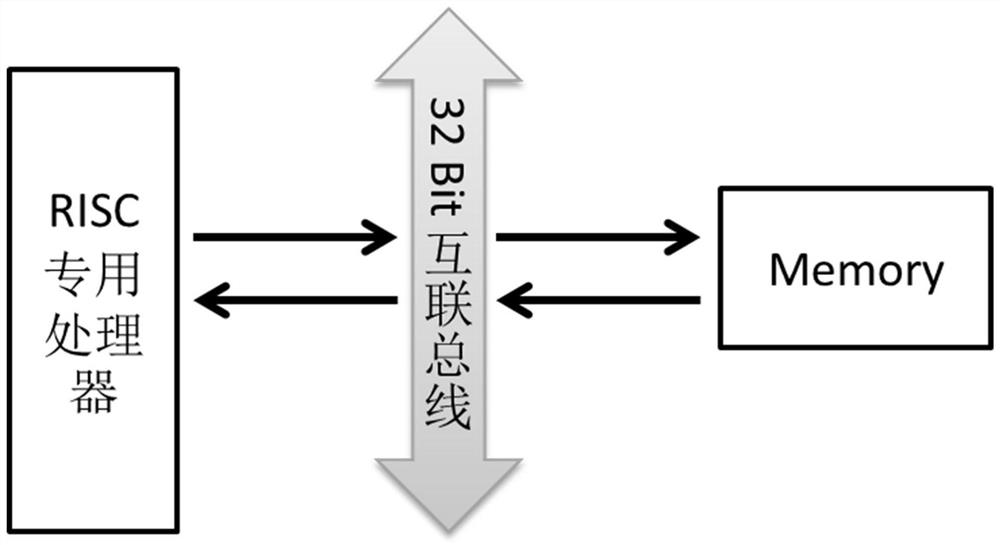

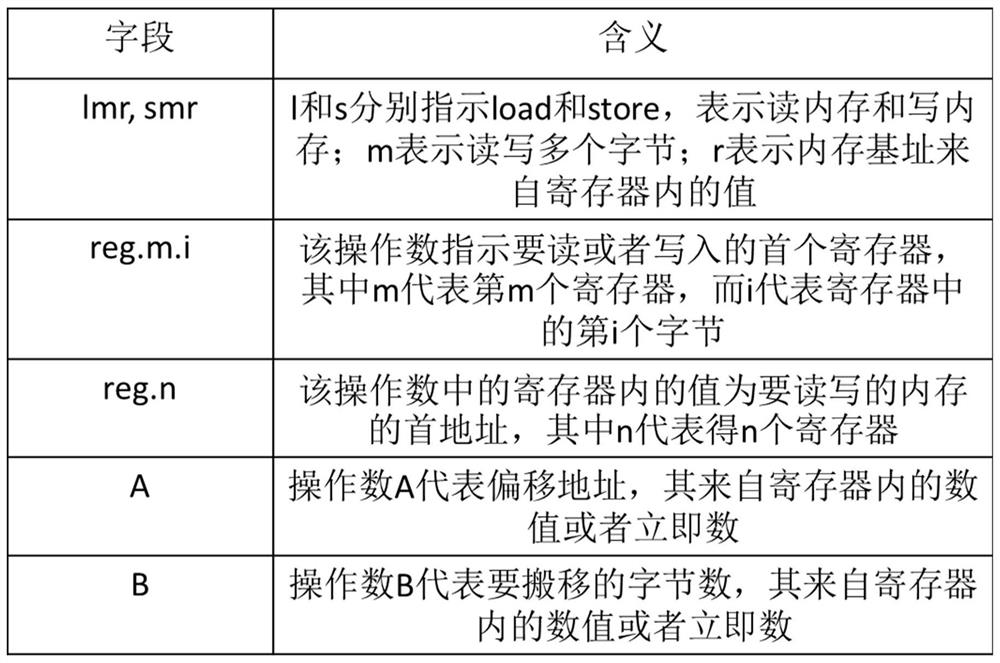

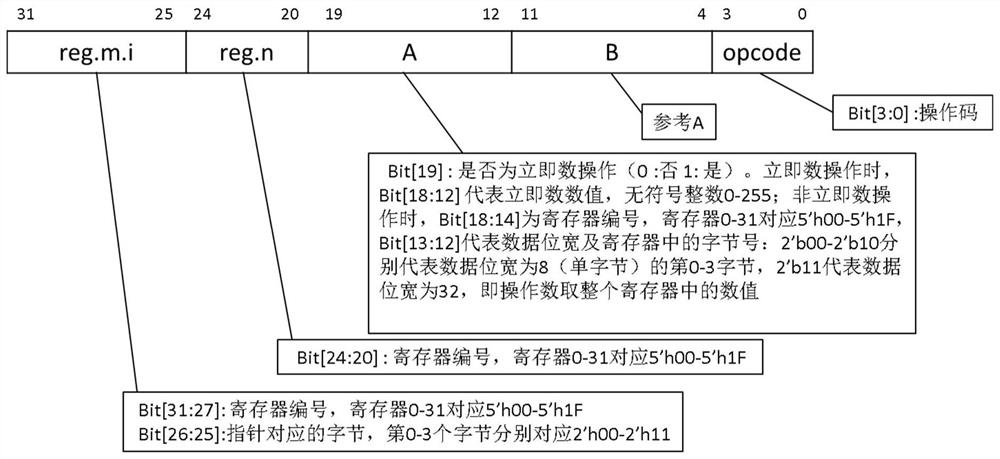

[0042] refer to figure 1 and figure 2 , in order to solve this technical problem, a high-speed multi-data transfer instruction structure is proposed, and the Load / Store in the traditional RISC instruction set is extended. This extension improves the data access speed of the processor to achieve fast response, High-speed external hardware control and dedicated data processing operations, which are suitable for special-purpose processor designs with strong real-time performance. The present invention a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com