Wiring of a semiconductor switch

A circuit layout and semiconductor technology, applied in the direction of semiconductor devices, electronic switches, circuits, etc., can solve problems such as settings that cannot be optimized, and achieve the effect of a compact structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

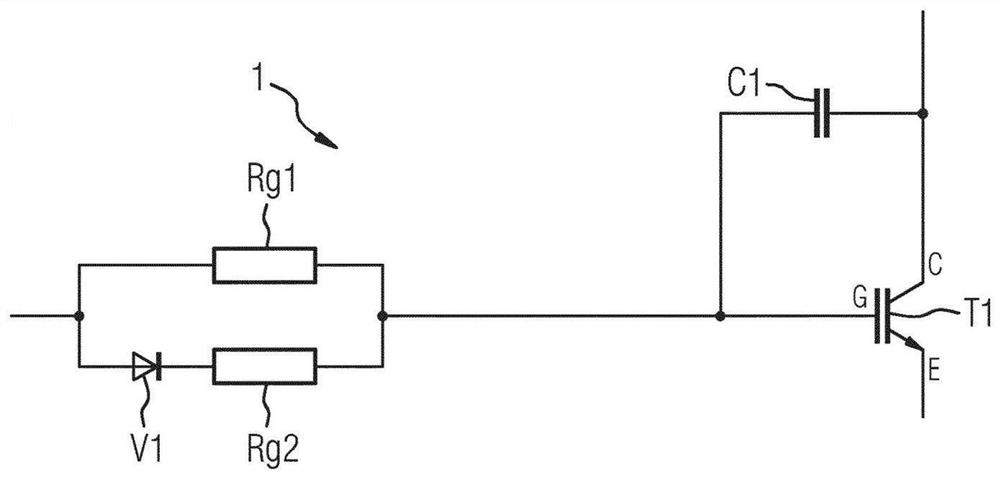

[0041] FIG. 1 shows a circuit arrangement 1 of a semiconductor switch T1 known from the prior art. The semiconductor switch T1 is, for example, a field effect transistor, in particular a MOSFET or an IGBT, and has a gate G, a collector C and an emitter E. A capacitor C1 is arranged between the collector C and the gate G. This forms a gate wiring arrangement consisting of the first gate resistor Rg1 , the second gate resistor Rg2 and the gate diode V1 , which symbolizes the gate resistors as explained above in the introduction.

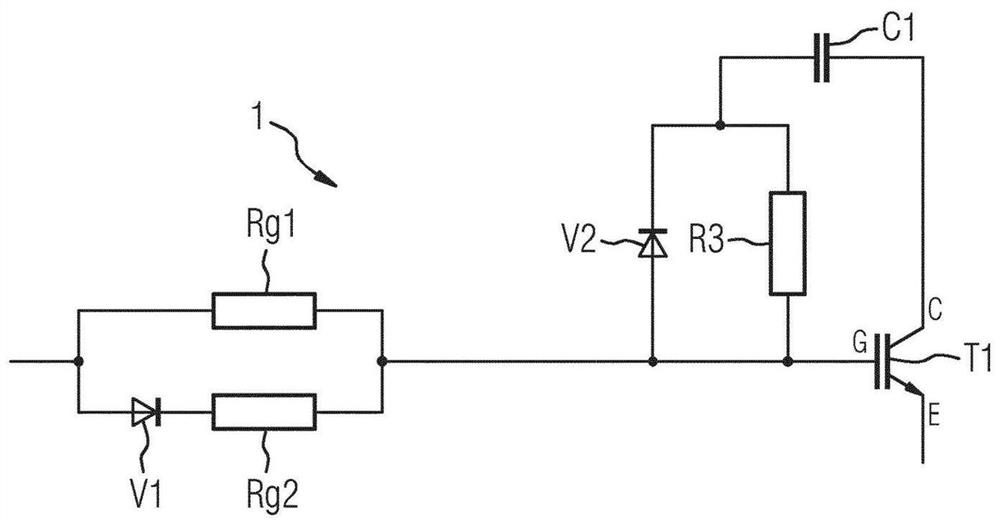

[0042] figure 2 A first embodiment of a circuit arrangement 1 of a semiconductor switch T1 is shown.

[0043] The semiconductor switch T1 is, for example, a field effect transistor, in particular a MOSFET or an IGBT, and has a gate G, a collector C and an emitter E. A capacitor C1 is arranged between the collector C and the gate G. This forms a gate wiring arrangement consisting of the first gate resistor Rg1 , the second gate resistor Rg2 and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com