Implementation method and system for vsetli instruction in risv_v vector instruction set

An implementation method and instruction set technology, applied in the field of CPU, can solve the problems of increased execution cycle, power consumption, low CPU execution efficiency, etc., and achieve the effect of reducing power consumption, reducing execution cycle, and reducing latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

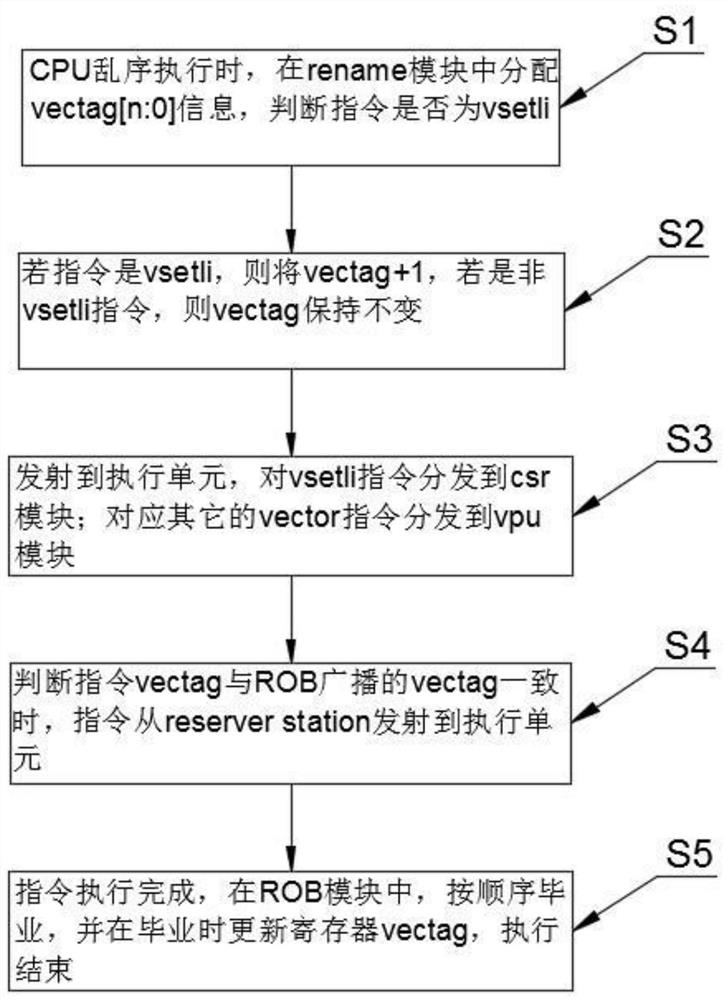

[0027] This embodiment discloses as figure 1 The implementation method of a risv_v vector instruction set vsetli instruction shown includes the following steps:

[0028] When the S1CPU executes out of order, allocate vectag[n:0] information in the rename module to determine whether the instruction is vsetli;

[0029] S2 If the instruction is vsetli, then vectag+1, if it is not a vsetli instruction, then the vectag remains unchanged;

[0030] S3 is sent to the execution unit, and the vsetli instruction is distributed to the csr module; corresponding to other vector instructions, it is distributed to the vpu module;

[0031] S4 judges that when the instruction vectag is consistent with the vectag broadcast by the ROB, the instruction is sent from the reserver station to the execution unit;

[0032] The execution of the S5 instruction is completed, and in the ROB module, graduations are performed sequentially, and the register vectag is updated at the time of graduation, and th...

Embodiment 2

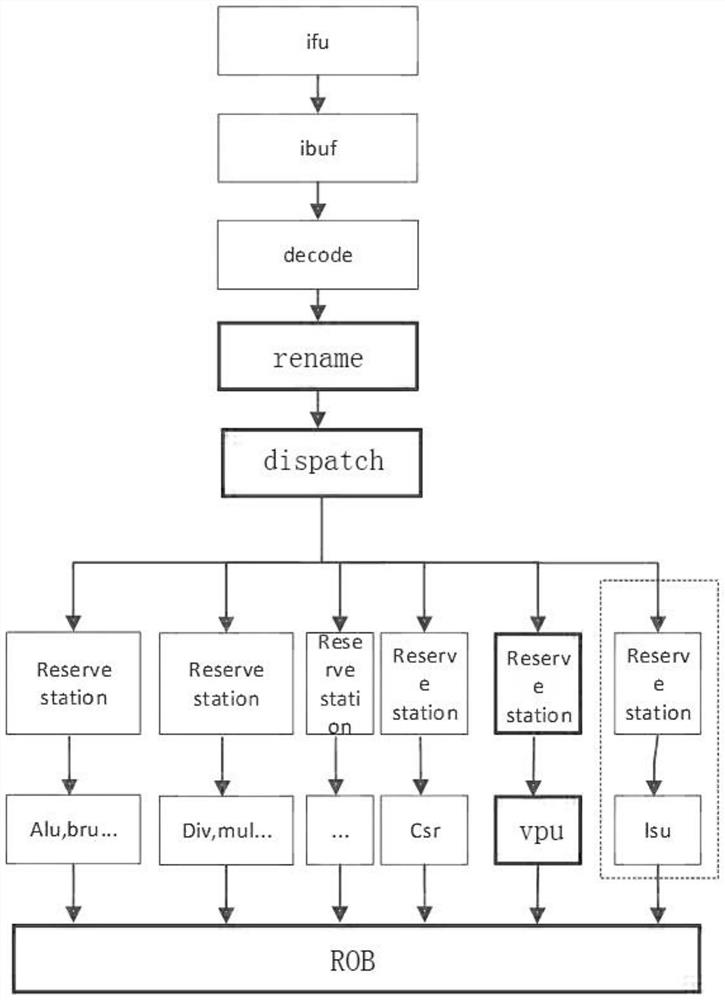

[0039] This embodiment refers to the out-of-order CPU, and its basic structure is as follows figure 2 As shown, this embodiment discloses an implementation system of a risv_v vector instruction set vsetli instruction, which includes four modules: rename, dispatch, ROB and vpu.

[0040] The rename module of this embodiment will allocate a vectag[n:0] information in the rename module. If it is vsetli, then vectag+1, and the vectag of the non-vsetli instruction remains unchanged. The purpose of doing this is for the vpu unit The command to be executed can be sent to the execution unit for execution only when the vectag of the command in the reserve station is consistent with the vectage broadcast by the csr.

[0041] The function of the dispatch module in this embodiment is to distribute the instructions to different datapaths according to the types of the instructions, and to distribute to the csr module corresponding to the vsetli instruction; to distribute to the vpu module c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com