Novel FPGA structure of power gating technology based on anti-fuse device control

A technology of power gating and anti-fuse, applied in CAD circuit design, special data processing applications, etc., can solve problems such as increasing chip cooling costs, power distribution costs, packaging costs, reducing chip market competitiveness, and affecting battery life. , to achieve the effect of improving chip competitiveness, improving chip market competitiveness, and increasing yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The present invention is explained and described in detail below by combining the drawings and embodiments. This example and the accompanying drawings are all illustrative descriptions, and should not be construed as limitations of this patent.

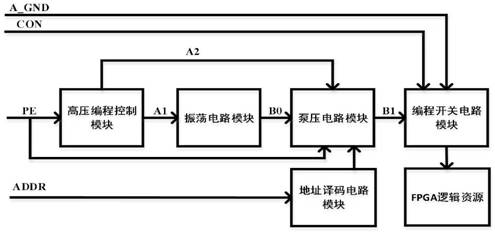

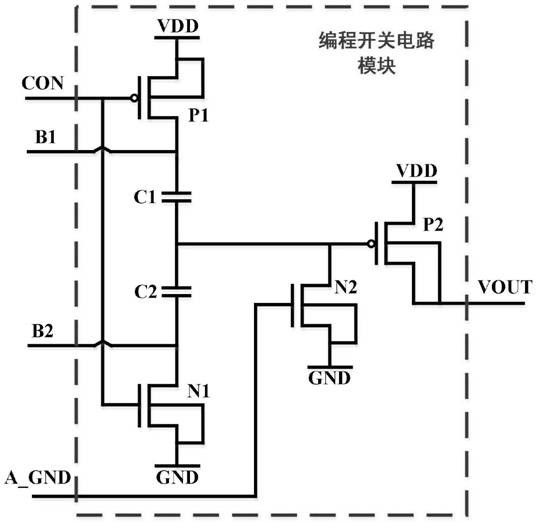

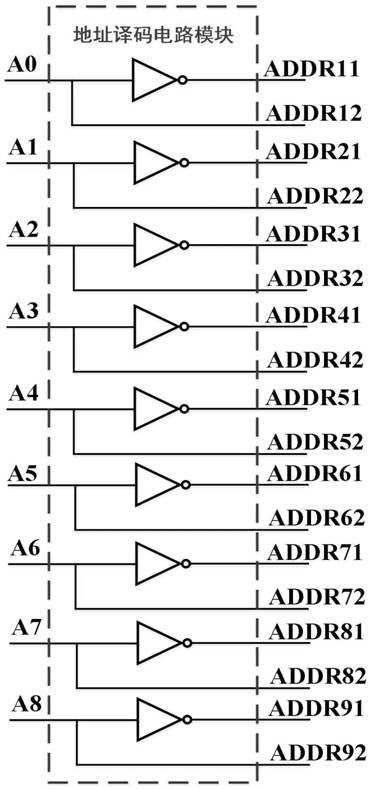

[0026] For the novel FPGA structure that the present invention designs, comprise address decoding circuit module, as image 3 As shown, it includes 9 inverters, and the output address of the decoding circuit is connected to the pumping circuit to control the high voltage output of the pumping circuit. Such as Figure 4 Shown is the overall implementation diagram of this design. Among them, the logic resources of the entire FPGA are divided into 9 power domains, namely BLOCK1, BLOCK2, BLOCK3, BLOCK4, BLOCK5, BLOCK6, BLOCK7, BLOCK8, and BLOCK9. The power on and off of each power domain is controlled by 9 programming switch circuits, and each programming switch circuit contains two anti-fuse devices to be programmed, which are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com